# IGBT のゲート電荷・ゲート電圧検出を用いた負荷短絡保護

吉田 秀太郎\* 濱田 航太 長谷川 一徳 大村 一郎 (九州工業大学)

Load Short-Circuit Protection with Detecting the Gate Voltage and Gate Charge of an IGBT Hidetarou Yoshida\*, Kota Hamada, Kazunori Hasegawa, Ichiro Omura (Kyushu Institute of Technology)

This paper proposes a new load short-circuit protection method for an IGBT. The proposed method is characterized by detecting not only gate charge but also gate voltage of the IGBT. This results in a shorter protection time, compared to the previous method that detects only the gate charge. A real-time monitoring system using an FPGA, AD converters, and DA converters, is used for the proposed protection method. Experimental results verify that the proposed method achieves a protection time of 390 ns, which is reduced by 68% compared to the previous method.

キーワード: 負荷短絡保護, ゲート電荷, ゲート電圧, IGBT (Load short-circuit protection, gate voltage, gate charge, IGBT)

## 1. まえがき

近年 IGBT(Insulated Gate Bipolar Transistor)をはじめとするパワーデバイスは、産業用だけでなく家庭用電化製品などの様々な製品に組み込まれている。今後もさらなる市場拡大が見込まれており、それに伴い信頼性の向上も求められている(1)。一方で変換器の高パワー密度化が進められ、IGBT の電流密度は増加する傾向にある。これは IGBT内部の電流集中に対する耐量の低減を招くため、保護回路をはじめ制御回路の高性能化が求められる。その一つに負荷短絡保護が注目されている。IGBT の負荷短絡保護において従来のセンス IGBT を用いた方法では保護速度に限界があると指摘されている。

本論文では、IGBT のゲート電圧とゲート電荷を検知することで負荷短絡保護を行う方法を提案する。提案法は従来のセンス IGBT による方法と比べて高速な保護が可能になる。

#### 2. IGBT の負荷短絡保護方法

#### 〈2·1〉高速負荷短絡保護の必要性

負荷短絡時は IGBT に過電流が流れ IGBT チップの温度が上昇する。IGBT の小型化はチップの熱容量低下につながるため、負荷短絡時における単位時間あたりの温度上昇が増大する。それゆえ高速な保護手法が求められている<sup>(2)</sup>。

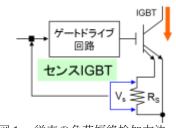

従来の保護方法はセンス IGBT とセンス抵抗  $R_s$  を利用している $^{(3)(4)}$ 。センス IGBT は, $\pm IGBT$  の保護を行うために

図1 従来の負荷短絡検知方法

Fig. 1. Conventional protection method.

共通のゲート及びコレクタとセンスエミッタを有するチップに埋め込まれた IGBT のことである。負荷短絡が起きるとコレクタ電流が増大し、その際のセンス抵抗電圧  $V_S$ も検出している。センス IGBT はノイズと負荷短絡による過電流を区別するために、短絡保護スピードが  $5 \mu s$  程度かかる。

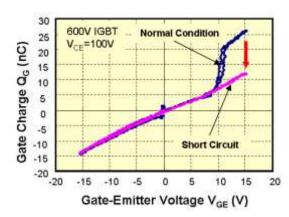

## 〈2·2〉ゲート電荷検出による負荷短絡検知方法

センス IGBT を用いた保護方法よりも高速な保護を実現する手法として、ゲート電荷を検知を用いた保護方法が提案されている $^{(5)(6)}$ 。図  $^2$  に IGBT の通常動作時及び負荷短絡時のゲート電荷  $^2$  を示す。ゲート電圧が  $^2$  15 $^2$  付近において、負荷短絡時のゲート電荷は通常動作時の電荷と比較して少ない。これは、IGBT の入力容量は電圧依存性がなくほぼ一定であるが、帰還容量はゲート - コレクタ間を流れる変位電流(ミラー効果)、及びゲート絶縁膜界面に蓄積されるホールによる寄生容量(ネガティブゲートキャパシタンス)によって変化するためである。いずれもコレクタ電圧に関係しており、負荷短絡時にコレクタ電圧が通常動作時に比

図 2 通常動作時と負荷短絡時のゲート電荷 Fig.2. Gate charge characteristics under normal condition and short-circuit condition.

べて増大することに起因している<sup>(7)</sup>。ゲート電荷の減少を検知することで保護を実現できるが、ゲート電荷を検出するタイミングはゲート電圧が 15V に達してからである。そのため、ゲート電圧が閾値電圧を超えてすぐに負荷短絡を検知することができない。

## 3. 提案する負荷短絡保護方法

#### 〈3·1〉ゲート電圧とゲート電荷検出による負荷短絡保護

文献(8)では負荷短絡時における IGBT のゲート電圧とゲート電荷の関係について論じている。本論文では、この関係を負荷短絡保護の高速化に応用する。

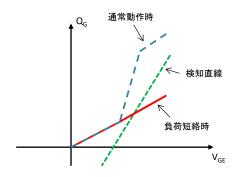

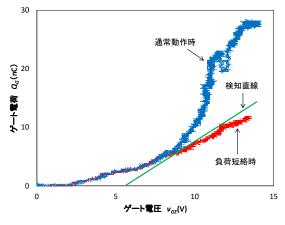

図 3 に通常動作時と負荷短絡時におけるゲート電圧とゲート電荷がなす軌跡が取る範囲を示す(®)。負荷短絡時のみ斜線で示す領域(Prohibited Area,以下,負荷短絡領域と称す。)を軌跡が通過する。ゲート電圧とゲート電荷の軌跡が負荷短絡領域に進入する点は、ゲート電圧が+15 V に達するより低い電圧である。これは、ゲート電圧が+15 V に立ち上がる前に負荷短絡を検知できることを意味し、負荷短絡保護の高速化を実現する。

提案法の実現にあたっては、ゲート電圧とゲート電荷を同時に測定し、その軌跡を求める必要性がある。つまり、複数パラメータを同時に検出するだけでなく、信号処理が必要である。本論文では FPGA (Field Programmable Gate Array) を用いたリアルタイムモニタリングシステムを導入する<sup>(9)</sup>。

## 〈3・2〉負荷短絡領域の決定

負荷短絡領域を理論的に求めるためには IGBT 内部の物性パラメータが既知である必要があり,実用上は理論的算出が困難である。本論文ではあらかじめ測定対象の IGBT の通常動作時・負荷短絡時におけるゲート電圧とゲート電荷の軌跡を測定し,実験的に負荷短絡領域を決定する。負荷短絡状態のみを検知するように領域を決定する直線を引いた。

図3 ゲート電荷・ゲート電圧の関係 (8)

Fig. 3. Relationship between the gate charge and gate voltage

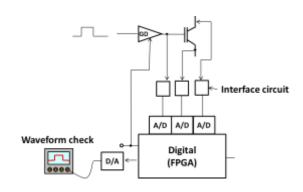

図4 リアルタイムモニタリングシステム<sup>(9)</sup> Fig.4. Real-time monitoring system.

## 4. 実験回路の構成

#### 〈4·1〉 リアルタイムモニタリングシステムの構成

図 4 にリアルタイムモニタリングのブロックダイアグラムを示す<sup>(9)</sup>。これは、複数の ADC (AD converter) を有し、IGBT の電圧、電流、温度などのパラメータをインターフェイス回路を通して検出できる。デジタル回路 (FPGA) からDAC (DA converter) を通し、アナログ信号に変化した波形をモニタリングできる。

本論文では、IGBT のゲート電圧とゲート電荷を検出する インターフェイス回路を用いた。インターフェイス回路か らの信号を ADC、FPGA、DAC を通り出力することで、リ アルタイムモニタリングを行う。

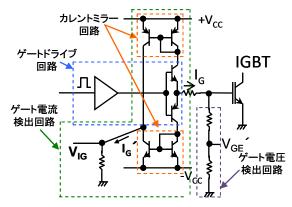

### 〈4·2〉 ゲート電圧・ゲート電流検出回路の構成

図 5 にゲート電圧・ゲート電流(電荷)の検出回路を示す。ゲート電流検出はゲートドライブ回路に 2 つのカレントミラー回路を付加することで実現している。ゲートドライブ回路を動作させるとゲート電流  $I_G$  と等しい値の電流  $I_G$  を出力する。 $I_G$  を検出用抵抗と ADC を通して FPGA に入力し,FPGA 内で積分することでゲート電荷  $Q_G$  を算出する。ゲート電圧  $V_{GE}$ は,分圧抵抗を通して検出する。

図5 ゲート電流・ゲート電圧検出回路の構成

Fig. 5. Configuration of gate charge and gate voltage detect.

Fig. 6. Experimental circuit.

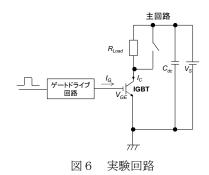

## 〈4・3〉 負荷短絡保護実験回路の構成

図 6 に実験回路を示す。IGBT は東芝製 10J303 を使用した。この IGBT は定格電圧 600 V,定格電流 10 A である。電源電圧  $V_s$ は 100V,コンデンサ  $C_{dc}$ は 780  $\mu$ F, $R_{Load}$ は 30 $\Omega$ で実験を行った。

### 5. 実験結果

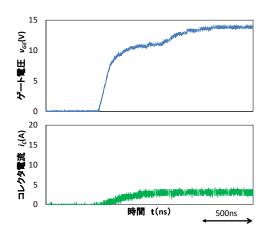

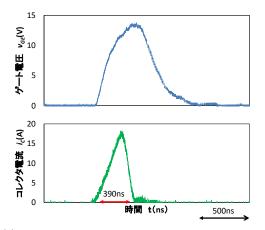

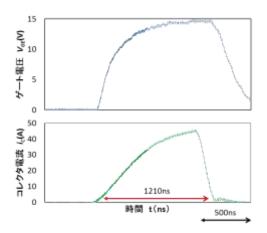

IGBT がオンしコレクタ電流が流れ始める瞬間を始点に、保護がかかり IGBT がオフし、コレクタ電流が零に達した瞬間を終点とした時間を保護時間と定義する。ただし、図に示すゲート電圧は ADC に入力し、FPGA でデジタルフィルタを通して DAC で出力した値を実際の波形に変換したものである。

図 7 に IGBT の通常動作時実験の波形を示す。通常動作時はコレクタ電流が IGBT の定格電流以内に収まっている。図 8 に負荷短絡時の実験波形を示す。ゲート電荷のみを検出する手法と、ゲート電荷とゲート電圧を検出する提案法との比較を行う。図 8(a)のゲート電荷のみの検出方法では、保護時間が 1210 ns であった。一方、図 9(b)に示す提案法の保護時間は 390 ns であった。

図 9 に提案法における通常動作時・負荷短絡時それぞれのゲート電圧とゲート電荷の軌跡を示す。通常動作時は短絡検知直線を常に上回る一方で、負荷短絡時は VGE > 9 V において負荷短絡検知直線を下回っている。

図 7 通常動作時のゲート電圧 vGE とコレクタ電流 icの 実験結果

Fig. 7.Experimental waveforms of the gate voltage  $v_{GE}$  and the collector current  $i_C$  under normal condition.

(a)Detecting the gate charge and the gate voltage.

(b) Detecting the gate charge.

図 8 負荷短絡時のゲート電圧  $v_{GE}$  とコレクタ電流  $i_{C}$  の実験結果

Fig. 8.Experimental waveforms of the gate voltage  $v_{GE}$  and the collector current  $i_C$  under load short-circuit condition.

図 9 ゲート電荷  $Q_G$ とゲート電圧  $v_{GE}$ の軌跡 Fig.9. Trajectory of the gate voltage  $v_{GE}$  and the gate charge.

### 6. まとめ

本論文では、ゲート電圧・ゲート電荷検出を利用した IGBT の負荷短絡保護手法を提案した。FPGA を用いたリア ルタイムモニタリングシステムを設計・制作し、負荷短絡 検知を実現した。

600 V 10 A 定格の IGBT を用いた実験により、負荷短絡の保護時間は 390 ns を実証した。これはゲート電荷のみ検出する手法に比べ、68% 短縮されたことを確認した。

## 文 献

- (1) R. Herzer, "Integrated gate driver circuit solutions", Proc. CIPS, pp1-1(2010)

- (2) I. Omura, Presentation at ECPE Workshop on Power Electronics Research & Technology Roadmaps -Copenhagen, Denmark (2007)

- (3) E.Motto, J.Donlon, S. Ming, K. Kuriaki, T. Iwagami, H. Kawafuji and T. Nakano ,"Large package transfer molded DIP-IPM", Proc. of IAS'08, pp.1-5 (2008)

- (4) M. Kudoh, Y. Hohi, S. Momota, T. Fujiwara and K. Sakurai, "Current sensing IGBT for future intelligent power module", Proc. of ISPSD 96, pp.303-306 (1996)

- (5)I. Omura, H. Ohashi and W. Fichtner, "IGBT negative gate capacitance and related instability effects", IEEE ED-letters, Vol. 18, No.12, pp.622-624 (1997)

- (6) K. Yuasa, S. Nakamichi and I. Omura, "Ultra high speed short circuit protection for IGBT with gate charge sensing", Proc. of ISPSD' 10, pp.37-40 (2010)

- (7) T. Tanimura, Y. Kazufumi, I. Omura, "Full Digital Short Circuit Protection for Advanced IGBTs", Proc. ISPSD, pp60-63(2011)

- (8) I. Omura, W. Fichtner, H. Ohashi, T. Ogura, H. Ninomiya, "SMICONDUCTOR DEVICE AND CONTROL METHOD THEREKF," USP 6,153,896(2000)

- (9)濱田航太・吉田秀太郎・大村一郎:「リアルタイムモニタ リング機能を持ったゲート駆動システムの構築」,電学 研究会資, EDD-13-062~081/SPC-13-124~143, pp17-20(2013)