# Review

# Paralleling of IGBT Power Semiconductor Devices and Reliability Issues

Ravi Nath Tripathi and Ichiro Omura

# Special Issue

Feature Papers in Semiconductor Devices

Edited by

Dr. Frédérique Ducroquet, Prof. Dr. Yi Gu, Prof. Dr. Jae-Hyung Jang, Prof. Dr. Tao Wang and

Dr. Hongtao Li

Review

# Paralleling of IGBT Power Semiconductor Devices and Reliability Issues

Ravi Nath Tripathi 1,\* and Ichiro Omura 2

- Next Generation Power Electronics Research Center, Kyushu Institute of Technology, Kitakyushu, Fukuoka 808-8196, Japan

- Life Science and System Engineering Kyushu Institute of Technology, Kitakyushu, Fukuoka 808-0196, Japan; omura@life.kyutech.ac.jp

- \* Correspondence: tripathi.ravi-nath639@mail.kyutech.ac.jp or ravi1989tripathi@gmail.com

**Abstract:** Paralleling of power semiconductor devices is inevitable considering their widespread application and exploitation in the extended horizon of these applications. However, paralleling of power semiconductor devices is prone to severe unbalancing corresponding to the non-idealities of device parameters, which leads to non-identical dynamic and static characteristics of the power devices, as well as the operating conditions and aging. Therefore, the currents are generally non-uniform and cause the derating of the system. This paper discusses and analyzes issues associated with the paralleling of IGBT power devices, which can evoke serious reliability issues. Furthermore, the paper examines the techniques and methodologies that have been proposed to reduce the issue of current unbalancing of parallel-connected power devices.

Keywords: power semiconductor device; paralleling; current unbalancing; reliability

Citation: Tripathi, R.N.; Omura, I.

Paralleling of IGBT Power

Semiconductor Devices and

Reliability Issues. *Electronics* 2023, 12,

3826. https://doi.org/10.3390/

electronics12183826

Academic Editors: Frédérique Ducroquet, Yi Gu, Jae-Hyung Jang, Tao Wang and Hongtao Li

Received: 29 June 2023 Revised: 29 August 2023 Accepted: 30 August 2023 Published: 10 September 2023

Copyright: © 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

# 1. Introduction

The Si-IGBT is one of the extensively developed and commercially mature power devices that has been used in various high-power applications [1]. With the advent of wide-band gap (WBG) devices, power device technology received a major boost in terms of fast switching and extended thermal capability. The operations of power devices are constrained by voltage blocking and current-carrying capability, which consequently limit the power-handling capability of devices and power electronic systems [2]. The applications in industrial motor drives, energy-wind power generation converters, solar photovoltaic power generation converters, and automobiles require power semiconductor modules within the 1200/1700 V class [3]. Si-IGBT and WBG SiC-MOSFET devices are the major players for the 1200/1700 V class power devices and modules. Based on the market trend and surveys, the Si-IGBT is expected to play a major role in the industrial motor and home appliance segment, and the SiC-MOSFET is expected to play a major role in automotive and energy segments [4,5]. However, the corresponding application segments require high-current power modules that exceed the limit of the maximum current rating of a single chip. The power device chip sizes are constrained by several factors that ultimately limit the rating of a single chip. A single Si-IGBT chip for the maximum voltage capability of 1200/1700 V is limited by the current rating of approximately 200 A [4,6]. Furthermore, applications of the medium voltage class, i.e., 3.3 kV, 4.5 kV, and 6.5 kV, for high-power industrial drives, have similar current limitation constraints [7–9].

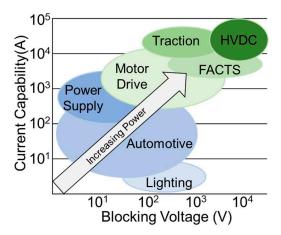

The paralleling of Si-IGBT chips/discrete devices is inevitable and extensively used for high-current applications, as shown in Figure 1, to realize the required current rating corresponding to the specific voltage class of the devices. Furthermore, paralleling provides compelling advantages: better performance-to-cost and cost-per-ampere ratios, flexible connection and operation, better thermal distribution, and high-power density [9–12]. The paralleling can be realized by different methods: paralleling of chips/discrete devices,

Electronics **2023**, 12, 3826 2 of 19

paralleling of half bridges/arms/legs, and paralleling of the modules [11,13]. The major problem and concern associated with the paralleling of power semiconductor devices is the current imbalance behavior due to non-idealities and system asymmetry factors [14,15]. The current imbalance behavior also varies corresponding to the paralleling technique and system configuration, which affects the asymmetry factors. The unbalancing can provoke major concerns, such as system derating and thermal derating due to non-uniform current sharing, which, in turn, may lead to stability, reliability, and failure issues of the devices, as well as the system [14,16].

**Figure 1.** Current capability requirement corresponding to blocking voltage for application of power semiconductor devices [10].

The current imbalance is categorized as static and dynamic current unbalancing. The static and dynamic behavior of paralleled IGBTs was discussed in [17] in 1990. The non-idealities and asymmetry affecting the static unbalancing are the on-state voltage  $(V_{CE,sat})$ /on-state resistance  $(R_{ds,on})$ , gate-emitter voltage  $(V_{GE})$ , junction temperature  $(T_j)$ , and total loop resistance. The non-idealities and asymmetry affecting the dynamic unbalancing are threshold voltage  $(V_{G,th})$ , gate signal propagation delay  $(t_{d,on};t_{d,off})$ , rise time and fall time of the gate signal  $(t_r;t_f)$ , gate resistance  $(R_G)$ , device parasitic capacitances, total power loop inductance, and gate loop inductance [18–21].

One rudimental means of minimizing unbalancing is the selection of the appropriate devices by ensuring the identical device parameters and other technical passive techniques [9,12,16]. However, this is just a preliminary step for the parallel power device system design and development because of the variable operating condition and environment, as well as the aging of the components. Different gate-driving strategies are implemented for parallel-connected power devices, which can be largely categorized as passive and active, to minimize the current imbalance. Passive techniques have the advantage of easy and low-cost implementation and may improve the current imbalance. However, optimizing the current sharing among the parallel-connected power devices is not possible. The active techniques provide improved current unbalancing to realize homogenous and optimized sharing by manipulating the gate signal corresponding to device performance and characteristics. However, the active control techniques address the implementation complexity and cost. The techniques for current balancing for parallel-connected devices are summarized as follows:

- 1. Device matching: Ensuring close matching of device parameters, such as  $R_{ds,on}$  and  $V_{G,th}$ , helps promote current sharing among parallel devices. Devices with similar characteristics are selected and grouped together to minimize differences in their current-carrying capabilities.

- 2. Symmetric system layout: In general, many device manufacturers provide application notes for the paralleling of the power devices in the design and adoption of the symmetric system layout to minimize the connection impedances in the system

Electronics **2023**, 12, 3826 3 of 19

layout. This is also crucial concerning overall system stability, and symmetric system layout is vital because it ensures the appropriate gate-driving loop and power circuit loop design.

- 3. Passive control: Device matching and symmetric system layout techniques are also a kind of passive control method; however, this method does not employ any additional components in the parallel-connected power device system. In passive control techniques, passive components, such as common mode choke or differential mode choke, are used with the parallel-connected device system to minimize the current imbalance.

- 4. Active control: The active control technique monitors the parallel devices to maintain equal current sharing. In general, these circuits sense the individual device parameters to estimate the current unbalancing, and correspondingly regulate the gate signal to minimize the current imbalance and achieve homogenous current sharing.

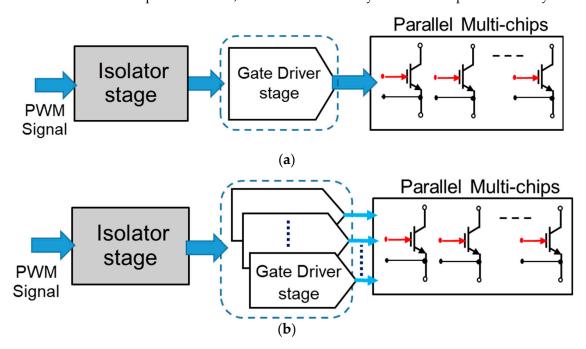

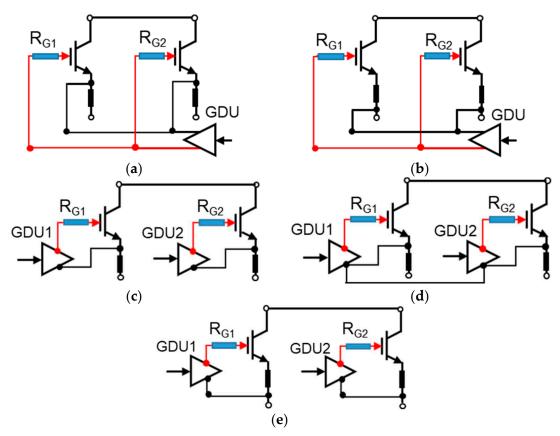

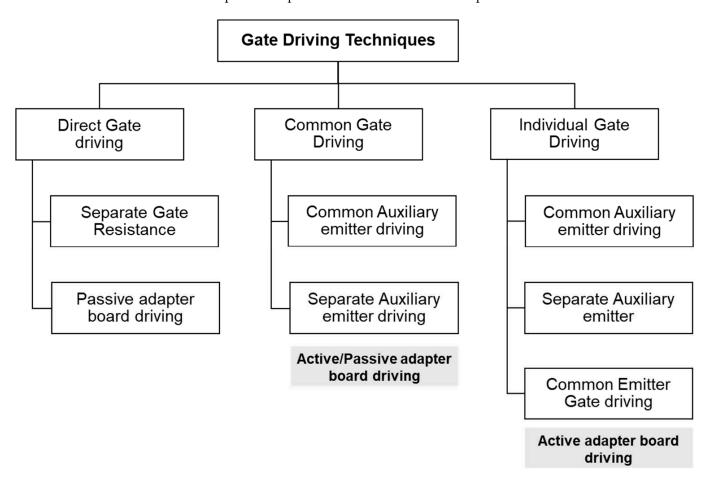

Furthermore, an appropriate gate-driving system is required for parallel-connected power devices when employing the appropriate current-balancing technique. The fundamental categorization of gate-driving techniques shown in Figure 2 is the common gate driver (CGD) and individual gate driver (IGD) [14,16]. In the common gate-driving technique, the parallel-connected power devices are driven by a single gate-driving unit, and in the individual gate-driving technique, the power devices are driven by a corresponding separate gate drive unit (GDU) Figure 2. The gate-driving techniques possess their own advantages and disadvantages based on the GDU configuration, such as common emitters or separate emitters, and common auxiliary emitters or separate auxiliary emitters.

**Figure 2.** Gate-driving technique for parallel-connected power devices: (a) common gate driving (b) individual gate driving.

This paper discusses and investigates the gate-driving techniques implemented for parallel-connected power semiconductor devices. Further, it examines the study of the influence of parameters on the current imbalance of the devices in terms of device physics. Furthermore, the gate-driving techniques that have been used for the parallel-connected IGBT power devices are investigated and discussed considering passive and active current-balancing techniques that have been implemented to achieve improved/optimized current balancing. The paper is configured as follows: Section 2 presents the investigation into and study of the influence of system parameters on parallel-connected IGBT power devices. Section 3 examines the gate-driving techniques with active and passive current-balancing techniques, and Section 4 provides the inference in the form of a discussion.

Electronics **2023**, 12, 3826 4 of 19

# 2. Influence of System Parameters

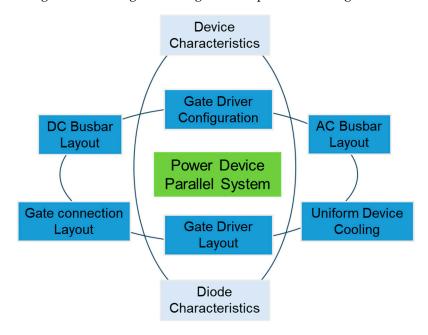

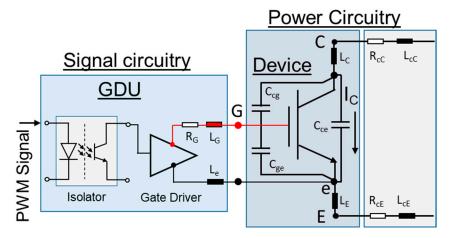

The components of a parallel-connected system have direct, indirect, and cumulative influences on its performance, such as dynamic current sharing, static current sharing, unwanted junction temperature swing of the devices, oscillations, and frequent operation in the safe operating area (SOA) limit region. The system components influencing parallel-connected power devices are represented in Figure 3. The parallel-connected device system encompasses the device parasitic parameters, GDU parameters, and connection layout parameters, consisting of stray inductances and resistances. A schematic circuit diagram of a single device and gate-driving unit is represented in Figure 4.

**Figure 3.** System components influencing the performance of parallel-connected power semiconductor devices [14,15,22,23].

**Figure 4.** Schematic diagram of an IGBT and gate-driving system including the device parasitic, stray inductance, and capacitance of the connection layout.

# 2.1. Device Parameters

In this subsection, the co-relations of the device parameters are discussed corresponding to dynamic current unbalancing and static current unbalancing. The transfer characteristics of the device are as follows: the collector current ( $I_C$ ) relates to  $V_{GE}$ , which is associated with the dynamic current balancing considering threshold voltage. The fundamental reason for the difference in device characteristics regarding the device parameters is

Electronics **2023**, 12, 3826 5 of 19

the fabrication process, in which it is extremely difficult to eliminate variation at different steps. The gate oxide layer thickness affects  $V_{G,th}$ , and a thicker oxide layer ultimately results in a higher  $V_{G,th}$  for the conduction [24]. In addition, similar to the gate oxide thickness, the p-base doping concentration influences  $V_{G,th}$  and an increase in doping ultimately increases the  $V_{G,th}$  required for conduction [24]. Threshold voltage affects the dynamic current sharing during turn-on and does not have a significant role during turn-off considering the difference between the negative gate drive voltage and  $V_{G,th}$  [25]. The device with lower  $V_{G,th}$  turns on earlier, resulting in current imbalance.

The switching characteristic of the device is related to the capacitances formed between the gate and the insulating silicon oxide layer [26]. The gate-emitter capacitance and Miller capacitance of IGBT devices mainly impact the dynamic current imbalance in parallel [27]. The equivalent input capacitance comprising the gate-emitter capacitance affects the turn-on delay; a lower input capacitance means the device turns on faster and results in current imbalance. The common gate resistance in a parallel-connected IGBT system results in the limit of the increase in  $V_{\rm GE}$  for slower IGBTs in the Miller region, thereby resulting in current imbalance [27].

Similarly, the output characteristic, also termed the static characteristic of the device, provides the relation between the device current and on-state voltage, i.e., collector current ( $I_C$ ) and  $V_{CE\,(sat)}$ , respectively, for an IGBT. The gate oxide thickness and p-base doping also influence  $V_{CE\,(sat)}$ ; higher gate oxide thickness and p-base doping concentration results in increased  $V_{CE\,(sat)}$ , and consequently higher  $R_{ds,on}$  for the corresponding IGBT device and less static current under the paralleled device operation [24]. Furthermore, the forward voltage ( $V_F$ ) of the diode and  $V_{CE\,(sat)}$  in combination as a device parameter impacts the current sharing of the parallel-connected devices [25].

The effect of the device parameters, rate of change in the current (di/dt) and voltage (dv/dt), is discussed in [25] considering their major impact during turn-off. The device having higher di/dt will have an overshoot in current during turn-on, and during turn-off the IGBT having higher dv/dt reaches the dc-link voltage earlier than in the counterpart IGBT, thus leading to the high current overshoot in the counterpart IGBT. In [25], a selection criterion for IGBT device parameters is proposed considering di/dt and dv/dt.

# 2.2. Gate-Driving Parameters

The gate-driving layout determines the gate current path, and an asymmetric gate-driving layout results in parallel-connected power devices due to the asymmetric gate current path [9]. The gate-driving parameters in conjunction with the gate-driving layout affect the gate resistance ( $R_G$ ), gate loop emitter inductance ( $L_e$ ), gate-emitter voltage ( $V_{GE}$ ), gate signal propagation delay ( $t_{d,on}$ ;  $t_{d,off}$ ), and rise time and fall time of gate signal ( $t_r$ ;  $t_f$ ), consequently leading to current imbalances among the parallel-connected power devices [19].

One of the vital parameters of gate driving is  $R_G$ , which governs multiple factors. The use of individual gate resistances is recommended to reduce the potential of oscillations and the effect of the Miller region [16,27,28]. The effect of unequal  $R_G$  on the current imbalance is demonstrated in [29] considering the different cases of  $R_G$  and demonstrating the linear unbalance rate corresponding to increase in variation between  $R_G$ . However, there is a sudden non-linear increase in current imbalance after resistance difference higher than 30%. The gate resistor selection is discussed in [27,30], which mentions its effect on the following parameters: turn-on and turn-off times, switching losses, dv/dt across the collector-emitter, di/dt, and EMI due to switching. An increase in  $R_G$  increases turn-on and turn-off times, and consequently decreases dv/dt, di/dt, and EMI, but increases switching losses.

The current imbalance during turn-off is discussed in [31] considering a change in  $R_G$  for a parallel-connected IGBT device operating with equal  $R_G$ . Although parallel-connected devices operate with equal gate resistance, an increase in gate resistance results in a significant change in current imbalance during turn-off. This is due to the change in the turn-off delay time difference corresponding to an increase in  $R_G$ .

Electronics **2023**, 12, 3826 6 of 19

The current imbalance during turn-off due to unequal  $R_G$ ,  $t_{d,off}$ , and  $L_e$  was demonstrated in [8] using TCAD simulation for parallel-connected IGBT devices. The unequal  $R_G$  results in a significant current imbalance. Further,  $t_{d,off}$  and  $L_e$  produce significant current imbalance. In [8], the impact of the unequal  $R_G$  demonstrated during turn-on results in a severe current unbalance; however, the impact of the unequal  $L_e$  demonstrated during turn-on does not produce a significant current imbalance.

The current mismatch phenomenon during turn-off is mentioned in [32] corresponding to fulfillment of three conditions, given as follows: the individual gate resistances are used for the parallel-connected field-stop IGBTs,  $V_{GE}$  values are near  $V_{G,th}$ , and IGBT reaches the field-stop layer before reaching the DC link voltage, in addition to the occurrence of a self-turn-off process and parasitic turn-on effect before reaching the DC link voltage. The DC link influence is mentioned in [26], in which the current redistribution during turn-off stops as soon as the voltage across the collector-emitter ( $V_{CE}$ ) regains the DC link voltage. A similar kind of mechanism was also described for a single IGBT case as a negative gate capacitance effect in [25].

The reason for the turn-off current imbalance due to gate-driving parameters is the occurrence of the distinctive  $V_{CE}$  slope and current redistribution among the paralleled IGBT devices [8,19,31]. The current imbalance phenomenon during turn-off corresponding to unequal  $V_{CE}$  for parallel-connected devices is discussed extensively in [26]. During turn-off of the devices,  $V_{GE}$  reaches the Miller plateau and  $V_{CE}$  rises significantly. However, different slopes, together with unequal stray collector inductance ( $I_{C}$ ) and/or emitter inductance ( $I_{E}$ ), lead to the current redistribution between the parallel-connected power devices [8,19]. This results in a serious cumulative effect as the redistribution of current affects the  $I_{CE}$  of IGBTs, which further leads to a combined cumulative effect, resulting in a change in  $I_{CE}$  slopes [19].

$V_{GE}$  impacts are discussed for dynamic current unbalancing and static current unbalancing in [11,14]. The difference in  $V_{GE}$  of the parallel-connected devices results in the unequal static current sharing [11] and unequal dynamic current sharing during turnon [14]. The difference of 0.5 V for  $V_{GE}$  is used in [14] to demonstrate the effect during turn-on; however, there is no significant impact on current sharing during turn-off.

# 2.3. System Layout and Interconnections

The stray inductance and resistance due to the load connection layout and parallel device interconnection layout can cause severe current imbalance. The stray emitter and collector inductance, ( $L_E$ ,  $L_{cE}$ ) and ( $L_C$ ,  $L_{cC}$ ), respectively, are almost unaffected by the frequency; however, the stray resistance ( $R_{cC}$ ,  $R_{cE}$ ) significantly increases corresponding to frequency due to the skin and proximity effects occurring in the conductors [33]. Therefore, the stray resistance and inductance have a dominant effect on current imbalance during dynamic current sharing among the parallel-connected power devices. Furthermore, the stray resistance impacts the current imbalance during static current sharing. It is mentioned that the significant changes in  $R_{cC}$ ,  $R_{cE}$  have a major impact on current imbalance during switching turn-on and, as a result, at higher operating frequencies, the total power loss increases significantly [33].

The effect of  $L_E$  and  $L_C$  is thoroughly investigated in [8,26] during dynamic current sharing. The current unbalancing demonstrated for two parallel-connected devices considering unequal  $L_E$  and  $L_C$  is examined in [8]; a non-identical current slope during turn-on is observed because of the unequal displacement current through gate oxide. The difference in  $L_C$  has a significantly dominant effect compared to  $L_E$  during turn-on; however, differences in unequal  $L_E$  and  $L_C$  are not mentioned quantitatively in [8]. In [19], the current unbalancing is demonstrated due to the difference in  $L_C$  during turn-off, and it is mentioned that the unequal  $L_E$  values have the same impact on the current redistribution. However, the study in [26] also includes the busbar inductance and unequal  $R_C$  condition.

In [31], the impact of  $L_E$  is elucidated considering the influence on the gate current path with equal  $R_G$  during turn-off; an increase in  $L_E$  consequently increases  $t_{d,off}$ . The

Electronics **2023**, 12, 3826 7 of 19

effect of  $L_C$  is also demonstrated and  $t_{d,off}$  increases corresponding to the increase in  $L_C$ , and a current redistribution occurs as mentioned in [19]. However, as discussed in [31], current redistribution, and consequently current imbalance, is improved with the higher  $L_C$  value because of the slower current redistribution.

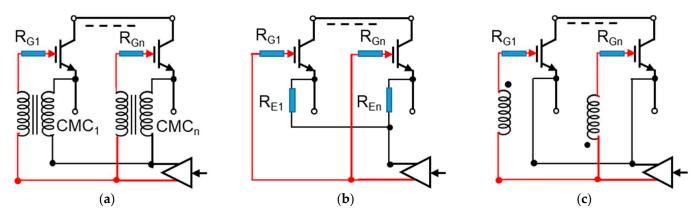

In [25], three different gate-driving strategies (shown in Figure 5) are compared considering a common gate driver with a common emitter, an individual gate driver with independent driving, and an individual gate driver with a common auxiliary emitter for turn-on and turn-off conditions. This results in a different gate-driving layout. This demonstrates that a single driver/common emitter has almost the same performance as individual gate driving with an auxiliary common emitter and individual gate driving with independent driving, which lead to static current unbalance. The effect of a common auxiliary emitter considering Le >> LE is also demonstrated in [31], which confirms that a common auxiliary emitter configuration helps improve the current imbalance compared to a common emitter configuration. This demonstrates that a single gate driver with a common auxiliary emitter has better current balancing during turn-off compared to the common gate driver with a common mode inductance. Commutation path inductance (L<sub>S</sub>) is also discussed in [31], which demonstrates the effect on the current redistribution phenomenon. This paper mentioned that there is no influence of an increase in  $L_S$  (changed from 10 nH to 90 nH) on current redistribution; however, it impacts the voltage during turn-off and results in voltage overshoot.

Figure 5. Layout configuration of the gate driver for parallel devices: (a) common auxiliary emitter CGD; (b) common emitter CGD; (c) independent auxiliary emitter IGD; (d) common auxiliary emitter IGD; (e) common emitter IGD.

The system parameters for the parallel-connected IGBT devices considering co-relation factors of device characteristics, such as transfer characteristics, output characteristics, and switching characteristics, are summarized in Table 1. The summary of related references corresponding to system parameters is also given in Table 1.

Electronics **2023**, 12, 3826 8 of 19

| System Parameters                                                                    | Co-Relating Factors                                                                                                                         | References    |  |

|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|---------------|--|

| Threshold voltage (V <sub>G,th</sub> )                                               | Gate oxide thickness, transfer characteristics, dynamic current sharing                                                                     | [11,14,24]    |  |

| On-state saturation voltage ( $V_{CE,sat}$ )/on-state resistance ( $R_{DS,on}$ )     | Gate oxide thickness, p-base doping, output characteristic, static current sharing, dynamic current sharing                                 | [11,14,24,25] |  |

| Parasitic capacitances                                                               | Input capacitance, output capacitance, switching characteristics, Miller region, dynamic current sharing, current redistribution phenomenon | [26,27,32]    |  |

| Rate of change in current (di/dt) and voltage (dv/dt)                                | Switching characteristics, dynamic current sharing                                                                                          | [25]          |  |

| Gate resistance $(R_G)$                                                              | Switching characteristics, dynamic current sharing, current redistribution phenomenon                                                       | [8,9,16,28–31 |  |

| Gate loop emitter inductance (L <sub>e</sub> )                                       | Switching characteristics, dynamic current sharing                                                                                          | [8,18–21]     |  |

| Gate-emitter voltage ( $V_{GE}$ )                                                    | static current sharing                                                                                                                      | [18–21,26,31] |  |

| Gate signal propagation delay (t <sub>d,on</sub> ; t <sub>d,off</sub> )              | Switching characteristics, dynamic current sharing                                                                                          | [8,18-21]     |  |

| Stray emitter and collector inductance ( $L_E$ , $L_{cE}$ ) and ( $L_C$ , $L_{cC}$ ) | Switching characteristics, dynamic current sharing, current redistribution phenomenon                                                       | [25,26,31,33] |  |

| Stray resistance ( $R_{cC}$ , $R_{cE}$ )                                             | Switching characteristics, dynamic as well as static current sharing                                                                        | [33]          |  |

| Commutation path inductance (L <sub>S</sub> )                                        | Dynamic current sharing                                                                                                                     | [31]          |  |

**Table 1.** Summary of parallel-connected IGBT system parameters.

# 3. Gate-Driving Techniques

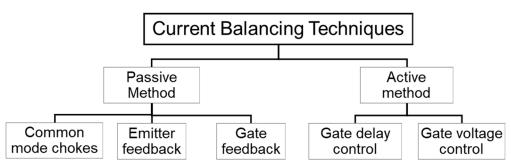

Active and passive methods, as shown in Figure 6, are adopted to minimize the current unbalancing or optimize the current sharing amongst the parallel-connected power devices. This is required considering the maximum junction temperature of a particular chip to retain thermal stability and avoid thermal runway, and to ensure the operation of the parallel-connected devices within SOA corresponding to the SOA limit of the devices. In a parallel-connected system, if a device frequently experiences a higher temperature swing and operation near the SOA limit, the device will experience accelerated aging and lifetime issues [16].

Figure 6. Current-balancing techniques of the parallel-connected IGBT power devices.

One conventional approach to achieving the operating criterion considering thermal stability and the SOA limit is derating the chips/power modules [16]. This method is the easiest and does not require sophisticated or complex gate-driving techniques. In many cases, the device manufacturers provide the application note for an analytical explanation of the derating factors regarding the parallel-connected modules. The application notes [22,23,34–36] of different manufacturers have detailed information regarding the paralleling requirement and derating factors. However, derating the chips/modules is not a current-balancing technique; therefore, the parallel system capability cannot be exploited in terms of system performance, system stability, or cost. The analysis of derating factors is a critical and

Electronics **2023**, 12, 3826 9 of 19

tedious procedure in the evaluation of the appropriate derating factor considering static sharing, dynamic sharing, thermal stability, and the SOA limit based on various influential factors and parameters [37].

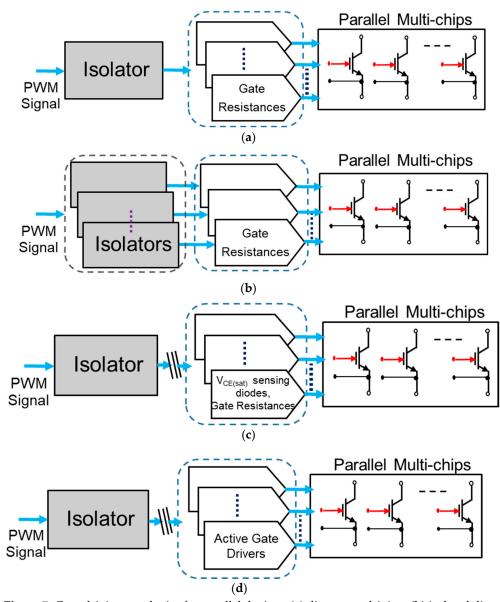

## 3.1. Gate-Driving Topologies for Parallel-Connected Power Devices

A general gate-driving strategy is discussed in [9] in a study of the impact of corresponding gate-driving strategies on the paralleling of IGBT devices. The gate-driving strategies are categorized as direct gate driving, isolated gate driving, passive adapter board driving, and active adapter board driving. A schematic diagram of gate-driving techniques discussed in [9] is represented in Figure 7. As summarized in [9], direct gate driving, and passive adaptor board driving are low-cost and low complexity implementations and are highly sensitive to layout/wire length and emitter loop current. Active adapter boards have a low cost with medium complexity for implementation, have better emitter loop current performance, and are less sensitive to layout/wire length. Finally, the isolated driver has high cost and complexity, is less sensitive to layout/wire length, and is best for emitter loop current response.

**Figure 7.** Gate-driving topologies for parallel devices: (a) direct gate driving; (b) isolated direct gate driving; (c) passive adapter board driving; (d) active adapter board driving.

### 3.2. Passive Gate-Driving Technique for Current Imbalance

Passive gate-driving techniques are a lucrative option to achieve improved current sharing for parallel-connected power devices. A detailed investigation and study were performed in [8] considering the current imbalance cause and effect, as well as the impact of passive measures on the corresponding current imbalances. The passive measure technique is categorized in three parts, as shown in Figure 8: the common mode choke technique (without feedback), emitter feedback, and gate current feedback technique.

**Figure 8.** Schematic diagram of passive gate-driving technique for parallel-connected power devices: (a) common mode chokes; (b) emitter feedback through common auxiliary emitter; and (c) gate current feedback using differential mode chokes.

#### 3.2.1. Common Mode Chokes

The common mode chokes are investigated in [9] using passive adapter board gate driving and the CGD technique under the conditions of an asymmetric gate drive length and asymmetric busbar configuration. The common mode choke significantly worsens the dynamic current imbalance for an asymmetric gate drive length. However, the common mode choke improves the dynamic current imbalance for an asymmetric busbar configuration.

The impact of common mode (CM) chokes on the CGD technique is discussed in [14], and is described as a patented technology from ABB. The current sharing is demonstrated for the two parallel-connected devices considering unequal  $L_E$  values. A similar test condition without CM chokes results in current imbalance during turn-on and during static current sharing; there is almost no impact during turn-off. The inclusion of CM chokes eliminates the current unbalancing during turn-on and in static conditions.

#### 3.2.2. Emitter Feedback

The effect of emitter feedback caused by the emitter inductance through a common auxiliary emitter is investigated in [9] using passive adapter board gate driving under the conditions of an asymmetric gate drive length and asymmetric busbar configuration. The emitter feedback provides improved dynamic current sharing with an asymmetric gate drive length, as well as an asymmetric busbar configuration. However, emitter feedback is less effective in the case of the asymmetric busbar configuration compared to an asymmetric gate drive length.

Similar emitter feedback is investigated in detail in [8] considering the difference in gate resistors, the difference in turn-off delay times, the difference in gate inductances, and the combined effect of the difference in emitter inductance and the difference in turn-off delay times during turn-off for two parallel-connected power devices with a CGD configuration. This also considers the difference in turn-off delay times due to gate-emitter capacitance ( $C_{GE}$ ) and due to  $V_{G,th}$ . The emitter feedback technique can reduce current imbalances for all the test conditions.

Furthermore, emitter feedback is investigated for turn-on conditions considering the difference in gate resistors,  $C_{GE}$ ,  $V_{G,th}$ ,  $L_e$ ,  $L_E$ , and  $L_C$ . The current imbalance is improved

Electronics **2023**, 12, 3826 11 of 19

for the turn-on condition for all the cases except the difference in the emitter inductance condition. The current imbalance worsens in the case of the difference in the emitter inductance condition for the emitter feedback.

### 3.2.3. Differential Choke-Based Gate Feedback

The effect of differential choke-based gate feedback is assessed in [8]. This considers the turn-off case with a difference in turn-off delay times, a difference in gate inductances, and the combined effect of a difference in emitter inductance and a difference in turn-off delay times; a difference in the turn-off delay times due to  $C_{GE}$  and  $V_{G,th}$ ; and the turn-on case with a difference in gate resistors,  $C_{GE}$ ,  $V_{G,th}$ ,  $L_e$ ,  $L_E$ , and  $L_C$ . In the turn-off case, the gate feedback method can reduce current imbalances, except the difference in turn-off delay times due to  $C_{GE}$ , and the current imbalance worsens for the case of  $C_{GE}$ . In the case of turn-on, the current imbalance is reduced for the difference in gate resistors and gate inductances; however, the current imbalance almost remains the same for  $L_E$  and  $V_{G,th}$ ; the current imbalance worsens for the case of  $L_C$  and  $C_{GE}$ .

The comparative performance of the passive gate driving techniques is summarized in Table 2. The performance is summarized considering the study and investigation discussed in [8,9,14].

| Imbalance Parameters                           | Transient | Common Mode Chokes | Emitter Feedback | Gate Feedback |

|------------------------------------------------|-----------|--------------------|------------------|---------------|

| Asymmetric Gate drive length $(L_G)$           | on        | Increased          | Reduced          | Reduced       |

|                                                | off       | Increased          | Reduced          | Reduced       |

| Asymmetric bus bar length $(L_S)$              | on        | Reduced            | Reduced          |               |

|                                                | off       | Reduced            | No change        |               |

| Gate Resistance (R <sub>G</sub> )              | on        | Increased          | Reduced          | Reduced       |

|                                                | off       | Increased          | Reduced          | Reduced       |

| Threshold voltage $(V_{G, \operatorname{th}})$ | on        |                    | Reduced          | No change     |

|                                                | off       |                    | Reduced          | Reduced       |

| Gate-emitter capacitance ( $C_{GE}$ )          | on        |                    | Reduced          | Increased     |

|                                                | off       |                    | Reduced          | Increased     |

| Emitter Inductance (L <sub>E</sub> )           | on        | Reduced            | increased        | No change     |

|                                                | off       |                    | reduced          |               |

**Table 2.** Comparison of common mode chokes, emitter, and gate feedbacks passive methods.

# 3.3. Active Gate-Driving Control Techniques

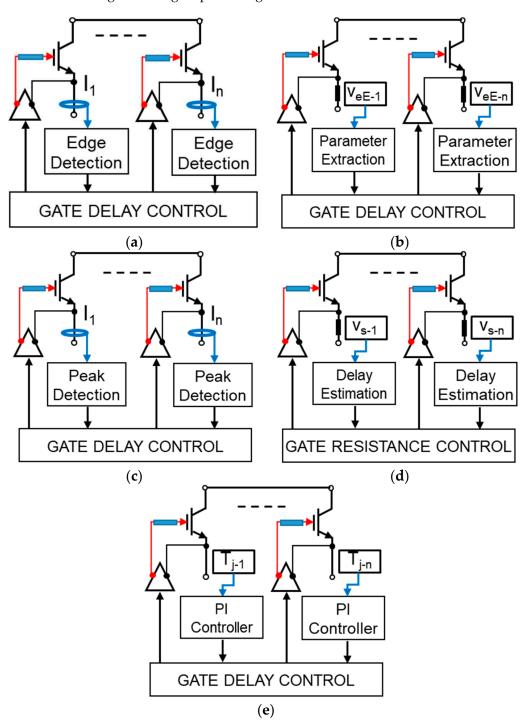

The active gate-driving control techniques are employed to minimize the current imbalance and/or to achieve optimized current sharing, as shown in Figure 9 for parallel collected devices/modules. The current-balancing techniques are classified in [38] as derating, active gate control, and impedance balancing. Further, active gate-driving control is categorized as gate delay control and the average current method. The derating method is a means of maintaining the thermal stability and SOA operation of the parallel-connected chips/modules by reducing the rated operating limit of the chips/modules; this method is not capable of providing current balancing or improving current imbalance. The active gate control method can be an appropriate solution; however, implementation complexity is an associated issue. The active gate control methods are summarized in Figure 8 using a schematic representation of the techniques.

# 3.3.1. Gate Delay Control

The gate delay control technique is presented in [39] for the dynamic current balancing during turn-on and turn-off. The results are demonstrated for four parallel connected

IGBT devices through gate delay control, which achieves improved current sharing. The operating principle is presented for the gate delay control based on calculation of the current error using central signal processing or a master–slave control method.

**Figure 9.** Schematic diagram of active gate-driving control techniques for dynamic current balancing of parallel—connected power devices: (a) current edge detection; (b) auxiliary emitter and emitter voltage measurement; (c) current peak detection; (d) TSEP-based junction temperature measurement; (e) gate voltage and delay control using dynamic gate resistance.

The active gate delay control is proposed and discussed in [40] based on the edge detection of currents with peak current monitoring of parallel-connected power devices. The rise-and-fall time controller is based on the detected rising and falling edges, and gate

signals are manipulated to provide the required delay and to achieve current balancing. A distributed non-centralized control is presented in [41] based on the edge detection technique presented in [40]; to implement the distributed non-centralized control, the master–slave technique and daisy chain technique are used to determine the appropriate delay of the gate signals and are finally experimentally evaluated for four parallel-connected IGBT power devices.

The delay time compensation principle is presented in [42–45] considering the voltage measurement between the emitter and auxiliary emitter ( $V_{eE}$ ). The measurement of  $V_{eE}$  corresponding to individual devices connected in parallel is further used for the extraction of delay time information. This delay time information is further used for the compensation algorithm to determine the appropriate delay time for the gate signal corresponding to individual devices and generation of the manipulated gate signal. The method is examined for the two parallel-connected power devices in [42] to achieve active current balancing and evaluated for the three parallel-connected devices; in addition, the half bridge inverter configuration is examined in [45]. This demonstrates the balanced current sharing during turn-off after employing this technique, and improved current imbalance during turn-on as well.

The dynamic current peak detection-based active delay compensation method is presented in [46]. The peak current of the parallel-connected devices is detected, and active gate delay compensation control is demonstrated for two IGBT devices using fully digital feedback control in FPGA. The efficacy of the method is demonstrated for four parallel connected IGBT devices in [47] with a current imbalance limit to achieve current optimization. Further, this dynamic peak current detection implementation is demonstrated using a PCB Rogowski current sensor in [48]. This approach is suitable for system miniaturization considering the characteristic of the PCB Rogowski current sensor, providing current measurement in the form of peak overshoots for parallel-connected power devices. The appropriateness of this method is demonstrated for four parallel connected IGBT devices, and current measurement accuracy is verified using a Pearson current probe.

Another active gate delay control technique is presented in [49] using the junction temperature measurement of the power devices. The online junction temperature of corresponding devices is measured using the thermo-sensitive electric parameter (TSEP) method, which is integrated with a gate-driving unit to estimate the junction temperature of the individual devices. The internal gate resistance is a TSEP considering its dependence on the chip temperature. However, an accurate calibration mechanism is required to translate the voltage measurement across the internal gate resistor into temperature estimation and based on the temperature estimation of the devices, gate signals are manipulated to incorporate an appropriate delay and to equalize the junction temperature of the parallel-connected devices.

#### 3.3.2. Gate Voltage Control

A gate voltage control method is mentioned in [39] for the static current balancing of the parallel IGBT devices considering the negative temperature coefficient. The appropriate adjustment of the gate voltage can provide improved static current sharing. The method of gate voltage control based on the current averaging method is presented in [50] and balanced static current sharing is demonstrated for two parallel connected IGBTs. Furthermore, the gate voltage control method based on the current average calculation and current cross-reference is presented in [12], and results are demonstrated for two independent parallel-connected transistors and for the boost converter implementation.

The device current slope can be controlled via dynamic gate-emitter voltage control of the corresponding device [51] and dynamic current balancing can be realized. The dynamic adjustment of  $V_{GE}$  can be realized through dynamic  $R_{G}$  control. The dynamic  $R_{G}$  control is presented and implemented in [52,53] for parallel-connected IGBTs to realize dynamic  $V_{GE}$  adjustment. Furthermore, turn-on and turn-off delay time parameters can also be controlled by dynamic resistance control.

#### 4. Discussion

The various components that influence the performance of the parallel-connected power device system are summarized in Figure 3. The power semiconductor device characteristics, diode characteristics, gate driver configuration, and gate driver layout are one set of influences, and DC busbar layout, AC busbar layout, gate connection layout, and device cooling are another set, which, in combination, can cause severe issues in terms of reliability, thermal stability/thermal runaway, unwanted oscillations, and violation of safe operating area (SOA) operation.

# 4.1. Influence of Parameters and Passive Gate Control

The influence of parameters is thoroughly studied and investigated in Section 2. The turn-on and turn-off phenomena are significantly different for the IGBT devices; therefore, the effects of parameters and gate control techniques may possess unique impacts. The case of different emitter inductances for dynamic current imbalance is improved during turn-off via the passive gate control technique of emitter feedback; however, the current imbalance worsens during turn-on. Similarly, emitter feedback for an asymmetric feedback busbar length can improve current imbalance during turn-on but has no impact during turn-off. This ultimately implies that a single perfect solution is not possible using the passive gate control technique; however, emitter feedback can still be the preferred choice considering its impact on a higher number of parameters that influence unbalancing compared to other passive gate control techniques. The passive feedback methods discussed in Section 3.2 can mainly improve or minimize the current imbalance rather than realizing current balancing or optimized current sharing under most of the unbalanced conditions.

The condition and criterion for a single IGBT are discussed in [54] using a proposed signal flow graph model that can be vital for parallel-connected IGBT system design. It establishes a relationship between critical parameters: emitter inductance, gate inductance, collector inductance, and gate resistance. If emitter inductance is zero, the critical gate resistance required increases with the increase in gate inductance. Furthermore, if gate inductance is constant, critical gate resistance decreases as emitter inductance increases.

The circuit stability depends on the emitter inductance, and a small emitter inductance destabilizes the circuit, considering that an increase in emitter inductance is preferable to an increase in collector inductance, which can minimize the possibility of oscillation; gate inductance should be as small as possible to minimize the oscillation [54]. The effect of emitter inductance in [31] for turn-off provides confirmation considering 0 nH, 5 nH, 10 nH, 15 nH, and 20 nH cases, and demonstrates that the current redistribution phenomenon is almost absent for the 20 nH case compared to the 0 nH case, which has dominant current redistribution due to the self-turn-off of the IGBT. Therefore, the design criteria in [54] would be significant, as the emitter inductance, gate inductance, collector inductance, and gate resistance are the crucial parameters for current imbalance, as well as system oscillation. Nevertheless, these criteria must be exploited for parallel system design, which requires overall system parameter design optimization.

The influence of the device parameters considering the IGBT, as well as the antiparallel diode, is analyzed in [55] for paralleling of specific types of module packages. This study targets the most influential parameters for the parallel-connected system and defines the relationship for reverse recovery energy ( $\Delta E_{recov}$ ) with the forward voltage of the diode ( $\Delta V_F$ ), turn-on energy ( $\Delta E_{on}$ ) with the forward voltage of the diode ( $\Delta V_F$ ) and threshold voltage ( $V_{C,th}$ ), and turn-off energy ( $\Delta E_{off}$ ) with the collector-emitter voltage ( $\Delta V_{CE,sat}$ ) and turn-off delay time ( $\Delta t_{dvoff}$ ). This demonstrates that the linear relation between current unbalancing corresponding to  $\Delta t_{dvoff}$  has an effect during turn-off, a dominant  $V_{C,th}$  effect during turn-on, a dominant  $V_F$  effect during reverse recovery and turn-on, and a  $V_{CE,sat}$  dominant effect during turn-off, which can lead to different slopes of  $V_{CE}$  during turn-off, and ultimately lead to current redistribution phenonmenon. The relationships are mathematically defined as:

Electronics **2023**, 12, 3826 **f** 15 of 19

$$\Delta E_{recov} = f(\Delta V_F)$$

$$\Delta E_{on} = f(\Delta V_F, \Delta V_P)$$

$$\Delta E_{on} = f(\Delta V_{CE}, \Delta t_{dvoff})$$

# 4.2. Gate-Driving Techniques and Active Gate Control

The gate-driving methods discussed in Section 3.1 and active current-balancing technique discussed in Section 3.3 for parallel-connected power semiconductor devices are summarized in Figures 9 and 10. The gate-driving technique is categorized fundamentally as direct driving, common gate driving, or individual gate driving. The simplest way of driving parallel-connected power devices is via direct gate driving, which is subcategorized into separate gate resistance, isolated separate gate resistance, and passive adapter board driving. Further, common gate driving and individual gate driving (which is a kind of active adapter board driving) are subdivided into separate auxiliary emitter driving and common auxiliary emitter driving. The individual gate driver can also be subcategorized as isolated gate driving. The common auxiliary emitter provides an additional possibility to incorporate the passive emitter feedback technique.

**Figure 10.** Gate-driving techniques for parallel-connected power devices.

The active gate control current-balancing techniques are mainly realized using the individual gate-driving method to assist corresponding power devices with gate signal adjustment capabilities. Most of the active gate controls employ the delay adjustment technique, which is the simplest to implement; however, computation and decisions for gate delay can be complex depending on the implementation methodology. In addition, the individual gate-driving implementation is costly compared to other approaches as it

Electronics **2023**, 12, 3826 16 of 19

requires separate active gate drivers for each device. Isolated individual gate-driving is the costliest means of implementation but provides maximum flexibility for independent adjustment. The gate voltage control technique provides static current balancing, and dynamic gate voltage control has the capability to adjust the device current slope as well as the gate delay. Dynamic gate voltage control has higher complexity compared to other techniques considering the computation and determination of the pattern for the selection of dynamic gate resistance for the implementation.

# 4.3. Reliability, Derating, and Stability Factors

The current imbalance in the parallel-connected system enforces the SOA operational and thermal operational limits considering the system reliability. The worst-case scenario of the maximum possible current imbalance must be considered to determine the derating factors corresponding to SOA. Furthermore, the maximum junction temperature operation of a single chip should be considered to determine the thermal derating. The complexity of these factors increases with the increased number of parallel modules/discrete devices/chips. Derating criteria are discussed in [55] based on the relationship's dominant parameter's impact on current balancing to achieve operation within the SOA limit.

Current imbalance impacts the junction temperature and, considering this, the reliability of parallel-connected switches is discussed in [56] using the Markov-based reliability model. The mean time to failure criterion is considered to analyze the failure possibility under different current sharing and operating conditions. The operating conditions are parallel-connected switches with redundant operation and parallel-connected switches with modular operation. Furthermore, the short-circuit performance and reliability of parallel-connected devices is indispensable; it is discussed for the parallel SiC MOSFET and Si-IGBT in [57]. The performance is studied considering different device parameters, and non-identical  $V_{\rm G,th}$  parameter variation is the dominant factor under the short-circuit condition.

The derating factor for SOA operation and the thermal operation limit are mentioned in [14]. The cooling of the devices is another aspect, and homogenous cooling of the paralleled device/module system is a critical factor to realize homogenous sharing of the current and to maintain the junction temperature within the operating limit, as well as to ensure it is closely matched. It has been mentioned that the current imbalance can be up to 50% due to  $t_{\rm d,off}$  and  $t_{\rm dvoff}$  during turn-off; therefore, to achieve operation within SOA, the turn-off current must be reduced by 50%. Further, the switching losses and on-state losses must be critically analyzed corresponding to the unequal current sharing to achieve thermal stability by employing thermal derating based on the junction temperature profile. This factor can be more critical for the full-load operating conditions and high-switching-frequency operations.

The paralleling problems are discussed in [16], which mentions the stability considerations as part of the fundamentals for the parallel-connected IGBT system. The system stability depends on the generated power loss and dissipated power losses; that is, the rate of generated power loss should be less than or equal to the dissipative power, i.e.,  $(\partial P_G/\partial T) \leq (\partial P_D/\partial T)$ . This is important to achieve a stable and settled junction temperature corresponding to an increase in generated power losses. This must be satisfied for a single device, as well as an overall paralleled system, to realize and maintain system stability, along with individual device stability, to avoid thermal runway and violation of SOA operation. Furthermore, it is also worth noting that frequent operation with high temperature swings and operation near the SOA limit can cause accelerated aging and lifetime reduction.

**Author Contributions:** Conceptualization, R.N.T.; methodology, R.N.T. and I.O.; formal analysis, R.N.T. and I.O.; investigation, R.N.T.; resources, R.N.T. and I.O.; data curation, R.N.T.; writing—original draft preparation, R.N.T.; writing—review and editing, R.N.T. and I.O.; project administration, R.N.T.; funding acquisition, R.N.T. All authors have read and agreed to the published version of the manuscript.

Electronics **2023**, 12, 3826 17 of 19

**Funding:** This work is supported by the Japan Society for the Promotion of Science (JSPS) KAKENHI under grant number 20K14720.N.

**Conflicts of Interest:** The authors declare no conflict of interest.

#### References

Ohashi, H.; Omura, I. Role of Simulation Technology for the progress in Power Devices and its Applications. IEEE Trans. Electron Devices 2013, 60, 528–536. [CrossRef]

- 2. Nelson, J.J.; Venkataramanan, G.; Beihoff, B.C. Investigation of Parallel Operation of IGBTs. In Proceedings of the Conference Record of the 2002 IEEE Industry Applications Conference, 37th IAS Annual Meeting (Cat. No.02CH37344), Pittsburgh, PA, USA, 13–18 October 2002; pp. 2585–2591.

- 3. Radke, T.; Lakshmanan, N. *The Next Generation of High-Power IGBT Modules: LV100 for Wind Converter, Photovoltaic Inverter and Motor Drive*; Mitsubishi Electric Europe: Uxbridge, UK, 2019.

- 4. Milan, R.; Ana, V.; Abdoulaye, L. IGBT Market and Technology Trends 2021, Yole Development. August 2021. Available online: https://medias.yolegroup.com/uploads/2021/08/YINTR21197\_IGBT\_Market\_Technology\_Trends\_August\_2021\_Sample.pdf (accessed on 1 August 2023).

- 5. Poshun, C.; Ezgi, D. Power SiC Market and Technology Report, Yole Development, 2022. Available online: https://www.yolegroup.com/product/report/power-sic-2022/ (accessed on 1 August 2023).

- 6. Anup, B. Application Trends in SiC, United SiC. In *Disruptive Wide Bandgap Semiconductors, Related Technologies, and Their Applications;* IntechOpen: London, UK, 2019.

- 7. Chen, N.; Chimento, F.; Nawaz, M.; Wang, L. Dynamic Characterization of Parallel-Connected High-Power IGBT Modules. *IEEE Trans. Ind. Appl.* **2014**, *51*, 539–546. [CrossRef]

- 8. Werner, R.; Weigel, J.; Boehmer, J.; Eckel, H.-G. Potential of passive feedbacks to reduce dynamic current imbalances of paralleled IGBTs. In Proceedings of the PCIM Europe International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Nuremberg, Germany, 7–9 May 2019.

- 9. Jadhav, V.; Zhou, Y.; Jansen, U. Analysis of different IGBT gate driver strategies influencing dynamic paralleling performance. In Proceedings of the PCIM Asia International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Shanghai, China, 28–30 June 2016.

- 10. Kizilyalli, I.C.; Carlson, E.P.; Cunningham, D.W.; Manser, J.S.; Xu, Y.; Xu, A.; Liu, A.Y. Wide Band-Gap Semiconductor Based Power Electronics for Energy Efficiency; US Department of Energy (USDOE): Washington, DC, USA, 2018.

- 11. Zhao, Z. Application Tips to Parallel IGBT; Infineon Technologies: Neubiberg, Germany, 2008.

- 12. Perez-Delgado, R.; Velasco-Quesada, G.; Roman-Lumbreras, M. Current sharing control strategy for IGBTs connected in Parallel. *J. Power Electron.* **2016**, *16*, 769–777. [CrossRef]

- 13. Li, H.; Zhou, W.; Wang, X.; Munk-Nielsen, S.; Li, D.; Wang, Y.; Dai, X. Influence of paralleling dies and paralleling half bridges on transient current distribution in multichip power modules. *IEEE Trans. Power Electron.* **2018**, *33*, 6483–6487. [CrossRef]

- 14. Paralleling of IGBT Modules, App. Note 5SYA 2098-00, Hitachi Energy Switzerland Limited. Available online: https://search.abb.com/library/Download.aspx?DocumentID=5SYA2098&LanguageCode=en&DocumentPartId=&Action=Launch (accessed on 1 August 2023).

- 15. IGBT Modules in Parallel Operation with Central and Individual Driver Board, App. Note AN 17-001 SEMIKRON. Available online: https://www.semikron-danfoss.com/service-support/downloads/detail/semikron-application-note-modules-in-parallel-operation-with-central-and-individual-driver-board-en-2017-01-27-rev-00.html (accessed on 1 August 2023).

- 16. Schlapbach, U. Dynamic paralleling problems in IGBT module construction and application. In Proceedings of the International Conference on Integrated Power Electronics Systems, Nuremberg, Germany, 16–18 March 2010.

- 17. Letor, R. Static and dynamic behaviour of paralleled IGBTs. IEEE Trans. Ind. Appl. 1992, 28, 359-402. [CrossRef]

- 18. Medaule, D.; Yu, Y. Parallel Operations of High Power IGBTs. In Proceedings of the IEE Colloquium on IGBT Propulsion Drives, London, UK, 25 April 1995.

- 19. Schrader, R.; Muenster, P.; Eckel, H.-G. Dynamic Current Sharing and Gate Feedback During Turn-OFF of Paralleled IGBTs. In Proceedings of the PCIM Europe Europe International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Nuremberg, Germany, 5–7 June 2018.

- Wintrich, A.; Nascimento, J.; Leipenat, M.; Gmbh, S.E.; Kg, C. Influence of parameter distribution and mechanical construction on switching behaviour of parallel IGBT. In Proceedings of the PCIM Europe International Conference Power Electronics, Intelligent Motion, Power Quality, Nuremberg, Germany, 30 May–1 June 2006.

- 21. Xiao, Y.; Liu, Q.; Tang, Y.; Du, L.; Ma, H. Current sharing model of parallel connected IGBTs during turn-on. In Proceedings of the IEEE-IECON, 40th Annual Conference of the IEEE Industrial Electronics Society, Dallas, TX, USA, 29 October–1 November 2014.

- 22. Soltau, N.; Wiesner, N.; Ando, Y.; Sakai, J.; Hatori, K. Parallel Operation: Influence of Power Module Parameters, Mitsubishi, February 2023. Available online: https://www.meu-semiconductor.eu/wp-content/uploads/2023/02/BPs\_02-23\_MitsubishiReprint.pdf (accessed on 1 August 2023).

- 23. Parallel Connection: Chapter 10, Fuji Electric. Available online: https://www.fujielectric.co.jp/products/semiconductor/model/ev\_hev\_igbt/application/box/doc/pdf/MT5F33743\_E\_Rev1.3\_10.pdf (accessed on 1 August 2023).

Electronics **2023**, 12, 3826 18 of 19

24. Joyce, J. Current Sharing and Redistribution in High Power IGBT Modules. Ph.D. Thesis, University of Cambridge, Cambridge, UK, 2001.

- 25. Weigel, J.; Boehmer, J.; Nagel, A.; Kleffel, R. Paralleling High Power Dual Modules: A Challenge for Application Engineers and Power Device Manufacturers. In Proceedings of the European Conference on Power Electronics and Applications (EPE ECCE Europe), Warsaw, Poland, 11–14 September 2017.

- 26. Insulated Gate Bipolar Transistor IGBTs, Application Note, 2022, Toshiba Electronic Devices and Storage Corporation, Japan. Available online: https://toshiba.semicon-storage.com/info/docget.jsp?did=63557 (accessed on 1 August 2023).

- 27. IGBT Gate Driver Reference Design for Parallel IGBTs with Short-Circuit Protection and External BJT Buffer. TI Designs; Texas Instruments Incorporated: Dallas, TX, USA, 2017.

- 28. Is It Possible to Connect Multiple IGBT in Parallel? Toshiba Electronic Devices and Storage Corporation, Japan. Available online: https://toshiba.semicon-storage.com/ap-en/semiconductor/knowledge/faq/mosfet\_igbt/igbt-016.html (accessed on 1 August 2023).

- 29. Yong, T.; Bo, W.; Jie, L.Q. Research on Parallel Operation Characteristic and current sharing method of High Power IGBT. In Proceedings of the Journal of Physics: Conference Series, Joint 2019 International Conference on Ubiquitous Power Internet of Things (UPIOT 2019) & 2019 3rd International Symposium on Green Energy and Smart Grid (SGESG 2019), Chongqing, China, 21–23 August 2019; IOP Publishing: Bristol, UK, 2019.

- Hermwille, M. The Use of Gate Resistors to Control IGBT Switching; Semikron International: Nürnberg, Germany, 2008.

- 31. Schrader, R.; Cordt, D.; Münster, P.; Eckel, H.-G. Influences of gate-circuit and parasitic inductances on turn-OFF current imbalances of paralleled IGBTs due to differences in their switching behavior. In Proceedings of the European Conference on Power Electronics and Applications (EPE ECCE Europe), Riga, Latvia, 17–21 September 2018.

- 32. Böhmer, J.; Schumann, J.; Fleisch, K.; Eckel, H.-G. Current mismatch during switching due to the self-turn-off effect in paralleled IGBT. In Proceedings of the European Conference on Power Electronics and Applications (EPE), Lile, France, 2–6 September 2013.

- 33. Wu, R.; Smirnova, L.; Wang, H.; Iannuzzo, F.; Blaabjerg, F. Comprehensive Investigation on Current Imbalance among Parallel Chips inside MW-Scale IGBT Power Modules. In Proceedings of the International Conference on Power Electronics and ECCE Asia (ICPE-ECCE Asia), Seoul, Republic of Korea, 1–5 June 2015.

- 34. Thomas, S.; Matthias, W. Paralleling of IGBT Modules-Derating Factor and Layout. Infineon, October 2019. Available online: https://www.infineon.com/dgdl/Infineon-AN2004\_06\_Paralleling\_of\_EconoPACK+-ApplicationNotes-v01\_00-EN.pdf? fileId=db3a304412b407950112b40edf8b12b2 (accessed on 1 August 2023).

- 35. Parallel Operation of Dynex Modules ANN5505 Applicayion Note, Dynex Semiconductor, July 2002. Available online: https://www.dynexsemi.com/Portals/0/PDF/DNX\_AN5947.pdf?ver=erlYQ8DZhgkoNaSPguaZ7g%3D%3D (accessed on 1 August 2023).

- 36. High Voltage IGBT Modules Application Manual, Hitachi, 2009. Available online: https://pdd.hitachi.eu/documents/products/igbt/application-notes/application\_note\_r2.pdf (accessed on 1 August 2023).

- Chamund, D.; Findlay, B.; Birkett, K.; Shammas, N. Parallel operation of IGBT modules using de-rating factors'. In Proceedings of the 37th International Universities Power Engineering Conference (UPEC), Stafford, UK, 9–11 September 2002.

- 38. Shammas, N.Y.A.; Withanage, R.; Chamund, D. Review of series and parallel connection of IGBTs. *IEEE Proc. Circuits Devices Syst.* **2006**, *153*, 34–39. [CrossRef]

- 39. Hofer, P.; Karrer, N.; Gerster, C. Paralleling intelligent IGBT power modules with active gate-controlled current balancing. In Proceedings of the IEEE POWER Electronics Specialist Conference, Baveno, Italy, 23–27 June 1996.

- 40. Bortis, D.; Biela, J.; Kolar, J.W. Active gate control for current balancing of parallel connected IGBT modules in solid-state modulators. *IEEE Trans. Plasma Sci.* **2008**, *36*, 2632–2637. [CrossRef]

- 41. Lobsiger, Y.; Bortis, D.; Kolar, J.W. Decentralized active gate control for current balancing of parallel connected IGBT modules. In Proceedings of the European Conference on Power Electronics and Applications, Birmingham, UK, 30 August–1 September 2011.

- 42. Alvarez, R.; Bernet, S. A new delay time compensation principle for parallel connected IGBTs. In Proceedings of the IEEE Energy Conversion Congress and Exposition, Phoenix, AZ, USA, 17–22 September 2011.

- 43. Alvarez, R.; Fink, K.; Bernet, S.; Antonio, C. Current Balancing of Parallel Connected Semiconductor Components. US Patent 8446206B2, 21 May 2013.

- 44. Alvarez, R.; Fink, K.; Bernet, S. Simulation and experimental investigation of parallel connected IGBTs. In Proceedings of the IEEE International Conference on Industrial Technology, Via del Mar, Chile, 14–17 March 2010.

- 45. Alvarez, R.; Bernet, S. Sinusoidal Current Operation of Delay-Time Compensation for Parallel-Connected IGBTs. *IEEE Trans. Ind. Appl.* **2014**, *50*, 3485–3493. [CrossRef]

- 46. Tripathi, R.N.; Tsukuda, M.; Omura, I. A fully digital feedback control of gate driver for current balancing of parallel connected power devices. *Microelectron. Reliab.* **2018**, *88*–*90*, 505–509. [CrossRef]

- 47. Tripathi, R.N.; Tsukuda, M.; Omura, I. Peak minimisation-based gate delay compensation for active current balancing of parallel IGBT system. *Microelectron. Reliab.* **2019**, 100–101, 113426. [CrossRef]

- 48. Tripathi, R.N.; Tsukuda, M.; Omura, I. Dynamic Current Balancing of Parallel Connected IGBT Devices using PCB Sensor for Integration in Power Modules. In Proceedings of the International Conference on Integrated Power Electronics Systems (CIPS), Berlin, Germany, 24–26 March 2020.

- 49. Brandelero, J.; Ewanchuk, J.; Degrenne, N.; Mollov, S. Lifetime extension through Tj equalisation by use of intelligent gate driver with multi-chip power module. *Microelectron. Reliab.* **2018**, *88*–90, 428–432. [CrossRef]

- 50. Chen, J.-F.; Lin, J.-N.; Ai, T.-H. The Techniques of the Serial and Paralleled IGBTs. IEEE IECON. In Proceedings of the 22nd International Conference on Industrial Electronics, Control, and Instrumentation, Taipei, Taiwan, 5–10 August 1996.

51. Wang, X.; Zhao, Z.; Yuan, L. Current Sharing of IGBT Modules in Parallel with Thermal Imbalance. In Proceedings of the IEEE Energy Conversion Congress and Exposition, Atlanta, GA, USA, 12–16 September 2010.

- 52. Sasaki, M.; Nishio, H.; Ng, W.T. Dynamic gate resistance control for current balancing in parallel connected IGBTs. In Proceedings of the IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, USA, 17–21 March 2013.

- 53. Sasaki, M.; Nishio, H.; Shorten, A.; Ng, W.T. Current Balancing Control for Parallel Connected IGBTs Using Programmable Gate Driver Output Resistance. In Proceedings of the International Symposium on Power Semiconductor Devices & IC's (ISPSD), Kanazawa, Japan, 26–30 May 2013.

- 54. Kono, H.; Omura, I. Parasitic oscillation analysis of trench IGBT during short-circuit type II using TCAD-based signal flow graph model. *IEEE Trans. Electron. Devices* **2022**, *69*, 5705–5712. [CrossRef]

- 55. Demystifying the Paralleling of IGBT Modules, Infineon, 2019. Available online: https://www.infineon.com/dgdl/Infineon-Demystifying\_the\_paralleling\_of\_IGBT\_modules-Article-v01\_00-EN.pdf?fileId=5546d4626d82c047016da4e0023f256e (accessed on 1 August 2023).

- 56. Rahimi, T.; Ding, L.; Abadifard, A.; Ghavidel, P.; Farhadi, M.; Faraji, R. Unbalanced currents effect on the thermal characteristic and reliability of parallel connected power switches. *Case Stud. Therm. Eng.* **2021**, *26*, 101134. [CrossRef]

- 57. Wu, R.; Mendy, S.; Agbo, N.; Gonzalez, J.O.; Jahdi, S.; Alatise, O. Performance of Parallel Connected SiC MOSFETs under Short Circuits Conditions. *Energies* **2021**, *14*, 6834. [CrossRef]

**Disclaimer/Publisher's Note:** The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content.