Doctoral Thesis

Mar. 2014

# Studies on Test Application at Field Test and Low Power Logic-BIST

フィールドにおけるテスト印加と低電力論理 BIST に関する研究

A thesis submitted in partial fulfillment of the requirements for the degree of doctor of philosophy

By

Senling Wang

Supervisor: Prof. Seiji Kajihara

Department of Information Systems

Graduate School of Computer Science and Systems Engineering

# **Abstract**

Advances in semiconductor process technology have resulted in various aging issues in field operation of Very Large Scale Integration (VLSI) circuits. For example, HCI (Hot carrier injection), BTI (Bias Temperature Instability), TDDB (Time Dependent Dielectric Breakdown) are well-known aging phenomena, and they can increase the circuit delay resulting in serious reliability problems. In order to avoid system failures caused by aging, recent design usually sets a certain timing margin in operational frequency of the circuit. However, it is difficult to determine the size of the proper timing margin because of the difficulty of prediction of its aging speed in actual use that is related to operational environment. Pessimistic prediction may result in performance sacrificing although it will improve the reliability of the system.

BIST-based field test is a promising way to guarantee the reliability of the circuit through detecting the aging-induced faults during the circuit operation. However, the field test has a limitation on test application time, which makes it difficult to achieve high test quality. Therefore an effective test application method at field is required.

In addition to the requirement of short test application time, the BIST-based field test requires performing at-speed testing in order to detect timing-related defects. However, it is well known that power dissipation during testing is much higher than that in normal circuit operation. Because excessive power dissipation causes higher IR-drop and higher temperature, it results in delay increase during testing, and in turn, causing false at-speed testing and yield loss. While many low power test methods have been proposed to tackle the test power issue, inadequate test power reduction and lower fault coverage still remain as important issues. Moreover, low power testing that just focuses on power reduction is insufficient. When the test power is reduced to a very low level, a timing-related defect may be missed by the test, and a defective circuit will appear to be a good part passing the test. Therefore, appropriate test power control is necessary though it was out of considering in the existing methods.

In this dissertation, we first proposed a new test application to satisfy the limitation of short test application time for BIST-based field test, and then we proposed a new low power BIST scheme that focuses on controlling the test power to a specified value for improving the field test quality.

In chapter 3, a new field test application method named "rotating test" is presented in which a set of generated test patterns to detect aging-induced faults is partitioned into several subsets, and apply each subset in one test session at field. In order to maximize the test quality for rotating test, we proposed test partitioning methods that refer to two items: First one aims at maximizing fault coverage of each subset obtained by partitioning. Second one aims at minimizing the detection time interval of all faults in rotating test to avoid system failures. Experimental results demonstrated the effectiveness of the proposed partitioning methods.

In chapter 4, we proposed a new low power BIST scheme which can control the scan-in power, scan-out power and capture power while keeping test coverage at high level. In this scheme, a new circuit called pseudo low-pass filter (PLPF) is developed for scan-in power control, and a multi-cycle capture test technique is employed to reduce the capture power. In order to control scan-out power dissipated by test responses, we proposed a novel method that selects some flip-flops in scan chains at logic design phase, and fills the selected flip-flops with proper values before starting scan-shift operation so as to reduce the switching activity associated with scan-out. The experimental results for ISCAS-89 and ITC-99 benchmark circuits show that significant scan-in power reduction rate (the original rate of 50% is reduced to 7~8%) and capture power reduction rate (the original rate of 20% is reduced to 6~7%) were derived. With the scan-out controlling method, the scan-out power can be reduced from 17.2% to 8.4%, which could not be achieved by the conventional methods. Moreover, in order to control the test power to the specified rate to accommodate the various test power requirements. A scan-shift power controlling scheme was also discussed. It showed the capability of controlling any scan-shift toggle rate between 6.7% and 50%.

# TABLE OF CONTENTS

| Αl  | BSTRACT                                                                     | I            |

|-----|-----------------------------------------------------------------------------|--------------|

| LI  | IST OF FIGURES                                                              | V            |

| T.I | IST OF TABLES                                                               | VII          |

|     |                                                                             |              |

| 1.  | INTRODUCTION                                                                | I            |

|     | 1.1. BACKGROUND                                                             | 1            |

|     | 1.2. Objective                                                              | 2            |

|     | 1.3. STRUCTURE OF THIS DISSERTATION                                         | 3            |

| 2.  | PRELIMINARY                                                                 | 4            |

|     | 2.1. LSI TEST                                                               | 4            |

|     | 2.2. DESIGN FOR TESTABILITY (DFT)                                           | 5            |

|     | 2.2.1. Scan design                                                          | 5            |

|     | 2.2.2. Logic Built-In Self Test                                             | 7            |

|     | 2.3. FAULT MODELS                                                           | 8            |

|     | 2.3.1. Stuck-at fault model                                                 | 8            |

|     | 2.3.2. Transition fault model                                               | 9            |

|     | 2.3.2.1. Launch-off-Shift (LoS)                                             | 10           |

|     | 2.3.2.2. Launch-off-Capture (LoC)                                           | 11           |

|     | 2.4. FAULT SIMULATION                                                       | 11           |

| 3.  | BIST-BASED FIELD ROTATING TEST FOR AGING-INDUCED FAULT                      | DETECTION 13 |

|     | 3.1. RELIABILITY CHALLENGES: AGING                                          | 13           |

|     | 3.2. FIELD TEST FOR AGING-INDUCED FAULT                                     | 15           |

|     | 3.3. ROTATING TEST                                                          | 16           |

|     | 3.4. PATTERN PARTITION ALGORITHMS FOR ROTATING TEST                         | 17           |

|     | 3.4.1. Pattern partition for fault coverage improvement                     | 18           |

|     | 3.4.1.1. Quality of test partition for rotating test                        | 18           |

|     | 3.4.1.2. Problem formulation                                                | 19           |

|     | 3.4.1.3. Partition Algorithm                                                | 20           |

|     | 3.4.1.4. Experimental results                                               | 24           |

|     | 3.4.2. Pattern partition for reducing the probability of failure appearance | 27           |

|     | 3.4.2.1. Failure Appearance Probability (FAP)                               | 27           |

| 3.4.2.2. Problem formulation                                        | 30 |

|---------------------------------------------------------------------|----|

| 3.4.2.3. Partition algorithms                                       | 30 |

| 3.4.2.4. Experimental Results                                       | 32 |

| 3.5. CONCLUSIONS                                                    | 35 |

| 4. TEST POWER REDUCTION FOR LOGIC-BIST                              | 36 |

| 4.1. POWER DISSIPATION IN LSI                                       | 37 |

| 4.2. TEST POWER ISSUES                                              | 38 |

| 4.3. LOW POWER TEST APPROACHES                                      | 39 |

| 4.3.1. Low power scan test                                          | 39 |

| 4.3.2. Low power Logic-BIST                                         | 39 |

| 4.4. OBJECTIVES OF THIS WORK                                        | 42 |

| 4.5. TEST POWER METRIC IN THIS WORK                                 | 43 |

| 4.6. Proposed Power Reduction Methodologies                         | 44 |

| 4.6.1. Low power for Scan-in and Capture                            | 44 |

| 4.6.1.1. Scan-in power reduction with PLPF (Pseudo Low-Pass Filter) | 44 |

| 4.6.1.2. Capture power reduction with Multi-cycle test              | 49 |

| 4.6.1.3. Experimental results                                       | 50 |

| 4.6.2. Scan-in power controlling                                    | 54 |

| 4.6.2.1. Requirement of power controlling                           | 54 |

| 4.6.2.2. Scan-in power controlling scheme                           | 54 |

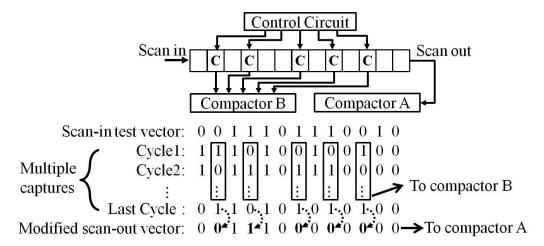

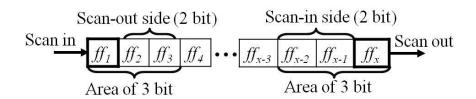

| 4.6.3. Scan-out power reduction by outputs overwriting              | 55 |

| 4.6.3.1. Scan-out power issues                                      | 55 |

| 4.6.3.2. Proposed scan-out power reduction method                   | 56 |

| 4.6.3.3. Control FFs' Selection                                     | 57 |

| 4.6.3.4. Value filling methods                                      | 63 |

| 4.6.3.5. Experimental results                                       | 68 |

| 4.7. CONCLUSIONS                                                    | 72 |

| 5. SUMMARY                                                          | 73 |

| REFERENCES                                                          | 75 |

| I IST OF DURI ICATIONS                                              | 70 |

# LIST OF FIGURES

| Figure 2.1 Principle of LSI testing [1]                         | 4  |

|-----------------------------------------------------------------|----|

| Figure 2.2 A scan-design schematic                              | 6  |

| Figure 2.3 Structure of Muxed-D scan cell                       | 6  |

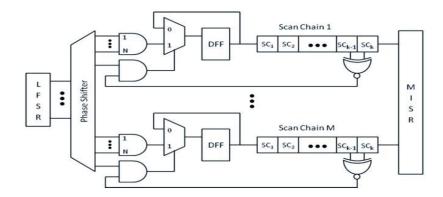

| Figure 2.4 Logic-BIST architecture [2]                          | 7  |

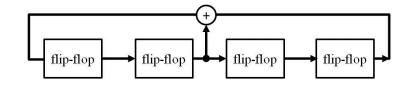

| Figure 2.5 Four-stage LFSR                                      | 8  |

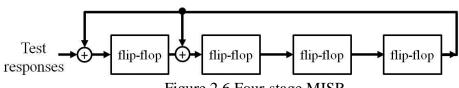

| Figure 2.6 Four-stage MISR                                      | 8  |

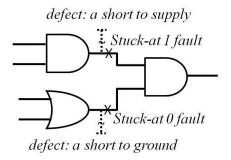

| Figure 2.7 Stuck-at-0 fault and stuck-at-1 fault                | 9  |

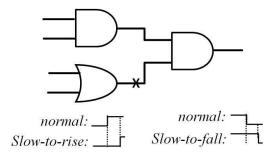

| Figure 2.8 Slow-to-rise fault and slow-to-fall fault            | 10 |

| Figure 2.9 Waveform of launch-off-shift                         | 11 |

| Figure 2.10 Waveform of launch-off-capture                      | 11 |

| Figure 2.11 Fault simulation scheme [1]                         | 12 |

| Figure 3.1 Bathtub curve for LSI's reliability [12]             | 14 |

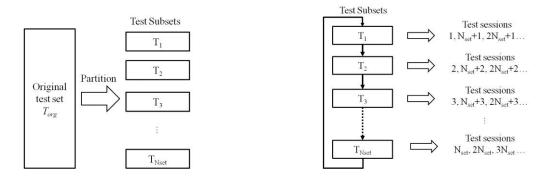

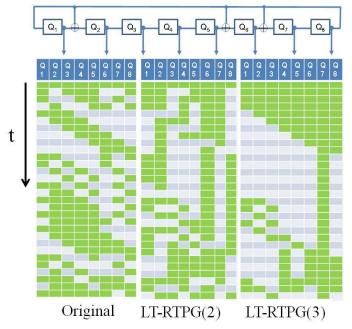

| Figure 3.2 Test partitioning and rotating test                  | 16 |

| Figure 3.3 Example for test pattern replacement                 | 24 |

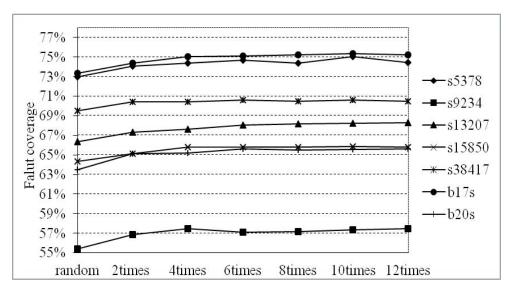

| Figure 3.4 Experimental result for Nset=8                       | 25 |

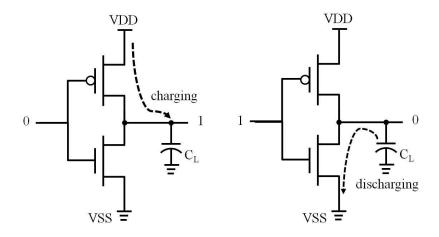

| Figure 4.1 Power dissipation in COMS gate                       | 37 |

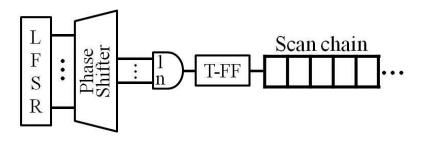

| Figure 4.2 Structure of LT-RTPG [40]                            | 41 |

| Figure 4.3 Comparison of LT-RTPG and the original LFSR patterns | 41 |

| Figure 4.4 Structure of ALP-RTPG [41]                           | 42 |

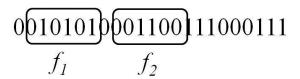

| Figure 4.5 High frequency in a test vector                      | 45 |

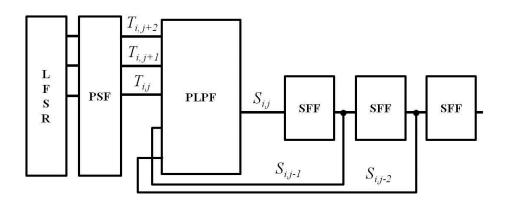

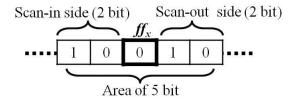

| Figure 4.6 Structure for scan-in power reduction                | 45 |

| Figure 4.7 Detail Structure of PLPF (3)                         | 46 |

| Figure 4.8 PSF for PLPF(3)                                      | 47 |

| Figure 4.9 PSF for PLPF(5)                                      | 48 |

| Figure 4.10 Vector Comparison with PLPF and LFSR                | 48 |

| Figure 4.11 Multi-capture waveform                              | 49 |

| Figure 4.12 Multi-cycle BIST with partial observation [46]      | 50 |

| Figure 4.13 Proposed capture timing                             | 50 |

| Figure 4.14 Capture-Power Reduction with Mul (N, 1)     | 52 |

|---------------------------------------------------------|----|

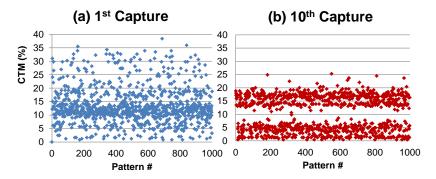

| Figure 4.15 Capture toggle rate (CTM) of each vector    | 53 |

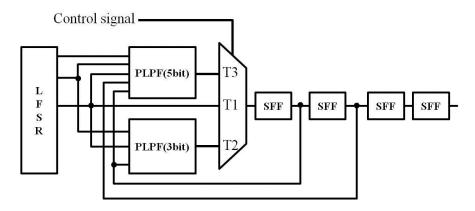

| Figure 4.16 Power controlling scheme                    | 55 |

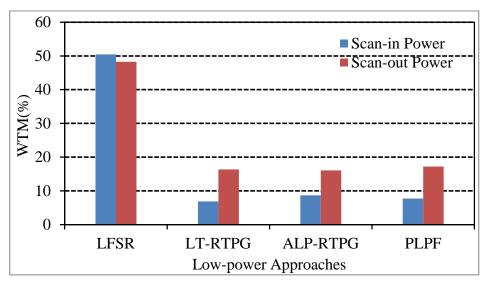

| Figure 4.17 Comparison of scan-in/out power reduction   | 56 |

| Figure 4.18 Idea of scan-out power reduction            | 57 |

| Figure 4.19 State of a scan chain of b14                | 58 |

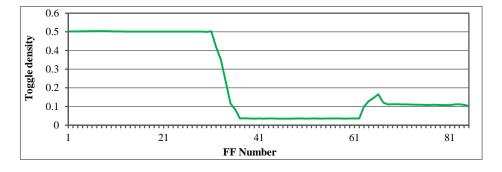

| Figure 4.20 Computation of toggle density               | 59 |

| Figure 4.21 Special cases of toggle density computation | 59 |

| Figure 4.22 Toggle density of a scan chain of b14       | 59 |

| Figure 4.23 Fault observation capacity of FFs           | 61 |

| Figure 4.24 Fault propagation capacity of FFs           | 61 |

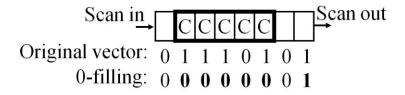

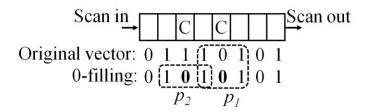

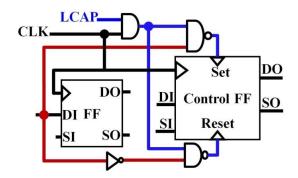

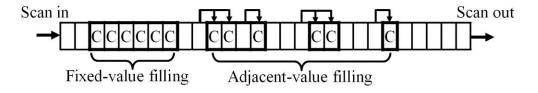

| Figure 4.25 Control structure for 0-filling.            | 64 |

| Figure 4.26 Distribution of control FFs in scan chains  | 64 |

| Figure 4.27 0-filling for consecutive control FFs       | 65 |

| Figure 4.28 0-filling for alternate control FFs         | 65 |

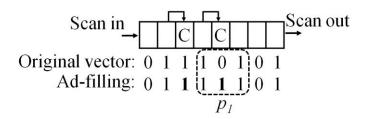

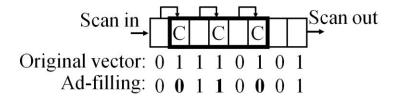

| Figure 4.29 Concept of adjacent-value filling           | 65 |

| Figure 4.30 Ad-filling for alternate control FFs        | 66 |

| Figure 4.31 Ad-filling for consecutive control FFs      | 66 |

| Figure 4.32 Feeding two control FFs by one FF           | 67 |

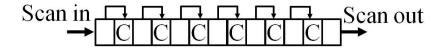

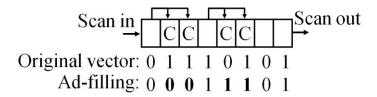

| Figure 4.33 Control structure for Ad-filling.           | 67 |

| Figure 4.34 Structure of hybrid value filling           | 68 |

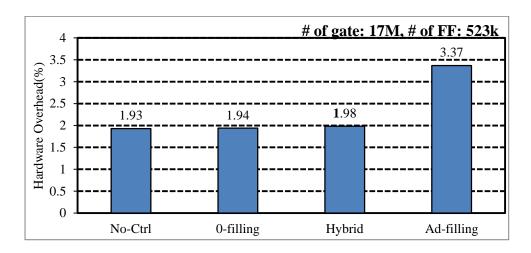

| Figure 4.35 Area overhead (investment) estimation       | 72 |

# LIST OF TABLES

| Table 3.1 Test pattern and detected faults                                            | 19            |

|---------------------------------------------------------------------------------------|---------------|

| Table 3.2 Examples of test partitioning                                               | 19            |

| Table 3.3 Similarity of test vector pairs                                             | 21            |

| Table 3.4 Fault list of a sub test set T <sub>1</sub>                                 | 23            |

| Table 3.5 Experimental result for random partition and the proposed partition with A  | $V_{set} = 8$ |

|                                                                                       | 26            |

| Table 3.6 Run time                                                                    | 26            |

| Table 3.7 Experimental result for the proposed partition algorithm with $N_{set} = 8$ | 27            |

| Table 3.8 Experimental results with $N_{test}$ =10                                    | 34            |

| Table 3.9 Experimental results with $N_{test}$ =20                                    | 34            |

| Table 3.10 Run time for GA and Proposed partition                                     | 34            |

| Table 4.1 Scan-in power reduction with Mul (0, 1)                                     | 51            |

| Table 4.2 Capture power reduction with Mul (1/15/20/30, 1)                            | 52            |

| Table 4.3 Test Coverage Evaluation                                                    | 53            |

| Table 4.4 Scan-in & Scan-out power evaluation                                         | 69            |

| Table 4.5 Peak power evaluation                                                       | 69            |

| Table 4.6 Fault coverage evaluation                                                   | 70            |

| Table 4.7 FFs control in hybrid value filling                                         | 71            |

# Chapter 1

## 1. Introduction

## 1.1. Background

Large Scale Integration (LSI) macro-chip plays a major role in modern human society that has been widely used in many types of electronic systems including computer, cell phone, motor vehicle, airplane, electrical appliances, etc. A very small defect on the chip can easily result in system failure and then lead to the loss of system reliability or even a big damage. Test plays an important role for the assurance of high level system reliability. Typically, test applies a set of test pattern to the input of circuit under test (CUT) and compares the output responses with the expected responses to find the defect-free chip as the responses match. In recent years, with the advances of semiconductor process technology, the transistor scale is shrinking, and more transistors are integrated onto the chip that circuit becomes complex. According to Moore's law, the number of transistors on a chip roughly doubles every couple of years. The most modern microprocessors (Intel's 62-Core Xeon Phi) in 2013 used a 22nm process and contained more than five billion transistors. The reduction of transistor scale and the huge amount of transistors on a chip increase the probability that manufacturing defects on the circuit resulting in faulty-chip. While faulty-chips can be removed by the production test and good chips will be shipped to the customers, when a good chip is put in the actual use for a long time or works at the severe environment, various aging phenomena such as HCI (Hot carrier injection), BTI (Bias Temperature Instability), TDDB (Time Dependent Dielectric Breakdown) might cause the increase of leakage current or open/short faults which can increase the delay resulting serious reliability problems. In order to avoid system failures caused by aging, recent design usually set a certain timing margin in operational frequency. However, it is difficult to determine the size of timing margin due to the difficulty of prediction of its aging speed in actual use that is related to operational environment. Pessimistic prediction may result in performance sacrificing although it will improve the reliability of the system.

BIST-based (Built-In Self Test) field test is a promising way in guaranteeing the reliability of the circuit because it can detect the aging-induced faults during circuit operation. However, since the time allowed for testing during circuit operation usually be very short (e.g.: 10msec), which makes it difficult to achieve high test quality.

In addition to the requirement of short test application time, the BIST-based field test requires performing at-speed testing in order to detect the timing-related defects. However, it is well known that power dissipation during testing is far higher than that in normal circuit operation. Excessive test power dissipation can cause higher IR-drop and higher temperature that result in delay variation during testing, and in turn, causing false at-speed testing and yield loss.

## 1.2. Objective

As described in the previous section, BIST-based field test is a promising way for guaranteeing the reliability of LSI by detecting the aging-induce faults in the field. However, the limitation of test application time of field testing and the high power dissipation during test are the big challenges for enhancing the test quality of field test. In this dissertation, these two problems will be discussed as the current issues and their solutions will be given.

In order to satisfy the limitation of short test application time for BIST-based field test for aging-induce faults detection, a BIST-based field rotating test will be presented. A set of generated test patterns to detect the aging induced faults is partitioned into several subsets, and apply each subset in one test session at field by rotating. The number of test patterns of each subset will not exceed the pattern limit derived from the upper bound of test application time. As the number of test patterns applied to each test is decreased, it will cause test quality loss. For maximizing the test quality for rotating test, two test partitioning methods that refer to two items will be presented: First one aims at maximizing fault coverage of each subset obtained by partitioning. Second one aims at minimizing the detection time interval of all faults in rotating test to avoid system failures.

For the power reduction of BIST-based field test, while many approaches have been proposed, existing methods only take into account reducing some parts of test power, power reduction is inadequate, and also lower fault coverage still remains as important issue. In addition, existing methods just focus on power reduction, however, if the test power is excessively reduced, some timing-related defects may be missed by the test and a defective circuit will appear to be a good part passing the test. Therefore, controlling the test power to a specified level is important. In this dissertation, we proposed a new low power BIST scheme to tackle these problems. In this scheme, for reducing the scan shift power, scan-in power (refer to the power dissipated by shifting test pattern into the scan chain) and scan-out power (refer to the power dissipated by shifting test responses out the scan chain) are considered individually. A new circuit called pseudo low-pass filter (PLPF) is developed to make the test patterns smoother with low switching activity for scan-in power reduction. A method that selects some flip-flops in scan chains at logic design phase, and overwrites the selected flip-flops' values before starting scan-shift so as to make the test responses smoother with low switching activity is proposed to reduce the scan-out power. For reducing the capture power (refer to the instantaneous power consumed by captured vectors at capture time), a multi-cycle test scheme is employed, where many capture clock cycles are executed in the capture mode during test. Furthermore, using PLPFs with different scan-in power reduction capability can control the scan-shift power to the user specified level.

# 1.3. Structure of this Dissertation

This dissertation is organized as follows:

Chapter 2 introduces some important concepts in LSI test related to this study.

Chapter 3 introduces BIST-based field rotating test for the aging-induced fault detection.

Chapter 4 introduces a new low power Logic-BIST scheme.

Chapter 5 outlines a summary of the methods proposed in this study.

# Chapter 2

## 2. Preliminary

In this chapter, some important concepts in LSI test related to this study will be described including the principle of LSI test, design for testability (DFT) technique, fault modeling and the concept of fault simulation.

#### 2.1. LSI Test

In the manufacturing process of LSI, process variations such as impurities in wafer material and chemicals, dust particles or in the projection system, etc., can produce physical defects on the chip [1]. Typical defects are broken conductors, missing contacts, bridging between conductors and many other phenomena that can make the chip fail. Since defects produced during manufacturing process are unavoidable, as a result, a fabricated chip may be non-conformance to the specification decided by the designer that is faulty and cannot be shipped to the market. In order to find the defect-free chip, test is required.

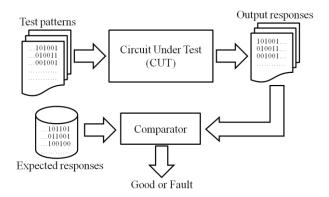

Figure 2.1 illustrates the basic principle of LSI testing. A set of binary stimuli (test patterns) is applied to the inputs of circuit under test (CUT), and compares the output responses with the expected responses decided by the designer. The circuit is considered to be good if the responses match.

Figure 2.1 Principle of LSI testing [1]

## 2.2. Design for Testability (DFT)

Conventional test is to set the primary input of a circuit to the desired values and observe the test responses from the primary output. This approach worked well for the small circuit that mainly consisted of combinational logic. However, with the advance of manufacturing technology, more capabilities are integrated onto a chip, and the circuit becomes complicated. A large circuit contains not only combinational logic but also sequential elements such as flip-flops or latches. For the high test quality, sequential elements in the circuit need to be set to the desired values, test pattern generation needs to create test sequences over many clock cycles to justify desired assignments to circuit inputs. As a result, run times and complexity of the test generation increases.

Design for testability (DFT) refers to design techniques that make products easier to test. DFT techniques add some hardware used for test to the CUT to make the internal state of the circuit easier to be controlled and observed from external access. The most popular DFT techniques for LSI test include scan design, Logic Built-In Self-Test. In the following sub-sections, they will be described briefly.

#### 2.2.1. Scan design

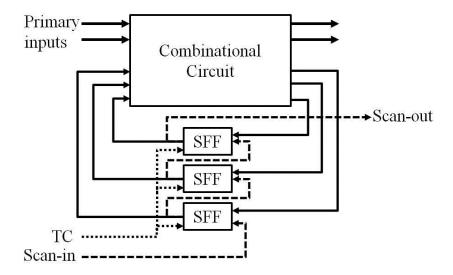

Scan design is currently the most common DFT technique [2]. The main idea in scan design is to obtain the controllability and observability for the sequential elements in the circuit. Typically, this is done by adding a test mode to the circuit and all flip-flops functionally form one or more shift registers called scan chains. Scan chains have a unique scan-input per scan segment. Thus, the length of scan chains is equal to the number of scan flip-flops divided by the number of scan inputs specified by the designer. Figure 2.2 shows a scan design schematic. Scan design can operate in three modes: normal mode, shift mode, and capture mode. In the normal model, all test signals are turned off, and the scan design operates in the functional configuration. In both shift mode and capture mode, using a test mode signal (TC), all flip-flops can be set to any desired states by shifting those logic states into the scan chain. Similarly, the captured test responses stored in flip-flops can be observed by shifting the contents of the scan chain out.

Figure 2.2 A scan-design schematic

Scan design requires converting the selected sequential elements in the circuit into scan cell. There are more than one possible implementations of a scan cell. The most widely used scan cell is Muxed-D as shown in Figure 2.3. Muxed-D scan cell is composed of a D flip-flop and a multiplexer. The multiplexer uses a scan enable (SE) input to select between the data in (DI) and the scan in (SI).

Figure 2.3 Structure of Muxed-D scan cell

#### 2.2.2. Logic Built-In Self Test

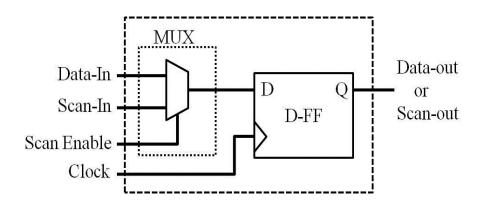

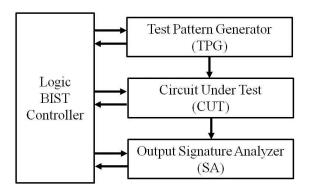

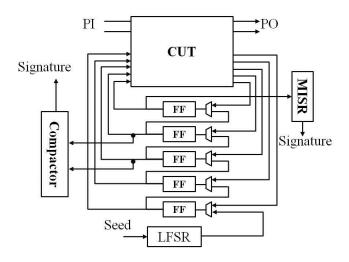

Logic-BIST (Built-In Self Test) refers to a DFT technique which currently be widely used for system debug or field test because it can provide self-test ability and easily to conduct at-speed testing for timing-related defects to obtain high test quality [2].

In Logic-BIST, circuits that generate test patterns and analyze the output test responses are embedded on the chip. Figure 2.4 shows a typical Logic-BIST architecture. An on-chip test pattern generator (TPG) automatically generates test patterns for application to the inputs of the circuit under test (CUT). The output test responses are loaded into a signature analyzer (SA) to examine the response to the test patterns. Specific test control signal are generated by the BIST controller for coordinating the Logic-BIST operation among the TPG, CUT, and SA. The signature analyzer has an output to indicate if the circuit has passed or failed the test.

Figure 2.4 Logic-BIST architecture [2]

In most Logic-BIST architectures, linear feedback shift registers (LFSRs) is used as a TPG because it can generate sequence of good random property with little area overhead. Figure 2.5 shows a structure of four-stage LFSR which is composed of elements (latches or flip flops) and exclusive OR (XOR) gates. The signature analyzers (SAs) are commonly constructed from multiple-input signature registers (MISRs) as shown in Figure 2.6. The MISR is basically an LFSR that has an extra XOR gate at the input of the flip-flop for compressing the output responses of the CUT into the LFSR during shift operation.

Figure 2.5 Four-stage LFSR

Figure 2.6 Four-stage MISR

Logic-BIST can easily apply a large number of test patterns with random property. As a result, more defects, either modeled or un-modeled, can be detected. In addition, Logic-BIST makes it easy to conduct at-speed testing for timing-related defects.

## 2.3. Fault Models

Various defect would be produced in the manufacturing process, it is difficult to generate tests for the real defects. For an accuracy test, it requires accurate description of the circuit behavior containing the physical defects, then, fault modeling is necessary.

There are many fault models related to various defect. In the following sub-sections the currently most popular fault model, the stuck-at fault model and the transition fault model will be introduced.

#### 2.3.1. Stuck-at fault model

A stuck-at fault occurs when a signal line in the circuit is stuck at a constant logic value, either a logic 0 or logic 1, as shown in Figure 2.7. Each signal line can have two types of stuck-at faults: stuck-at-0 and stuck-at-1. For a circuit with n signal line, the total number of stuck-at faults probably exist in the circuit is 2n. This number can be further reduced by fault collapsing technique [1].

Figure 2.7 Stuck-at-0 fault and stuck-at-1 fault

Research has shown that stuck-at fault model can cover many other physical defects within a circuit. However, with the transistor scale continuously shrinking and the operation frequency increasing, other types of defects are beginning to appear, which cannot be covered by stuck-at fault model, such as the transition faults which will be introduced next.

#### 2.3.2. Transition fault model

During the operation of a circuit, logic function and internal signal transition is performed within a specified time limit. For a correct operation the delay of signal transition should not exceed the time limit. In the manufacturing process, certain types of defects may cause the circuit gates to have a higher than normal delay. This un-expected delay can make the signal transition at the gate slower than normal speed. A transition fault will occur when the output of a gate switching from O(1) to O(1) to O(1) takes longer time than normal [3]. If the delay is large enough so as to exceed the specified time limit, its effects can be propagated to the circuit outputs and the circuit will operate with a faulty behavior.

Transition fault model assumes that the delay fault affects only one gate in the circuit. There are two transition faults associated with each gate: a slow-to-rise fault and a slow-to-fall fault [3] as shown in Figure 2.8. A slow-to-rise (slow-to-fall) fault means that the transition from 0 to 1 (1 to 1) will not reach any output within the stipulated time.

Figure 2.8 Slow-to-rise fault and slow-to-fall fault

To detect a transition fault in a circuit, it is necessary to apply two input vectors (V1, V2). The first vector V1 initializes the transition fault in the circuit. The second vector V2 launches the transition and propagates its effect toward the output or some observation points and captures the effects there at a specified time determined by the system clock speed. If the captured response indicates that the logic involved did not transition as expected during the clock cycle time, it is considered to contain a defect. There are two types of transition test method depending on how the transition is launched and captured: launch-off-shift (skewed load) [4] and launch-off-capture (broadside) [5].

#### 2.3.2.1. Launch-off-Shift (LoS)

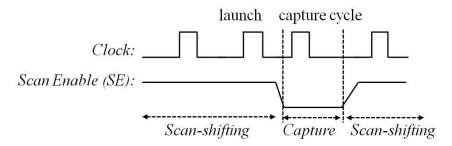

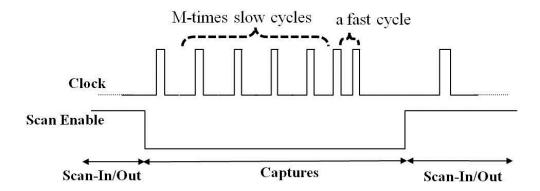

In the launch-off-shift (LoS) method [4], the transition is launched in the last shift of the scan chain load. Figure 2.9 shows the waveform of launch-off-shift. The critical timing is the time from that last shift (or launch) clock to the capture clock. The launch clock is a part of the shift operation and is immediately followed by a fast capture clock. The scan enable signal (SE) is high during the last shift and must go low very quickly to enable response capture at the capture clock edge. Since the capture clock is applied at system frequencies after the launch clock, the scan enable signal which typically drives the scan chains should also switch at system frequencies. This is a limitation because most scan shifting is done at lower frequencies. If the chains are shifted and tested at-speed (at system frequencies), a sophisticated buffer tree or strong clock buffer is required which results in high test cost.

Figure 2.9 Waveform of launch-off-shift

#### 2.3.2.2. Launch-off-Capture (LoC)

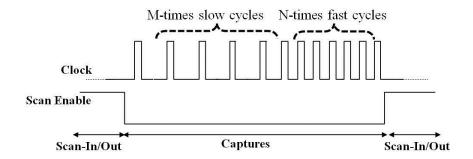

In the launch-off-capture (LoC) method [5], launch clock is separated from the shift operation, a pair of at-speed clocks is applied to launch and capture the transition in functional mode. Figure 2.10 shows launch-off-capture (LOC) method waveforms. This approach relaxes the speed constraint on the scan enable (SE) signal that test pattern scan shifting can be done at slow speeds, and also, the captured test responses can be shifted out slowly in test mode.

Figure 2.10 Waveform of launch-off-capture

#### 2.4. Fault Simulation

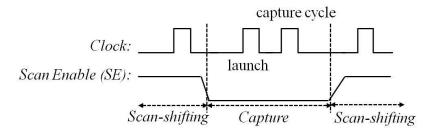

Fault Simulation [1] is used to verify the quality of the test pattern generated for a given fault model. A typical application of fault simulation is shown in Figure 2.11. Fault simulation is executed after the design verification where the verified circuit net-list and verification stimuli (test patterns) are available. A fault list can be generated by the fault simulator for the specified fault model. As each fault is inserted, the fault simulator runs test patterns. If the fault simulation shows that the responses of the faulty circuit are different with the expected responses, fault is detected and will be deleted from the fault list.

At the end of fault simulation, fault coverage is computed to evaluate the quality of the supplied test patterns. Fault coverage is defined as the ratio of the number of detected faults to that of faults in the fault list as shown following.

$$Fault\ Coverage = \frac{Number\ of\ detected\ faults}{Total\ number\ of\ faults}$$

With the help of other program (e.g.: test generator), fault simulation also can be used for test pattern generation if required. As shown in Figure 2.11, if expected fault coverage cannot be achieved through the original test patterns, the undetected faults in the fault list will be applied to a test generator to produce new test vectors.

Figure 2.11 Fault simulation scheme [1]

Because the number of faults simulated for fault detection analysis is very large, fault simulation will spend much greater time than design verification. Many improved approaches have been developed, such as parallel fault simulation [6], deductive fault simulation [7] and concurrent fault simulation [8].

# Chapter 3

# 3. BIST-based Field Rotating Test for Aging-induced fault detection

The continuous scaling down of transistor causes aging phenomena such as HCI, NBTI, TDDB, etc. [9-10]. These aging effects might cause the increase of leakage current or open/short faults which can increase the delay resulting serious reliability problems. This chapter presents a BIST-based rotating test [27] to detect the aging-induced faults for the assurance of the reliability of LSI. The proposed method partitions a set of pre-generated test patterns used to detect the aging induced faults into several subsets, and apply each test subset in one field test chance by rotation. As the number of test patterns applied to each test is decreased, test quality will be lost. In order to improve the test quality, two effective test pattern partition methods are also proposed.

The rest of this chapter is organized as following: Section 3.1 introduces the reliability challenge caused by aging degradation. Section 3.2 shows the field test for aging-induced fault. Section 3.3 describes the concept of the proposed rotating test. In Section 3.4, two pattern partition methods for rotating test and their experimental results will be discussed. Finally, concluding remarks are given in Section 3.5.

# 3.1. Reliability challenges: Aging

Reliable LSI plays an important role in electronic application systems which require high field reliability, such as medical devices, national defense, communications, and aircraft and automobile safety. Reliability of LSI depends on the failure rate during its life [12].

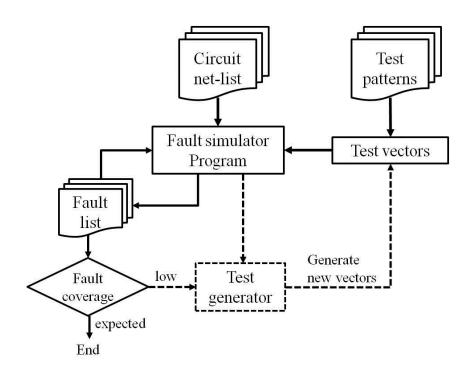

In the LSI life cycle, the failure rate varies with time. It can be modeled by a "bathtub" curve which is widely used in reliability engineering as shown in Figure 3.1. The bathtub curve can be divided into three stages: the "infant mortality" stage with decreasing failure rate, the "normal operation" stage with random failure rate which is near constant, and the "wear-out" stage with increasing failure rate. During LSI's early life the failure rate is very

high due to the manufacturing defects. In practice, the defective LSI or that with a high potential for failure are eliminated in this stage by manufacturing test involves burn-in test or voltage stress test, and etc. When a LSI is shipped to the market, the failure rate is relatively small and constant. Failures are caused by mechanisms inherent in the circuit. In the wear-out stage precedes the end of the LSI life, the probability of failure increases with time.

Figure 3.1 Bathtub curve for LSI's reliability [12]

With the advances in miniaturization of LSI, the feature size of transistor becomes smaller and smaller. The small feature size of the transistors causes aging phenomenon such as Hot-Carrier Injection (HCI), Negative Bias Temperature Instability (NBTI) and Time Dependent Dielectric Breakdown (TDDB) [9, 10]. These aging effects might cause the increase of leakage current or open/short faults which can increase the delay resulting serious reliability problems when the circuit works for a long time or be put in the severe environment, and it should be strictly avoided in high reliability electronic applications.

To guarantee the reliability of LSI, manufacturing test such as burn-in [13] test or stress test [13] are used through applying high temperature or over-voltage supply, aiming to accelerate the failure mechanisms and shorten the time to failure process. The chip with a high potential for failure would likely fail in the infant stage under high frequency or high temperature test. However, due to the small feature sizes and the low operation voltage, excessive burn-in test or stress test would deteriorate the good chips and result in their short lifetime [15].

Recent designs usually set a certain margin (timing) in operational frequency to avoid system failure caused by aging-induced faults [11]. However, timing margin is difficult to be determined by predicting its aging speed in actual use. If a circuit is used more frequently or in higher temperature, then an aging occurs earlier. In addition, the environment where the circuit operates often relates to its aging speed. For example, NBTI-induced delay degradation is significantly accelerated in high temperature. Therefore, the timing margin, which is derived from the worst case estimation, may results in performance degradation.

## 3.2. Field test for aging-induced fault

Field test is a promising approach in guaranteeing the reliability of the circuit through detecting the aging-induced faults [16]. It can be classified into two categories: concurrent test and non-concurrent test.

Concurrent test continuously detects the fault while the circuit is in normal operation mode, thus both the permanent defects (e.g. aging induced defects) and transient defects (e.g. soft errors) can be detected. Self-checking design [17], on-line monitoring [18], signature monitoring techniques [19] and concurrent self-test [20-22] fall into this category. On the other hand, concurrent testing requires large overhead or performance degradation due to special circuit architecture or inserted redundancy in terms of hardware, time, or information. For example, in the self-checking design [17], a complex circuit is partitioned into its constituent functional blocks and adding a checker circuit to check the output of each block, then can detect the concurrent error. The additional checker increases the hardware overhead and also results in performance degradation. Therefore, Concurrent test might not be accepted for general designs widely.

Recently non-concurrent test began to be used for some systems that need high reliability such as automotive, communication, medical, etc. [23-25]. Non-concurrent test is executed at test mode while the system is in idle state, suspended or power-on/off. Therefore, it has less impact on system performance. In addition, usually a built-in self-test (BIST) architecture is adopted to apply test patterns to the circuit under test (CUT) and

analyze the test responses. The impact on area overhead is relatively small. In [26], architecture for field test was proposed which has a BIST-based architecture. Even for non-stop systems, which do not often restart, the systems can run at test mode periodically in field. Thus field test like power-on test would be a promising method to detect aging-induced faults.

The major differences between the field test and the manufacturing test exist in the limitation of test application time and the test opportunity. Due to the requirement of the systems, test application time of the field test is very short, e.g. 10 msec. Therefore, if the number of test patterns is large, it may be impossible to apply all the patterns to the circuit within the required test time. On the other hand, since the BIST-based manufacturing test does not have any technological requirements on test time, its limitation for test application time is less than the field test apart from an economical reason.

Regarding the test opportunity, the power-on test has a peculiar feature. Usually the opportunity of the production test is once just after manufacturing the chip. But since the power-on test is executed every time the system is starting up, its opportunities are more than once. This can be an advantage of the field test as described in the following.

# 3.3. Rotating Test

In this work, a test partition with rotating test [27] is proposed to satisfy the constraint on application time for field test. Figure 3.2 shows the concept.

a. partitioning a given test set

b. applying each subset by rotating

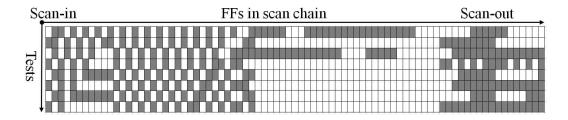

Figure 3.2 Test partitioning and rotating test

If a given test set is too large to apply in one field test (test session), it is needed to reduce the number of test patterns that will cause test quality loss because of the missing test patterns. However, the test patterns that were not applied at the test session can be applied at the next or later test session, because the field test is executed repeatedly every time the system runs at test mode. Therefore, we partition the original test set into some test subsets as illustrated in Figure 3.2(a), and applying one subset for the circuit at one test session. The original test set is partitioned so that the number of test patterns of each subset never exceeds the pattern limit derived from the upper bound of test time, and the number of subsets is as small as possible. Therefore, the number of test patterns of each subset should be  $N_{org}/N_{set}$  or  $N_{org}/N_{set}$ , where  $N_{org}$  and  $N_{set}$  are the number of test patterns of the original test set and the number of the subsets obtained by partitioning, respectively.

All the test patterns of the original test set can be applied through  $N_{set}$  opportunities of the tests. Each subset of test patterns is rotated and applied again at future test sessions, as shown in Figure 3.3(b). We call it "rotating test". In the example of Figure 3.2(b), sub test set  $T_I$  is applied not only at the first test session but also at the  $(i \times N_{set} + I)_{th}$  test session, where i = 1, 2, 3, ...

# 3.4. Pattern Partition algorithms for rotating Test

In rotating test, since the original test set needs to be partitioned into several smaller subsets to meet the test application time requirement. Once an aging-induced fault occurs during the circuit operation it might not be detected immediately until the test is applied that would cause a system failure. To guarantee the reliability, it is necessary to improve the fault coverage for each test subset as far as possible.

In addition, because of the missing test patterns of each subset a fault may not be detected at the followed test session right after it occurs. The fault effect would be propagated during a time interval from its occurrence to the detection. Although a system failure is not caused necessarily as soon as a fault excites, the longer detection time interval would cause the higher probability of a failure appears. Therefore, shorten the detection time interval for each fault is also necessary.

In this work, we proposed two pattern partition algorithms to tackle these problems.

#### 3.4.1. Pattern partition for fault coverage improvement

In this section, the proposed pattern partition algorithm focuses on improving the fault coverage for each test subset as far as possible.

#### 3.4.1.1. Quality of test partition for rotating test

Assume that all the subsets obtained by partitioning have the same size as  $N_{sub}$ . Then there are  $(N_{org}-1)!/(N_{sub}!)N_{set}$  combinations of partition. Even though the original test set is the same, test quality of the rotating test could be generally different depending on partitions. An example is shown below.

Suppose that we partition a test set  $T_{org} = \{t_1, t_2, t_3, t_4, t_5, t_6\}$  which are generated for nine faults  $f_1$  to  $f_9$  into three subset, i.e.:  $N_{org} = 6$ ,  $N_{set} = 3$ . Hence every subset size is 2 calculated from  $N_{org}/N_{set}$ . Each test pattern detects faults as shown in Table 3.1; for example,  $t_1$  detects three faults  $f_1$ ,  $f_2$  and  $f_5$ . We consider a test partition  $P_1$  as shown in Table 3.2(a). The subsets  $T_1$ ,  $T_2$  and  $T_3$  consist of  $\{t_1, t_2\}$ ,  $\{t_3, t_4\}$  and  $\{t_5, t_6\}$ . Individual fault coverage of subsets is 44% (= 4/9) for  $T_1$  and  $T_2$ , and 33% for  $T_3$ , hence the average fault coverage of  $P_1$  is 40.3%. Note that the sum of individual fault coverage for all subsets is more than 100% because faults  $f_5$  and  $f_8$  are detected in two subsets.

Next we consider an alternative test partition  $P_2$  for  $T_{org}$  as shown in Table 3.2(b). In this case, individual fault coverage of subsets are 55%, 55%, 44% for  $T_1$ ,  $T_2$  and  $T_3$ , respectively, and the average fault coverage of partition  $P_2$  is 51.3%, which is larger than that of  $P_1$ . It means that  $P_2$  has higher test quality than  $P_1$  because the field test aims at detecting aging-induced faults unlike the manufacturing test. Even if a fault has not occurred yet in a test session, the fault may occur before the next test session. Although a system failure is not caused necessarily as soon as a fault excites, high test quality would be derived if each fault can be detected by more test sessions frequently. Therefore, it is important for the rotating test to find a test partition so that the average fault coverage of individual subsets is as high as possible.

Table 3.1 Test pattern and detected faults

|         | $f_{I}$ | $f_2$ | $f_3$ | $f_4$ | $f_5$ | $f_6$ | $f_7$ | $f_8$ | $f_9$ |

|---------|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| $t_{I}$ | О       | О     |       |       | О     |       |       |       |       |

| $t_2$   |         | О     | 0     |       |       |       |       |       |       |

| $t_3$   |         |       |       | О     | 0     |       |       | О     |       |

| t 4     |         |       |       |       | 0     | О     |       | О     |       |

| t 5     |         |       |       |       |       |       | О     | О     |       |

| t 6     |         |       |       |       |       |       |       | О     | О     |

Table 3.2 Examples of test partitioning

| (a): test partition P <sub>1</sub> |         |       |       |        |        |       |       |       |       |          |

|------------------------------------|---------|-------|-------|--------|--------|-------|-------|-------|-------|----------|

|                                    | $f_{1}$ | $f_2$ | $f_3$ | $f_4$  | $f_5$  | $f_6$ | $f_7$ | $f_8$ | $f_9$ | Flt.cov. |

| $T_1(t_1,t_2)$                     | О       | 0     | 0     |        | 0      |       |       |       |       | 44%      |

| $T_2(t_3,t_4)$                     |         |       |       | О      | 0      | О     |       | 0     |       | 44%      |

| $T_3(t_5,t_6)$                     |         |       |       |        |        |       | О     | 0     | 0     | 33%      |

|                                    |         |       | (b):  | test p | artiti | on P  | 2     |       |       |          |

|                                    | $f_{1}$ | $f_2$ | $f_3$ | $f_4$  | $f_5$  | $f_6$ | $f_7$ | $f_8$ | $f_9$ | Flt.cov. |

| $T_1(t_1,t_5)$                     | О       | 0     |       |        | 0      |       | О     | 0     |       | 55%      |

| $T_2(t_2,t_4)$                     |         | О     | 0     |        | О      | О     |       | 0     |       | 55%      |

| $T_3(t_3,t_6)$                     |         |       |       | 0      | 0      |       |       | 0     | 0     | 44%      |

#### 3.4.1.2. Problem formulation

From the above observations on test quality in test partitioning, we formulate the following problem:

[Test Pattern Partitioning Problem] Given a test set  $T_{org}$  consisting of  $N_{org}$  patterns and the number of sub test sets  $N_{set}$ , find a partition such that

- (1) the number of test patterns of each sub test set is  $N_{org}/N_{set}$  or  $N_{org}/N_{set}$ , and

- (2) the average fault coverage of individual sub test sets is maximized.

It is easy to satisfy condition (1) because the number of patterns of each subset is uniquely calculated from  $N_{org}$  and  $N_{set}$ . Therefore our discussion focuses on condition (2) below.

#### 3.4.1.3. Partition Algorithm

The algorithm consists of two phases: First is test pattern partitioning, we are going to partitioning a given test set T into  $N_{set}$  sub test sets. Second is test pattern replacement, improving the pattern partitioning by exchanging test patterns between different sub test sets after pattern partitioning.

#### Phase 1: Test pattern partitioning

For pattern partitioning, we first define a terminology. Given test set T, for a couple of test patterns  $t_i$  and  $t_j$ , if they can detect more the same faults,  $t_i$  and  $t_j$  are more similar, the number of these faults is defined as the similarity between  $t_i$  and  $t_j$ . For example of test patterns and faults in Table 3.1,  $t_2$  is a detected fault of  $t_1$ , it also be detected by  $t_2$ . The similarity between  $t_1$  and  $t_2$  is 1. The same as  $t_1$  and  $t_2$ , the similarity between  $t_2$  and  $t_3$  is 0.

In order to maximize average fault coverage of subsets, we need to partition the test set into subsets so that the test patterns in the same subset do not detect the same faults and the different subsets can detect more the same faults as far as possible. The definition of similarity shows that: the smaller similarity of a couple of test patterns, the more different faults can be detected. During the partition, we need to comply with a rule: while distributing a pattern to a subset, the similarity between the new pattern and the patterns which already exist in the subset must be the smallest, in the meantime, the similarity between subsets must be the biggest. If we create a complete table as Table 3.1 shown with respect to test patterns and detected faults, we would have enough information to calculate the similarity. However, it is not efficient on both time and memory usage because it requires fault simulation without fault dropping and a table whose size is  $O(N_{org} \times N_{flt})$  where  $N_{flt}$  is the number of faults of the circuit.

In order to calculate the similarity of test patterns, we employ fault simulation with fault dropping after a fault is detected N-times where N can be set arbitrarily. We consider that for  $N_{set}$  pattern partition,  $N_{set}$ -times fault dropping simulation can get enough information. Below is the outline of the test partitioning algorithm for given test set T and the number of subsets  $N_{set}$ :

Step 1: For *T*, perform fault simulation with fault dropping after *N*-times detection in an arbitrary order of test patterns, and for each fault record the ID of the first *N* patterns which detect the fault.

Step 2: For every pair of test patterns  $t_i$  and  $t_j$  ( $i \neq j$ ), count the number of faults which are detected by the two test patterns simultaneously, and then create a two-dimensional table, as table 3.3.

$t_{1}$  $t_2$  $t_3$  $t_{4}$  $t_{5}$  $t_6$ 1 0 0 1 0 0 0 0  $t_2$ 0  $t_3$ 1 1 1 0 2 1 1 1  $t_4$ 0 1  $t_{5}$

Table 3.3 Similarity of test vector pairs

Step 3: According with the two-dimensional table of similarity, distribute a test pattern into a subset by the following two criteria:

1

1): The similarity between subsets is large.

$t_{6}$

0

0

For  $N_{set}$  pattern partitions, find out  $N_{set}$  test patterns which with the largest similarity between them from the two-dimensional table of similarity, and distribute each of them to different subsets. If M ( $M > N_{set}$ ) test patterns exist, calculate the sum of similarity for  $t_i$  ( $i \in N_{set}$ ) and each  $t_j \in T$  ( $j \neq i$ ), respectively. Then, find out  $N_{set}$  test patterns which with the smaller sum of similarity value, and distribute one of them to a subset.

2): The similarity between test patterns in each subset is small.

While distributing a test pattern to a subset, from the two-dimensional table of similarity, seek one pattern which with the smallest similarity between this pattern and the patterns which already exist in the subset. If more than one pattern is qualified, calculate the sum of similarity for the pending pattern and the patterns already exist in the other subsets. Distribute the pattern which with the biggest sum value of similarity to the subset.

Step 4: According to the two criteria shown in Step 3, perform the partition procedure until all given test patterns are distributed.

In the fault simulation at Step 1, a fault is dropped from the target fault list when the N-times detection pattern for the fault was found. By fault dropping simulation, a detected fault list for every test pattern can be created. We give an example for test patterns in Table 3.1. By comparing the fault list of each pair of test patterns, we create a two-dimensional table for example as table 3.3 to record the similarity of every couple of patterns at Step 2. At Step 3, pattern partition must meet the two formulas simultaneously.

#### Phase 2: Test pattern replacement

After test pattern partitioning, we consider that for a test set T with large number of test patterns, during test pattern partitioning, since fault dropping simulation dropped too much faults information, test pattern partitioning may be not accurate, capability of improvement in fault coverage still exists. Therefore, we perform test pattern replacement for partitioned sub test sets. First, we define a terminology. Given test set T, if fault f is detected by  $t_i$  in T, but not detected by any test vector in T-{ $t_i$ }, f is called an essential fault of  $t_i$  [28]. As the example shown in Table 3.1,  $f_4$  is an essential fault of  $t_3$ .

For a sub test set  $T_{sub}$ , some test patterns can detect more essential faults, we consider that these patterns are important for  $T_{sub}$ , removing one of them affects the fault coverage severely. Some test patterns can't detect anyone essential fault, removing some of them has less impact on fault coverage. We give an example for fault list of a sub test set  $T_I$  in table 3.4. Sub test set  $T_I$  detects 7 faults of all the 9 faults, fault coverage is 77%. Fault  $f_I$  and  $f_S$  are essential faults for  $T_I$ , detected by  $t_I$  and  $t_S$  respectively. Test pattern  $t_S$  detects  $\{f_S, f_S\}$ ,  $t_S$  detects  $\{f_A, f_G\}$ . If remove  $t_S$  and  $t_S$  from  $t_S$  no change in the fault coverage of  $t_S$  from the number of essential faults (#ess) and unessential faults (#uness) detected by each test pattern, we can calculate the number of rank (#rank) by

$$\# rank = \# ess * 2 + \# uness / 2$$

(1)

(Value of #uness/2 is rounded)

Table 3.4 Fault list of a sub test set T<sub>1</sub>

|         | $f_{I}$ | $f_2$ | $f_3$ | $f_4$ | $f_5$ | $f_6$ | $f_7$ | $f_8$ | $f_9$ | Flt.cov(%) | #ess | #uness | #rank |

|---------|---------|-------|-------|-------|-------|-------|-------|-------|-------|------------|------|--------|-------|

| $T_1$   | 0       | 0     | 0     | 0     | 0     | 0     |       | 0     |       | 77         | -    | -      | -     |

| $t_{I}$ | 0       | 0     | 0     |       | 0     |       |       |       |       | 44         | 1    | 3      | 4     |

| $t_2$   |         | 0     | 0     | 0     |       |       |       |       |       | 33         | 0    | 3      | 2     |

| $t_3$   |         |       | 0     |       | 0     |       |       |       |       | 22         | 0    | 2      | 1     |

| t 4     |         |       |       |       | 0     | 0     |       | 0     |       | 33         | 1    | 2      | 3     |

| t 5     |         |       |       | 0     |       | О     |       |       |       | 22         | 0    | 2      | 1     |

For test pattern replacement, we focus on test patterns with lower rank. We consider that a test pattern with low rank in a subset may detect the faults which are not detected by other subsets. For example as Figure 3.3 shows, given 2 subsets  $T_1$  and  $T_2$ ,  $f_2$  and  $f_1$  are undetected faults, respectively. For  $T_1$ , test pattern  $t_2$  has the lowest rank and detects fault  $f_1$ , for  $T_2$ ,  $t_8$  detects  $t_2$  with the lowest rank,  $t_2$  and  $t_8$  are not useful for  $t_1$  and  $t_2$ , but if exchange them,  $t_2$  and  $t_3$  become detectable for  $t_3$  and  $t_4$ .

Therefore, we consider that test pattern replacement can improve the test quality for partitioning method proposed in phase 1. The outline of test pattern replacement is shown as below:

Step1: For every test pattern of subset  $T_i$  ( $i \in N_{set}$ ), count the number of essential faults and unessential faults (all fault information is obtained during fault simulation in phase 1), record the undetected faults by  $T_i$  in a undetected fault list.

Step2: Calculate the rank of every test pattern by expression (1), sort test patterns for each subset by rank from low to high.

Step3: Set a threshold of rank for subset  $T_i$ , compare the undetected fault list of  $T_i$  with the fault list of every test pattern  $t_a$  (#rank of  $t_a$  < threshold) in  $T_j$  ( $j \in N_{set}$ ,  $j \neq i$ ), if  $t_a$  detects more faults which were not detected by  $T_i$ , exchange  $t_a$  and test pattern which with the lowest rank in  $T_i$ .

Step4: Update the undetected fault list for  $T_i$  and sort the test patterns for each subset by rank from low to high again, threshold minus 1. Return to step 3 until threshold=0.

|       | $f_I$   | $f_2$ | $f_3$                | $f_4$ | f5 | <br>#rank |            | $f_I$ | $f_2$ | $f_3$     | $f_4$ | f5 | <br>#rank |

|-------|---------|-------|----------------------|-------|----|-----------|------------|-------|-------|-----------|-------|----|-----------|

| $T_I$ | О       | ×     | o                    | o     | o  | <br>_     | $T_2$      | ×     | o     | o         | o     | o  | <br>-     |

| $t_2$ | О       |       |                      |       |    | <br>1     | ts         |       | О     | О         |       |    | <br>1     |

| t3    |         |       | О                    | 0     |    | <br>1     | t6         |       | 0     |           |       | o  | <br>1     |

| $t_I$ | О       |       | О                    | 0     |    | <br>2     | <i>t</i> 7 |       | o     | o         |       | o  | <br>2     |

| t4    |         |       |                      | 0     | o  | <br>3     | $t_5$      |       |       |           | o     | o  | <br>3     |

|       |         |       | $\frac{1}{\sqrt{1}}$ | 7     |    |           |            |       | 7     | $\bigcap$ |       |    |           |

|       | $f_{I}$ | $f_2$ | $f_3$                | $f_4$ | f5 | <br>#rank |            | $f_I$ | $f_2$ | $f_3$     | $f_4$ | f5 | <br>#rank |

| $T_I$ | o       | o     | o                    | 0     | o  | <br>-     | $T_2$      | 0     | 0     | o         | 0     | o  | <br>-     |

| ts    |         | o     | О                    |       |    | <br>3     | $t_2$      | О     |       |           |       |    | <br>2     |

| t3    |         |       | О                    | o     |    | <br>1     | t6         |       | o     |           |       | o  | <br>1     |

| $t_I$ | o       |       | o                    | o     |    | <br>2     | <i>t</i> 7 |       | o     | o         |       | o  | <br>2     |

| t4    |         |       |                      | o     | o  | <br>3     | t5         |       |       |           | o     | o  | <br>3     |

Figure 3.3 Example for test pattern replacement

#### 3.4.1.4. Experimental results

To demonstrate the effectiveness of the proposed test partition algorithm, we implemented it using C language and performed experiments for *ISCAS'89* and *ITC'99* circuits on a PC with *Core(TM)2 Duo 2.66GHz*, *1.99GB RAM*. In these experiments, we used test patterns generated for single stuck-at faults by an in-house *ATPG* program.

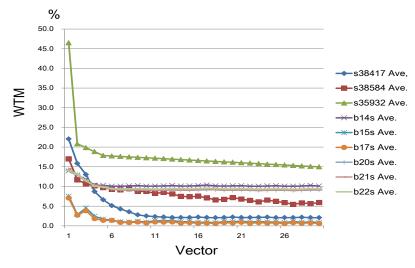

In the first experiment, we performed *Phase 1* of proposed test partition algorithm, partitioned the given compacted test set into eight subsets. Results are given in Figure 3.4 in which we draw the curve of average coverage for some circuits to compare our method with random partitioning. Y axis shows the average fault coverage, X axis shows the different partitions. Different curves show the result for different circuits. The origin of each curve shows the average fault coverage of subsets partitioned randomly, the other points show the average fault coverage of subsets partitioned by proposed method. We set the detection time of dropping simulation from 2 to 10. From the curves, we can see that for proposed partition method, with the detection time for dropping simulation increase, the average coverage increased. After 4 times dropping simulation the curves become gently, while the detection time for dropping simulation is set to 10, for most circuits, the proposed partition method found the best partition.

Figure 3.4 Experimental result for Nset=8

Table 3.5 gives the result of proposed method using 10 times fault dropping simulation. The first two columns show circuit names and the numbers of the given test patterns. The third and forth columns show the average fault coverage of eight subsets for our partitioning and random partitioning, respectively, and the fifth column gives the difference between two methods. These results show that it is meaningful for high quality power-on test to find better partition for the rotating test. The last column of the table gives the computing time in second. Since the algorithm is based on fault dropping simulation, test size, circuit size and detection time for dropping simulation dominate the computing time. Table 3.6 gives the application time of proposed partition while setting the detection time of dropping simulation from 2 to 10. The first column shows the circuit names. From the second column we show the application time while setting the detection time of fault dropping simulation from 2 to 10 respectively. We can see that comparing with 2-times fault dropping simulation, proposed partition by 10-times dropping simulation cost almost 1.5 times application time. Because more accurate similarity table requires more faults information, and more computing time is consumed.

Table 3.5 Experimental result for random partition and the proposed partition with  $N_{set} = 8$

| Circuit | #pattern | Random (%) | Proposed (%) | Diff(%) | Time(s) |

|---------|----------|------------|--------------|---------|---------|

| s5378   | 100      | 72.983     | 75.057       | 2.074   | 1.592   |

| s9234   | 111      | 55.427     | 57.361       | 1.933   | 2.177   |

| s 13207 | 235      | 66.333     | 68.216       | 1.883   | 6.526   |

| s 15850 | 97       | 64.314     | 65.867       | 1.553   | 5.847   |

| s38417  | 87       | 69.534     | 70.586       | 1.052   | 37.57   |

| b17s    | 1250     | 73.336     | 75.334       | 1.999   | 359.459 |

| b20s    | 989      | 63.514     | 65.546       | 2.032   | 65.367  |

| Average | -        | -          | -            | 1.789   | -       |

Table 3.6 Run time

| Circuit | Runtime (sec) |        |        |        |         |         |  |  |  |  |

|---------|---------------|--------|--------|--------|---------|---------|--|--|--|--|

| Circuit | 2times        | 4times | 6times | 8times | 10times | 12times |  |  |  |  |

| s 5378  | 0.75          | 0.92   | 1.08   | 1.33   | 1.59    | 1.81    |  |  |  |  |

| s9234   | 1.18          | 1.37   | 1.61   | 1.92   | 2.18    | 2.39    |  |  |  |  |

| s 13207 | 3.9           | 4.39   | 4.91   | 5.74   | 6.53    | 7.41    |  |  |  |  |

| s 15850 | 2.32          | 2.89   | 3.74   | 4.73   | 5.85    | 7.13    |  |  |  |  |

| s 38417 | 8.7           | 13.86  | 20.37  | 28.53  | 37.57   | 50.2    |  |  |  |  |

| b17s    | 216.64        | 235.83 | 266.09 | 307.63 | 359.46  | 411.81  |  |  |  |  |

| b20s    | 56.53         | 55.42  | 57.6   | 63.73  | 65.37   | 70.35   |  |  |  |  |

In the second experiment, we performed test pattern replacement for subsets which partitioned by the proposed test pattern partitioning method using 10 times fault dropping simulation, results are given in Table 3.7. The third and forth column shows the average fault coverage of eight subsets for the proposed test pattern partitioning method and performed test pattern replacement, respectively, and the fifth column gives the difference between two methods. These results show that test pattern replacement improved the average fault coverage of subsets after the test pattern partitioning.

Table 3.7 Experimental result for the proposed partition algorithm with  $N_{set} = 8$

|         |          | Test pattern partitioning algorithm |                                  |                |  |  |  |  |  |  |

|---------|----------|-------------------------------------|----------------------------------|----------------|--|--|--|--|--|--|

| Circuit | #pattern | Phase 1: Pattern partitioning (%)   | Phase 2: Pattern replacement (%) | Difference (%) |  |  |  |  |  |  |

| s5378   | 100      | 75.057                              | 75.576                           | 0.519          |  |  |  |  |  |  |

| s9234   | 111      | 57.361                              | 58.128                           | 0.767          |  |  |  |  |  |  |

| s13207  | 235      | 68.216                              | 69.25                            | 1.034          |  |  |  |  |  |  |

| s15850  | 97       | 65.867                              | 66.614                           | 0.747          |  |  |  |  |  |  |

| s38417  | 87       | 70.586                              | 71.013                           | 0.427          |  |  |  |  |  |  |

| b17s    | 1250     | 75.334                              | 76.11                            | 0.776          |  |  |  |  |  |  |

| b20s    | 989      | 65.546                              | 66.297                           | 0.751          |  |  |  |  |  |  |

| Average | -        | -                                   | -                                | 0.717          |  |  |  |  |  |  |

#### 3.4.2. Pattern partition for reducing the probability of failure appearance

For rotating test, since the original test set needs to be partitioned into several smaller subsets to meet the test application time requirement. Fault coverage of each subset would be reduced due to the missing test patterns so that many faults cannot be detected in test sessions and the detection time interval of faults becomes longer. Although a system failure is not caused necessarily as soon as a fault excites, the longer detection time interval would cause the higher probability of a failure appears. Therefore, reduce the probability of failure caused by faults is required for guaranteeing the system reliability.

#### 3.4.2.1. Failure Appearance Probability (FAP)

We define *Failure Appearance Probability (FAP)* as the probability of a failure appears during system operation. The computation for *FAP* is based on two assumptions: 1) no fault occurs during test application; 2) failure caused by a fault can be avoided when the fault is detected.

To compute the FAP, we assume that executing field test per unit time. Suppose that existence probability of an aging-induced fault during unit time is p and the probability of failure caused by the fault in a time unit is q. Hence, the FAP of a fault per unit time is pq. If the fault also cannot be detected in the next test session, the detection time interval becomes two units of time. The existence probability of the fault is 2p, and failure would be

caused by the faults more easily since the detection time interval becomes longer. Therefore, FAP of the fault undetected at two test session is  $2^2pq$ . We give an example to explain the FAP computation for rotating test below.

Suppose that a given test set can be partitioned into 4 subsets  $\{T_1, T_2, T_3, T_4\}$  and rotate them in field. Consider a fault f detected by  $T_1$ , if f can be detected by  $T_2$  but undetected by  $T_3$  and  $T_4$ . During the period between  $T_1$  and  $T_2$ , the time interval is 1 so that the failure rate of f is pq. After  $T_2$  is applied, f will be undetected in three consecutive test sessions until the next test  $T_1$  is applied, so that the detection time interval is 3 and the failure rate of fault f during the period between test  $T_2$  and the next  $T_1$  is  $3^2pq$ . If we assume that pq=1, the FAP of fault f during a rotating test is the sum of the FAP in different test sessions divided by the number of subsets that is (1+9)/4=2.5. For all faults detected by  $T_1$ , FAP can be formulated as:

$$FAP(T_1) = pq * [(\Delta f_{1,1} - \Delta f_{1,2}) + 4(\Delta f_{1,2} - \Delta f_{1,3}) + 9(\Delta f_{1,3} - \Delta f_{1,4}) + 16\Delta f_{1,4}]$$

$$= pq(\Delta f_{1,1} + 3\Delta f_{1,2} + 5\Delta f_{1,3} + 7\Delta f_{1,4})$$

(1)

Where,  $\Delta f_{I,1}$  denotes the fraction of faults detected by  $T_I$ ,  $\Delta f_{I,2}$  denotes the fraction of faults detected by  $T_I$  missed by  $T_2$  and  $T_3$ , and  $\Delta f_{I,4}$  denotes the fraction of faults detected by  $T_I$  missed by  $T_2$ ,  $T_3$  and  $T_4$  (only detected by  $T_I$ ). Note that (1) only gives the failure rate for the case that faults detected by  $T_I$ . The general case for computing the failure rate for the faults detected by  $T_I$  can also use the same equation (1) where  $\Delta f_{i,j}$  becomes the fraction of faults detected by  $T_I$  and undetected by other subsets  $T_{I+I}...T_{I-I}$  during a rotating test. For the case that a given test set is partitioned into 4 subsets, the failure rate for rotating test can be expressed as:

$$FAP(P:4 | \{T_1, T_2, T_3, T_4\}) = \frac{pq}{4} [FAP(T_1) + FAP(T_2) + FAP(T_3) + FAP(T_4)]$$

(2)

Where  $FAP(T_i)$  is the FAP of the faults detected by  $T_i$ . We can write the FAP for the rotating test with 4 subsets as:

$$FAP(P:4|\{T_1,T_2,T_3,T_4\}) = \frac{pq}{4} \sum_{i=1}^{4} \sum_{j=1}^{4} (2j-1)\Delta f_{i,j}$$

(3)

The FAP calculation can be extended to the rotating test with  $N_{set}$  subsets by rewriting (3) into (4).

$$FAP(P:N_{set} | \{T_1, T_2, ... T_{N_{set}}\}) = \frac{pq}{N_{set}} \sum_{i=1}^{N_{set}} \sum_{j=1}^{N_{set}} (2j-1)\Delta f_{i,j}$$

(4)

From the above discussions, we can observe that the FAP of rotating test is depending greatly on test partitioning. We show an example below. Suppose that we need to partition a test set into 4 subsets  $\{T_I, T_2, T_3, T_4\}$ , a fault f can be detected by two patterns  $t_1$  and  $t_2$ . Let's distribute  $t_1$  and  $t_2$  to subsets in three cases: 1) distribute  $t_1$  and  $t_2$  to the same subset  $T_1$ ; 2): distribute  $t_1$  to subset  $T_1$  and  $t_2$  to subset  $T_2$ ; 3) distribute  $t_1$  to subset  $T_1$  and  $t_2$  to subset  $T_3$ ; In case 1, fault f can only be detected by subset  $T_1$ , the detection time interval is 4. If we suppose that the factor pq in equation (1) is 1, hence average FAP of f is 16/4=4. In case 2, fault f can only be detected by two consecutive subsets  $T_1$  and  $T_2$ , however it will be missed at the next two consecutive subsets  $T_3$  and  $T_4$  so that the detection intervals are 1 and 3, respectively. Average FAP of f is (1+9)/4=2.5. In case 3, fault f is detected by  $T_1$  and  $T_3$ , missed at the  $T_2$  and  $T_4$ . The detection interval is 2, and the average FAP of f is (4+4)/4=2. Note that distributing test patterns  $t_1$  and  $t_2$  in case 3 can derive the minimum FAP.

The above example shows that for a fault f detected by N (N>1) test patterns, evenly distributing the N test patterns to subsets can minimize the FAP for rotating test. However, in general, it is difficult or even impossible to have an optimum partition on the original test sets for rotating test so that the detection patterns of every fault can be distributed evenly. This can be seen by an example. Suppose that a given test set is partitioned into 8 subsets and we have 4 test patterns  $\{t_1, t_2, t_3, t_4\}$  for 3 faults  $\{f_1, f_2, f_3\}$ . Fault  $f_1$  is detected by 4 test patterns,  $f_2$  is detected by  $f_1$  and  $f_3$  and  $f_3$  is detected by  $f_1$  and  $f_2$ . For fault  $f_1$ , we distribute all its test pattern evenly with  $f_1 = \{t_1\}$ ,  $f_2 = \{t_2\}$ ,  $f_3 = \{t_3\}$  and  $f_4 = \{t_4\}$ . For fault  $f_4 = \{t_4\}$  are distributed evenly. However for fault  $f_3$ , we

cannot find a way to assign  $t_1$  and  $t_2$  so that the FAP of  $f_3$  is minimized while not increasing the FAP of other faults.

In [29], a genetic algorithm (GA) based test partition method is proposed that can find a near optimal partitioning that detection test patterns of all faults are partitioned as evenly as possible. However, since the GA-based test partition method distributes each test pattern to only one subset so that the faults detected by only one test pattern can be detected at one test session but undetected at the other test sessions during one rotating, thus the FAP cannot be reduced. The FAP of these faults would be very high if there are too many test sessions during a rotating test. Therefore, for minimizing the FAP of rotating test, we need to find a partitioning that can reduce the FAP for the faults detected by only one pattern. In the next section we formulate a problem for test partitioning and propose a new test partition approach for rotating test aiming at the FAP minimization.

#### 3.4.2.2. Problem formulation

From the above discussions on *FAP* in test partitioning for rotating test, we formulate the following problem:

[Test Pattern Partitioning Problem] Given a test set  $T_{org}$  consisting of  $N_{org}$  patterns and the number of test patterns of each subset  $N_{test}$ . Note that  $T_{org}$  can detect all the faults of circuit. Then distribute test patterns in  $T_{org}$  into subsets. The objective is to minimize the FAP of a rotating test with obtained subsets.

For the problem solved in sub-section 3.4.1, the number of subsets is determined from  $N_{org}$  and  $N_{test}$ . Unlike that problem, because this formulation allows a test pattern of  $T_{org}$  to be included in more than one subset, the number of obtained subsets may be larger.

#### 3.4.2.3. Partition algorithms

The partitioning algorithm focuses on two points for failure rate reduction. 1: distribute the detection test patterns of every fault as evenly as possible; 2: for the faults detected by only one pattern, repeatedly distribute the detection pattern to different subsets.

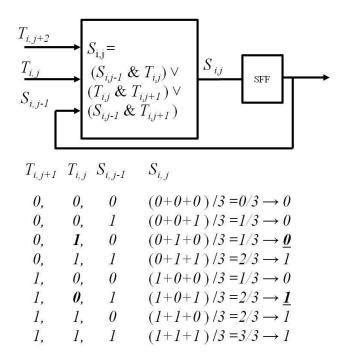

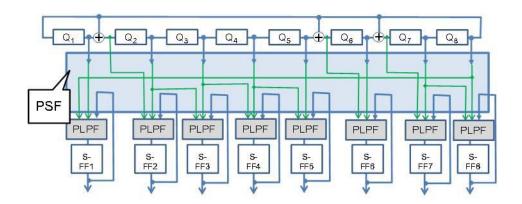

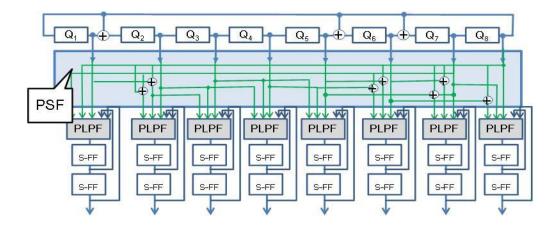

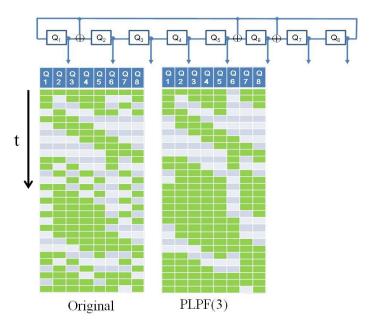

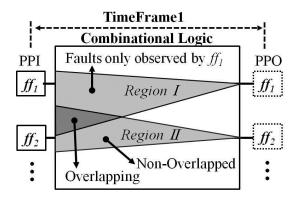

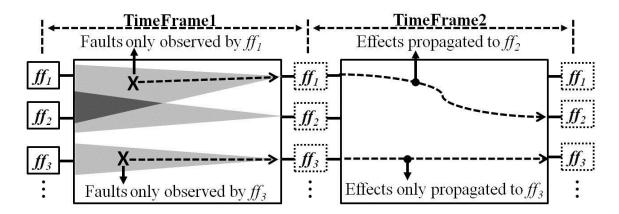

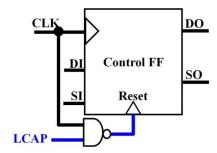

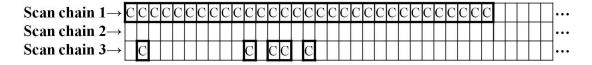

In order to evenly distribute the detection test patterns of faults, every time distributing a new test pattern to a subset we need to select the pattern which can detect more faults only detected by the previous subsets. For example: select a new pattern  $t_{new}$  is distributed to subset  $T_i$ ,  $t_{new}$  should detect more faults undetected by other patterns in  $T_i$  but (only) detected by  $T_i...T_{i-1}$ . In this way, the faults that were detected in the previous test session but undetected in the followed test sessions can be detected by applying the new subset. Hence the FAP of the faults can be reduced.