# Structure-based capacitance modeling and power loss analysis for the latest high-performance slant field-plate trench MOSFET

Kenya Kobayashi<sup>1\*</sup>, Masaki Sudo<sup>1</sup>, and Ichiro Omura<sup>2</sup>

<sup>1</sup>Graduate School of Engineering, Kyushu Institute of Technology, Kitakyushu, Fukuoka 804-8550, Japan

<sup>2</sup>Graduate School of Life Science and Systems Engineering, Kyushu Institute of Technology, Kitakyushu, Fukuoka 808-0196, Japan

\*E-mail: kenya.k.2050@gmai.com

Field-plate trench MOSFETs (FP-MOSFETs), with the features of ultralow on-resistance and very low gate-drain charge, are currently the mainstream of high-performance applications and their advancement is continuing as low-voltage silicon power devices. However, owing to their structure, their output capacitance ( $C_{\rm oss}$ ), which leads to main power loss, remains to be a problem, especially in megahertz switching. In this study, we propose a structure-based capacitance model of FP-MOSFETs for calculating power loss easily under various conditions. Appropriate equations were modeled for  $C_{\rm oss}$  curves as three divided components. Output charge ( $Q_{\rm oss}$ ) and stored energy ( $E_{\rm oss}$ ) that were calculated using the model corresponded well to technology computer-aided design (TCAD) simulation, and we validated the accuracy of the model quantitatively. In the power loss analysis of FP-MOSFETs, turn-off loss was sufficiently suppressed, however, mainly  $Q_{\rm oss}$  loss increased depending on switching frequency. This analysis reveals that  $Q_{\rm oss}$  may become a significant issue in next-generation high-efficiency FP-MOSFETs.

## 1. Introduction

Power semiconductor devices are contributing to the reduction of energy consumption in many applications from very small mobile devices to very large power electronics systems. Among these, low-voltage power MOSFETs (LV-MOSFETs), which are generally classified into those with rated voltage in the range from 12 to 250 V, are applied in various circuits such as DC-DC converters of distributed power supply systems and three-phase inverters of motor drives. For LV-MOSFETs, historically, planar gate double-diffused MOSFETs (D-MOSFETs) and trench gate MOSFETs (U-MOSFETs) were developed in the 1970s and the 1980s, respectively, 1) and they are currently used as matured low-cost devices. As great advancements of LV-MOSFET in terms of performance, field-plate trench MOSFETs (FP-MOSFETs)<sup>2-10)</sup> and superjunction trench MOSFETs (SJ-MOSFETs)<sup>11-17)</sup> were devised in the 1990s and commercialized in the 2000s. In both types of MOSFETs, specific on-resistance  $(R_{ON}A)$  could be drastically reduced with a high breakdown voltage  $(V_B)$  maintained. In particular, the FP-MOSFETs achieved not only ultralow R<sub>ON</sub>A but also very low reverse transfer capacitance ( $C_{rss}$ ) and gate-drain charge ( $Q_{gd}$ ) owing to the shielded-gate structure. Therefore, the FP-MOSFETs are currently the mainstream of high-performance applications and their advancements are continuing.

In general power conversion applications, power loss occurs during both conduction and switching operation. The power loss consists of the following components: gate drive loss ( $P_{\rm GD}$ ), conduction loss ( $P_{\rm CON}$ ), turn-on loss ( $P_{\rm SW(on)}$ ), turn-off loss ( $P_{\rm SW(off)}$ ), diode reverse recovery charge ( $Q_{\rm rr}$ ) loss ( $P_{\rm Qrr}$ ), and output charge ( $Q_{\rm oss}$ ) loss ( $P_{\rm Qoss}$ ). Among these, it is expected that  $P_{\rm GD}$  can be reduced by circuit control and gate driver technologies such as very low impedance and very high current gate drive. Low-recovery-charge Shottky barrier diodes (SBD) can improve  $P_{\rm Qrr}$ . Regarding FP-MOSFETs, it is obvious that there is a potential to reduce  $P_{\rm CON}$ ,  $P_{\rm SW(on)}$ , and  $P_{\rm SW(off)}$  drastically, and several power loss analysis has been reported so far. However, owing to their structure, the output capacitance ( $C_{\rm oss}$ ) which leads to  $P_{\rm Qoss}$  is a significant issue, especially in the case of megahertz switching. Which leads to  $P_{\rm Qoss}$  is a significant issue, especially in the case of

In this paper, we describe a structure-based capacitance model of the FP-MOSFET, which was proposed in a related report,<sup>32)</sup> to estimate power loss under various conditions. In the modeling, we consider in detail the components of capacitance for both the conventional D-MOSFETs and the latest slant FP-MOSFETs, and provide additional more comprehensive explanations of the derivation of equations. The accuracy of the model is validated by comparing its results with those of technology computer-aided design (TCAD)

simulation. For more comprehensive validation data, we present not only  $C_{\rm oss}$  curves and  $Q_{\rm oss}$  curves but also  $C_{\rm rss}$  curves and switching waveforms. By utilizing the proposed model, we expect that it is greatly useful for predicting the device performance of next-generation FP-MOSFETs.

## 2. Device structures, parameters, and basic characteristics

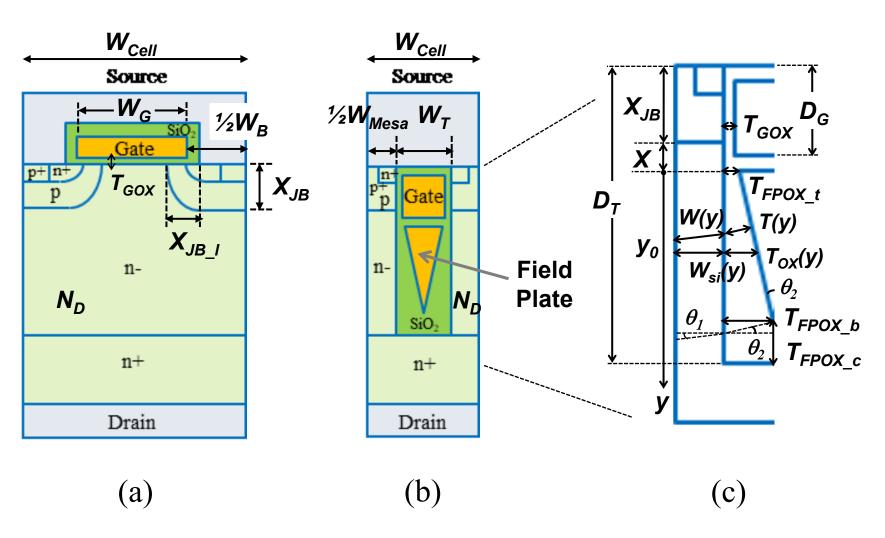

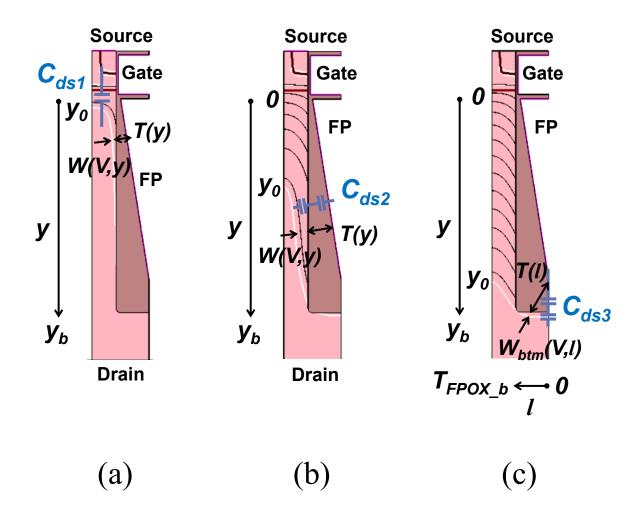

Figures 1(a) and 1(b) show schematic cross sections and representative structural parameters of a conventional D-MOSFET and a slant FP-MOSFET. Figure 1(c) shows comprehensive structural parameters of the FP-MOSFET to describe the capacitance model. The FP-MOSFET has a field plate inside a trench and the field plate is connected to a source electrode. In the off-state, an electric field in the drift region between trenches is reduced by the field-plate effect through a thick oxide. Therefore, despite the higher doping concentration in the drift layer than in the D-MOSFET, high  $V_B$  and low  $R_{ONA}$  can be obtained at the same time. Moreover, as one of the latest FP-MOSFET, a slant field-plate structure has been devised and its superior  $R_{ONA}-V_B$  characteristics have been reported. <sup>33-36</sup> In the slant field-plate structure having a gradient thick oxide, the electric field is distributed more uniformly in the vertical direction, and the structure can achieve high MOSFET performance.

In this study, we chose a 100-V-class MOSFET as a motive device, which is applied to, e.g., high-efficiency switching-mode power supply and a high-current motor drive inverter circuit. The capacitance model can be described by structural parameters such as detailed cell structure dimensions and impurity doping concentrations, as shown in Table I. It does not require any measurement of electrical characteristics. Physical constants used in the modeling are shown in Table II. As shown in Table I, the unit cell width ( $W_{Cell}$ ) of the FP-MOSFET is set to 2.6 µm, which is smaller than that of D-MOSFET (6.0 µm). Despite its smaller  $W_{Cell}$ , it has a drift layer concentration ( $N_D$ ) that is ten times higher than that of a conventional one.

Before the capacitance modeling, we confirmed the basic characteristics of both MOSFETs using the TCAD simulator named Sentaurus Device.<sup>37)</sup> As a result, the FP-MOSFET showed a sufficient  $V_B$  of 110.1 V and an ultralow RonA of 32.8 m $\Omega$ ·mm<sup>2</sup>, which was approximately one-sixth of that of the D-MOSFET, as shown in Table III. Moreover, in the FP-MOSET, a very small  $Ron \cdot C_{rss}$ , which approximately one-twentieth of that of the D-MOSFET, was confirmed. These indicate good features of the FP-MOSFET. However,  $Ron \cdot Q_{oss}$  is still high. Therefore, the capacitance modeling especially for  $C_{oss}$ , which requires the analysis  $P_{Qoss}$ , is important.

## 3. Description of capacitance modeling

Several analytical capacitance models for different vertical power device structures have been reported, e.g., those for silicon D-MOSFETs,<sup>38)</sup> silicon U-MOSFETs,<sup>39-41)</sup> and SiC D-MOSFETs.<sup>42)</sup> In those reports, however, since the  $C_{\rm oss}$  components of D-MOSFETs and U-MOSFETs are relatively simple, those modeling methods are not applied to complex-structured FP-MOSFETs.

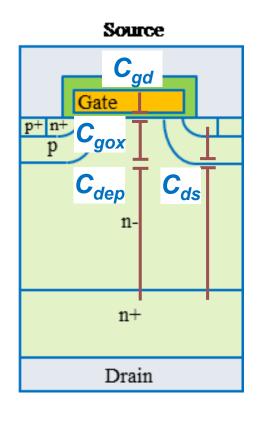

#### 3.1 D-MOSFET

Figure 2(a) shows the components of  $C_{oss}$  in the D-MOSFET.  $C_{oss}$  is simply expressed as

$$C_{oss\_DMOS} = C_{ds} + C_{gd}. (1)$$

The drain-source capacitance  $C_{ds}$  is a pn-junction capacitance and it is varied by the drain-source voltage  $V_{ds}$ .

$$C_{ds} = \sqrt{\frac{qN_D \varepsilon_{Si} \varepsilon_0}{2(V_{ds} + V_{bi})}} \cdot \frac{(W_B + 2X_{JB\_l})}{W_{Cell}}$$

(2)

Here, q is the elementary charge,  $\varepsilon_{Si}\varepsilon_{0}$  is the permittivity of Si,  $W_{B}$  is the p-base width, and  $X_{JB\_1}$  is the lateral expansion length of the p-base junction. The built-in potential  $V_{bi}$  is given by

$$V_{bi} = \frac{kT}{a} \ln \frac{N_A N_D}{n_i^2},\tag{3}$$

where k is Boltzmann's constant, T is the absolute temperature,  $n_i$  is the intrinsic carrier density of Si, and  $N_A$  is a p-base layer concentration.

The gate—drain capacitance  $C_{gd}$  is a series connection of a gate oxide capacitance  $(C_{gox})$  and a depletion layer capacitance  $(C_{dep})$ . Since  $C_{rss}$  is equal to  $C_{gd}$ ,  $C_{rss}$  is written as

$$C_{rss} = C_{gd} = \frac{c_{gox}c_{dep}}{c_{gox} + c_{dep}}. (4)$$

Furthermore,  $C_{gox}$  and  $C_{dep}$  are expressed as

$$C_{gox} = \frac{\varepsilon_{OX}\varepsilon_0}{T_{gox}} \cdot \frac{(W_G - 2X_{JB\_l})}{W_{Cell}},\tag{5}$$

$$C_{dep} = \frac{\varepsilon_{Sl}\varepsilon_0}{W_{d,mos}} \cdot \frac{(W_G - 2X_{JB\_l})}{W_{Cell}},\tag{6}$$

where  $\varepsilon_{OX}\varepsilon_{0}$  is the permittivity of SiO<sub>2</sub>,  $T_{gox}$  is the gate oxide thickness, and  $W_{G}$  is the gate width.  $W_{d\_mos}$  is the depletion layer width beneath the gate electrode and is given by<sup>43)</sup>

$$W_{d\_mos} = \frac{\varepsilon_{Si} T_{gox}}{\varepsilon_{OX}} \left( \sqrt{\frac{2V_{ds} \varepsilon_{OX}^2 \varepsilon_0}{q N_D \varepsilon_{Si} T_{gox}^2} + 1} - 1 \right). \tag{7}$$

By substituting Eqs. (5)–(7) into Eq. (4), the  $C_{rss}$  model can be obtained.

$$C_{rss\_DMOS} = C_{gd} = \frac{\varepsilon_{OX}\varepsilon_{0}}{\sqrt{\frac{2V_{dS}\varepsilon_{OX}^{2}\varepsilon_{0}}{qN_{D}\varepsilon_{Si}} + T_{gox}^{2}}} \cdot \frac{W_{G} - 2X_{JB\_l}}{W_{Cell}}$$

(8)

Finally, by substituting Eqs. (2), (3), and (8) into Eq. (1), the  $C_{oss}$  model can be obtained.

$$C_{OSS\_DMOS} = \sqrt{\frac{qN_D \varepsilon_{Si} \varepsilon_0}{2\left(V_{dS} + \frac{kT}{q} \ln \frac{N_A N_D}{n_l^2}\right)}} \cdot \frac{W_B + 2X_{JB\_l}}{W_{Cell}} + \frac{\varepsilon_{OX} \varepsilon_0}{\sqrt{\frac{2V_{dS} \varepsilon_{OX}^2 \varepsilon_0}{qN_D \varepsilon_{Si}} + T_{gox}^2}} \cdot \frac{W_G - 2X_{JB\_l}}{W_{Cell}}$$

(9)

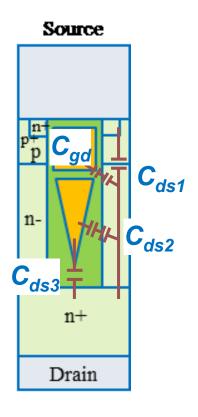

#### 3.2 FP-MOSFET

As an approach to capacitance modeling in the complex FP-MOSFET structure, we consider the four components of  $C_{oss}$ , as shown in Fig. 2(b).  $C_{oss}$  is simply expressed as

$$C_{oss\_FPMOS} = C_{ds1} + C_{ds2} + C_{ds3} + C_{gd}.$$

(10)

Here,  $C_{ds1}$  is the depletion layer capacitance of the pn-junction,  $C_{ds2}$  is a series connection of a field-plate oxide capacitance and a depletion layer capacitance along the trench side wall, and  $C_{ds3}$  is the trench bottom capacitance including the field-plate oxide and depletion layers. In the FP-MOSFET, however,  $C_{gd}$  is negligible in the case of  $C_{oss}$  calculation, because the area of the parallel-plate capacitor is usually very small for optimized cell design.

Figures 3(a)–3(c) show the TCAD-simulated FP-MOSFET half-cell structures, which show the  $V_{\rm ds}$  dependence of equal-potential contours. The potential contours of 5 V intervals and the depletion layer boundaries are shown as black and white lines, respectively. In each figure, the dominant capacitance components are  $C_{\rm ds1}$ ,  $C_{\rm ds2}$ , and  $C_{\rm ds3}$ , respectively.

**3.2.1 pn-Junction capacitance.** In the region of  $C_{ds1}$  [Fig. 3(a)], the depletion layer of the pn-junction extends down to the vertical direction with increasing  $V_{ds}$ . However, the capacitance width in the lateral direction decreases because of the expansion of another depletion layer along the trench side wall caused by the field-plate effect. It is considered that this pn-junction capacitance  $C_j$  is divided into  $C_{j0}$  and  $C_{j1}$  according to the  $V_{ds}$  condition.

$$C_{ds1} = C_j = \begin{cases} C_{j0}, \ V_{ds} < 1(V) \\ C_{j1}, \ V_{ds} \ge 1(V) \end{cases}$$

(11)

$C_{j0}$  is the capacitance at an early voltage including the  $V_{bi}$ .  $C_{j0}$  is modeled similarly to Eq. (2) for the  $C_{ds}$  of the D-MOSFET.

$$C_{j0} = \sqrt{\frac{qN_D \varepsilon_{Si} \varepsilon_0}{2(V_{ds} + V_{bi})}} \cdot \frac{W_{Mesa}}{W_{Cell}},\tag{12}$$

where  $W_{\text{Mesa}}$  is the mesa width.

Before  $C_{j1}$  modeling, we additionally explain some parameters shown in Fig. 1(c).  $\theta_2$  is

the angle of the field plate and it given by

$$\theta_2 = \tan^{-1} \left( \frac{T_{FPOX\_b} - T_{FPOX\_t}}{D_T - X_{IB} - X - T_{FPOX\_c}} \right), \tag{13}$$

where  $T_{\text{FPOX\_t}}$  and  $T_{\text{FPOX\_b}}$  are the lateral field-plate oxide thicknesses at top and bottom positions, respectively,  $T_{\text{FPOX\_c}}$  is the vertical field-plate oxide thickness of the center of the trench bottom,  $D_{\text{T}}$  is the trench depth, and X is the length between the p-base layer depth and the horizontal position of the top of the field plate.

$\theta_1$  is the direction of the electric line of force and it is given by

$$\theta_1 = \tan^{-1} \left( \frac{\varepsilon_{Si}}{\varepsilon_{OX}} \tan \theta_2 \right). \tag{14}$$

T(y) and W(y) are used to calculate the charge densities in the field-plate oxide and the silicon mesa region, respectively, and are given by

$$T(y) = T_{OX}(y)\cos\theta_2,\tag{15}$$

$$W(y) = \frac{W_{Si}(y)}{\cos \theta_1},\tag{16}$$

where y is the depth from the top of the field plate,  $T_{OX}(y)$  is the field-plate oxide thickness at the position y and  $W_{Si}(y)$  is the depletion layer width of the mesa region along the slant field plate at the position y.  $T_{OX}(y)$  is expressed as

$$T_{OX}(y) = \frac{T_{FPOX\_b} - T_{FPOX\_t}}{D_T - X_{IB} - X - T_{FPOX\_c}} y + T_{FPOX\_t}.$$

(17)

Although W(y) varies with  $V_{ds}$ , it has to be considered that  $V_{ds}$  is shared by the voltage of the field-plate oxide  $(V_{OX})$  and the voltage of the silicon mesa  $(V_{Si})$ . The relationship between  $V_{OX}$ ,  $V_{Si}$ , T(y), and W(y) are expressed as

$$V_{ds} = V_{Si} + V_{OX}, \tag{18}$$

$$V_{Si} = \frac{1}{2} E_{Si} W(y), \tag{19}$$

$$V_{OX} = E_{OX}T(y), (20)$$

$$\varepsilon_{Si} E_{Si} \cos \theta_1 = \varepsilon_{OX} E_{OX} \cos \theta_2, \tag{21}$$

$$E_{Si} = \frac{qN_D}{\varepsilon_{Si}\varepsilon_0}W(y), \tag{22}$$

where  $E_{Si}$  and  $E_{OX}$  are the electric field strengths of the silicon mesa region and field-plate oxide region, respectively. W(y) is derived by solving Eqs. (18)–(22). Since y varies with  $V_{ds}$ , W(y) is exactly expressed as  $W(V_{ds}, y)$  and can be described as

$$W(V_{ds}, y) = -\frac{\varepsilon_{Si}\cos\theta_1}{\varepsilon_{OX}\cos\theta_2} \cdot T(y) + \sqrt{\left(\frac{\varepsilon_{Si}\cos\theta_1}{\varepsilon_{OX}\cos\theta_2} \cdot T(y)\right)^2 + \frac{2\varepsilon_{Si}\varepsilon_0}{qN_D} \cdot V_{ds}}.$$

(23)

$C_{i1}$  includes the effect of capacitance width decrease by  $W(V_{ds}, y)$  and is described as

$$C_{j1} = \frac{\varepsilon_{Si}\varepsilon_0}{y_0 + X} \cdot \frac{W_{Mesa} - 2W(V_{ds}, y)}{W_{Cell}},$$

(24)

where  $y_0$  is the depletion layer depth of the center of the mesa.

**3.2.2 Oxide and depletion layer capacitance along field plate.** In the region of  $C_{ds2}$  [Fig. 3(b)], the initial  $C_{ds2}$  is nearly equal to the field-plate oxide capacitance  $C_{OX}$ . With increasing  $V_{ds}$ , the mesa region is depleted linearly owing to the relation  $y_0 \propto V_{ds}$  in the vertical direction, and the lateral depletion width under the position of  $y_0$  expands gradually by  $W(V_{ds}, y)$ . Thus,  $C_{ds2}$  is divided into two components according to the  $V_{ds}$  condition.

$$C_{ds2} = \begin{cases} C_{OX} & , V_{ds} < 1(V) \\ C_{FP}(V_{ds}), V_{ds} \ge 1(V) \end{cases}$$

(25)

Cox is provided by integrating field-plate oxide thickness in the depth direction.

$$C_{OX} = \frac{2(D_T - X_{JB} - X - T_{FPOX\_c})\varepsilon_{OX}\varepsilon_0}{W_{Cell}(T_{FPOX\_b} - T_{FPOX\_t})} \cdot ln \frac{T_{FPOX\_b}}{T_{FPOX\_t}}$$

(26)

At an arbitrary position y, the charge, which is across the field plate and the depletion layer in the mesa region, is defined as dQ. Differential equation of dQ expresses a voltage change of the drain–source electric charge and described as

$$\frac{dQ}{dV} = qN_D \frac{d}{dV}W(V_{ds}, y). \tag{27}$$

The voltage dependence capacitance  $C_{FP}(V_{ds})$  is provided by integrating Eq. (27) from  $y_0$  to  $y_b$ , which is the end of the depletion layer and is described as

$$C_{FP}(V_{ds}) = \frac{2 \cdot \int_{y_0}^{y_b} q N_D \frac{d}{dV} (W(V_{ds}, y)) dy}{W_{Call}}.$$

(28)

Finally, by substituting Eqs. (15), (17), and (23) into Eq. (28),  $C_{FP}(V_{ds})$  can be obtained.

$$C_{FP}(V_{ds}) = \frac{2}{W_{Cell}} \int_{y_0}^{y_b} \frac{\varepsilon_{Si}\varepsilon_0}{\sqrt{\frac{\varepsilon_{Si}^2 \cos^2 \theta_1 \left[ T_{FPOX\_t} + \frac{y(T_{FPOX\_t} - T_{FPOX\_b})}{X_{JB} + X + T_{FPOX\_b} - D_T} \right]^2 + \frac{2\varepsilon_{Si}\varepsilon_0 V_{ds}}{qN_D}}} dy \tag{29}$$

**3.2.3 Trench bottom capacitance.** In the region of  $C_{ds3}$  [Fig. 3(c)], when  $V_{ds}$  increase, at last  $y_0$  reaches almost the same depth as that of bottom of field plate.  $C_{ds2}$  decreases continuously in the model [Eqs. (25) and (29)]. Therefore, the trench bottom capacitance  $C_{ds3}$  has to be included as a component of total  $C_{oss}$ .

In the trench bottom region, the depletion layer  $W_{\text{btm}}(V_{\text{ds}}, l)$  begins to expand slightly when  $V_{\text{ds}}$  is greater than approximately 60 V.  $W_{\text{btm}}(V_{\text{ds}}, l)$  can be described similarly to Eq. (23).

$$W_{btm}(V_{ds}, l) = -\frac{\varepsilon_{Si}\cos\theta_3}{\varepsilon_{OX}\cos\theta_4} \cdot T(l) + \sqrt{\left(\frac{\varepsilon_{Si}\cos\theta_3}{\varepsilon_{OX}\cos\theta_4} \cdot T(l)\right)^2 + \frac{2\varepsilon_{Si}\varepsilon_0}{qN_D} \cdot V_{ds}}$$

(30)

Here, l is the length from the center of the trench, T(l) is the oxide thickness of the trench

bottom, and  $\theta_4$  and  $\theta_3$  are given by

$$\theta_4 = \tan^{-1}\left(\frac{l}{T_{FPOX}c}\right),\tag{31}$$

$$\theta_3 = \tan^{-1} \left( \frac{\varepsilon_{Si}}{\varepsilon_{OX}} \tan \theta_4 \right). \tag{32}$$

Thus,  $C_{ds3}$  is provided by integrating  $W_{btm}(V_{ds}, l)$  in the direction of the trench width from 0 to  $T_{FPOX b}$  and is described as

$$C_{ds3} = \frac{2 \cdot \int_0^{T_{FPOX\_b}} q N_D \frac{d}{dV} (W_{btm}(V_{ds}, l)) dl}{W_{Cell}}.$$

(33)

**3.2.4 Gate-drain capacitance.** As mentioned above, in the FP-MOSFET,  $C_{\rm gd}$  is negligible small, which is approximately two to three orders of magnitude lower than  $C_{\rm oss}$ . However, to compare it with the D-MOSFET, we carry out simplified modeling for  $C_{\rm gd}$ . As shown in Fig. 2(b), the  $C_{\rm gd}$  of the FP-MOSFET is the series connection of  $C_{\rm gox}$  and  $C_{\rm dep}$ , which is the same as in the case of the D-MOSFET. In the FP-MOSFET,  $C_{\rm gox}$  and  $C_{\rm dep}$  are expressed as

$$C_{gox} = \frac{\varepsilon_{OX}\varepsilon_0}{T_{gox}} \cdot \frac{2(D_G - X_{JB})}{W_{Cell}},\tag{34}$$

$$C_{dep} = \frac{\varepsilon_{Si}\varepsilon_0}{W_{d mos}} \cdot \frac{2(D_G - X_{JB})}{W_{Cell}}.$$

(35)

By substituting Eqs. (7), (34), and (35) into Eq. (4), the initial capacitance  $C_{\rm gd0}$  can be obtained as

$$C_{gd0} = \frac{\varepsilon_{OX}\varepsilon_{0}}{\sqrt{\frac{2V_{dS}\varepsilon_{OX}^{2}\varepsilon_{0}}{qN_{D}\varepsilon_{Si}} + T_{gox}^{2}}} \cdot \frac{2(D_{G} - X_{JB})}{W_{Cell}}.$$

(36)

Unlike the D-MOSFET, in the FP-MOSFET, the capacitance width of  $C_{\rm gd}$  is drastically reduced by the factor of  $W(V_{\rm ds},y)$ , as shown in Eq. (23). Thus, finally, the  $C_{\rm rss}$  model is described as

$$C_{rss\_FPMOS} = C_{gd0} \cdot \frac{w_{Mesa} - 2W(V_{ds}, y)}{w_{Mesa}} = \frac{\varepsilon_{OX}\varepsilon_{0}}{\sqrt{\frac{2V_{ds}\varepsilon_{OX}^{2}\varepsilon_{0}}{qN_{D}\varepsilon_{Si}} + T_{gox}^{2}}} \cdot \frac{2(D_{G} - X_{JB})}{w_{Cell}} \cdot \frac{w_{Mesa} - 2W(V_{ds}, y)}{w_{Mesa}}. (37)$$

The analytically derived  $C_{\text{oss}}$  and  $C_{\text{rss}}$  model equations for the D-MOSFET and FP-MOSFET are shown in Table IV.

## 4. Validation of proposed model

#### 4.1 Coss-Vds and Qoss-Vds curves

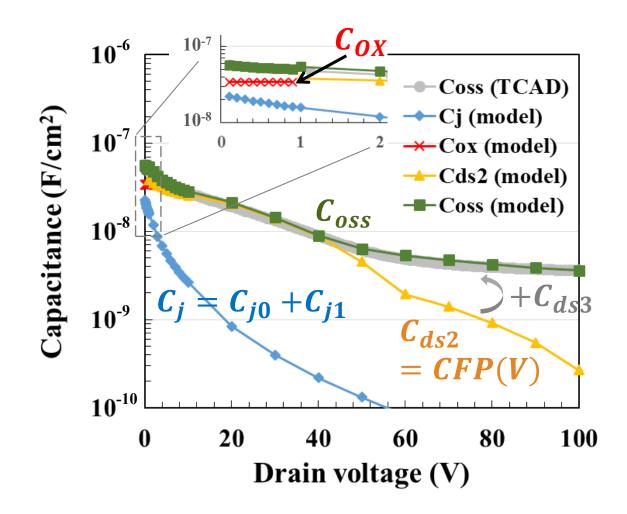

To validate the accuracy of the proposed model, firstly, we compared the calculated  $C_{\rm oss}-V_{\rm ds}$  curves of the FP-MOSFET with those of TCAD simulation. Figure 4 shows the  $V_{\rm ds}$  dependence of calculated  $C_{\rm oss}$  and each component of the FP-MOSFET;  $C_{\rm j}$  (=  $C_{\rm j0}+C_{\rm j1}$ ),  $C_{\rm ox}$ ,  $C_{\rm FP}(V)$ , and  $C_{\rm ds3}$  are drawn as the capacitances of a unit device area (cm<sup>2</sup>). In the low-voltage region of  $V_{\rm ds} < 1$  V,  $C_{\rm j}$  and  $C_{\rm ox}$  were the dominant components of total  $C_{\rm oss}$ , and the sum of  $C_{\rm j}$  and  $C_{\rm ox}$  corresponded well to TCAD results. This initial capacitance region is very important for calculating  $Q_{\rm oss}$  and  $E_{\rm oss}$ . The total  $C_{\rm oss}$  curves, which consist of all components, in the region of  $V_{\rm ds} \ge 1$  V, also showed good agreement with TCAD results.

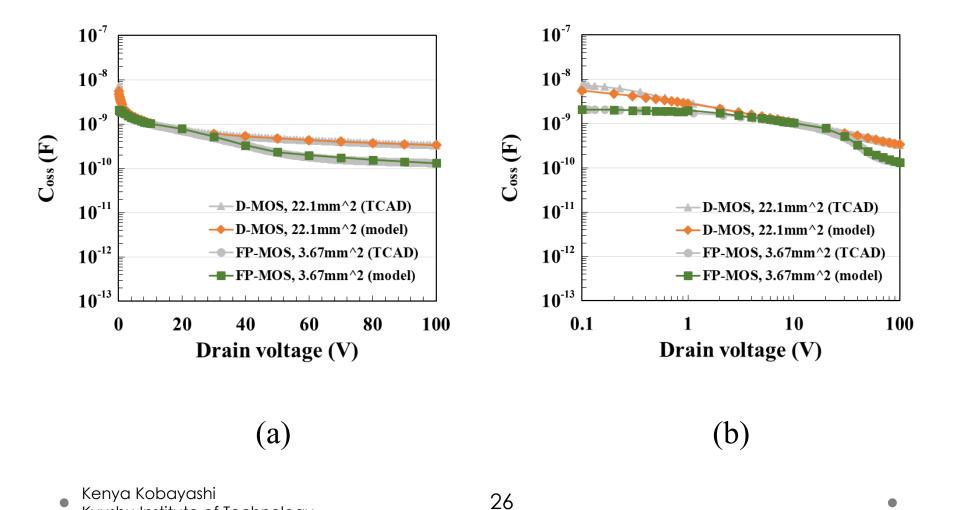

Figures 5(a) and 5(b) show the calculated  $C_{\rm oss}$  for the D-MOSFET and FP-MOSFET with TCAD simulation results, respectively. Here, each active area was designed to achieve the same  $R_{\rm ON} = 10~{\rm m}\Omega$ ; therefore, 22.1 mm² for the D-MOSFET and 3.67 mm² for the FP-MOSFET were defined. In both  $V_{\rm ds}$  linear scale [Fig. 5(a)] and  $V_{\rm ds}$  log scale [Fig. 5(b)], the  $C_{\rm oss}$  curves of both MOSFETs corresponded well qualitatively to TCAD results. In the detailed comparison for the FP-MOSFET, errors of 14 and 10% were seen at approximately  $V_{\rm ds} = 1~{\rm and}~60~{\rm V}$ , respectively, and another region showed less than 5%. These results indicate that the error occurred at the point where the  $V_{\rm ds}$  condition changed, as shown in Eqs. (11), (25), and (33). In the D-MOSFET, a maximum error of 24% was seen at  $V_{\rm ds} = 0.1~{\rm V}$ ; however, another region showed good results of less than 5%. The reason considered why the early voltage region has the error is that the spherical pn-junction of the p-base is not modeled very well.

By using the proposed model, the output charge  $Q_{oss}$  and the stored energy  $E_{oss}$  in the output capacitance are calculated as

$$Q_{oss} = \int C_{oss} dV, \tag{38}$$

$$E_{oss} = \int C_{oss} V_{ds} dV. \tag{39}$$

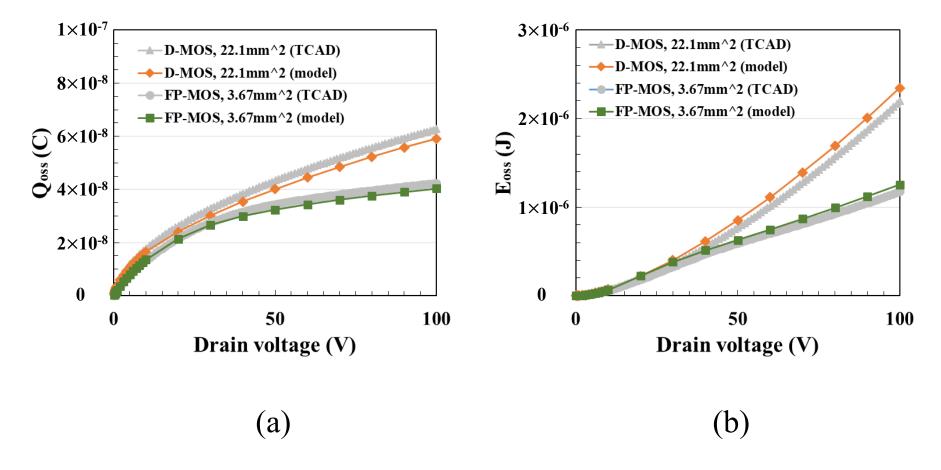

Figures 6(a) and 6(b) show the calculated  $Q_{\rm oss}$ – $V_{\rm ds}$  and  $E_{\rm oss}$ – $V_{\rm ds}$  curves compared with TCAD simulation results, for the D-MOSFET and FP-MOSFET, respectively. Each active area was designed for the same  $R_{\rm ON}$  of 10 m $\Omega$ . These modeled curves corresponded well qualitatively to TCAD curves. In an application circuit for 100-V-rating device, an input voltage ( $V_{\rm IN}$ ) of 50 V is assumed generally. In the comparison between the modeled  $Q_{\rm oss}$  and the TCAD results at  $V_{\rm ds} = 50$  V, only 6 and 7% errors were seen for the FP-MOSFET and D-MOSFET, respectively. In addition, in the case of the  $E_{\rm oss}$ , there were 5 and 10% errors for the FP-MOSFET and D-MOSFET, respectively. Therefore, it is recognized that these results are

sufficient to use for power loss analysis.

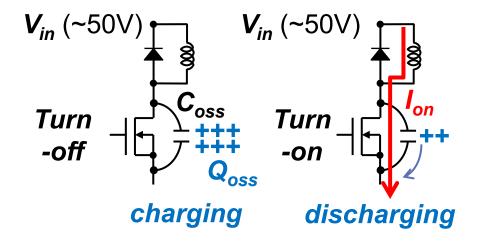

As mentioned above, this study especially focuses on the  $P_{\text{Qoss}}$  of the FP-MOSFET. Figures 7(a) and 7(b) explain the switching operation concerning  $C_{\text{oss}}$ . When the MOSFET is turned-off,  $C_{\text{oss}}$  stores charges. Then, during the turn-on sequence, the on-current  $I_{\text{ON}}$  is consumed by discharging of  $Q_{\text{oss}}$ . This becomes the energy loss  $E_{\text{oss}}$ , which is the  $Q_{\text{oss}}$  loss of one switching cycle.

#### 4.2 Crss-Vds curves and switching waveforms

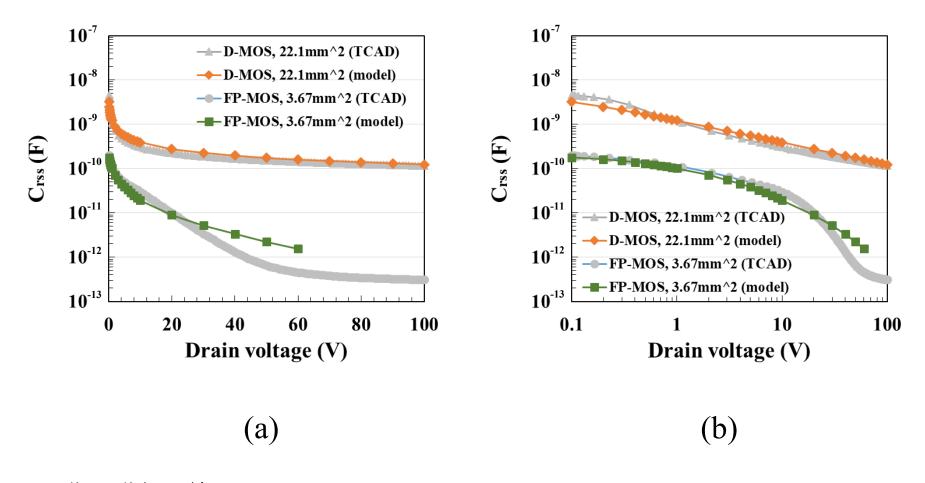

As additional validation data, we describe the calculated  $C_{rss}$ – $V_{ds}$  curves compared with TCAD simulation results for the D-MOSFET and FP-MOSFET, respectively, as shown in Figs. 8(a) and 8(b). Each active area was designed for the same  $R_{ON}$  of 10 m $\Omega$ . In both  $V_{ds}$  linear scale [Fig. 8(a)] and  $V_{ds}$  log scale [Fig. 8(b)], the  $C_{rss}$  curves of the D-MOSFET corresponded well qualitatively to TCAD results. However, there were relatively large errors with the maximum of 32% at approximately  $V_{ds} = 0.1$  and 10 V. The reason was the same as in the case of  $C_{oss}$  modeling, as mentioned in Sect. 4.1. On the other hand, in the case of the  $C_{rss}$  curves of the FP-MOSFET, errors of less than 10% were seen at  $V_{ds} \le 1$  V, and errors of less than 35% were seen at  $V_{ds} \le 1$  V. However, larger errors occurred in the high- $V_{ds}$  region because of the small value of  $C_{gd}$ , which is approximately two to three orders of magnitude lower than  $C_{oss}$ , as mentioned in Sect. 3.2.4.

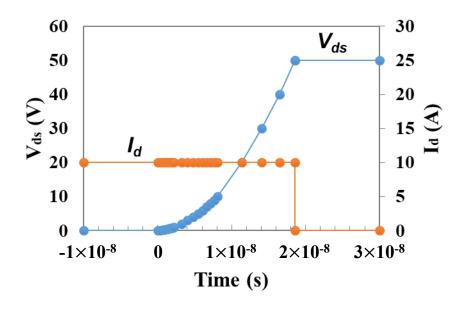

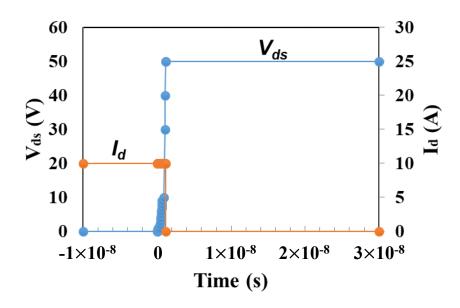

Figures 9(a) and 9(b) are the simply calculated turn-off switching waveforms using the  $C_{\rm rss}$  model for the D-MOSFET and FP-MOSFET, respectively, under the conditions of  $V_{\rm IN}$  = 50 V,  $I_{\rm ON}$  = 10 A, gate resistance  $R_{\rm g}$  = 1.5  $\Omega$ , and gate current  $I_{\rm g}$  = 0.83 A. Here, the turn-off time  $t_{\rm off}$  is given by

$$t_{off} = \int_0^{V_{IN}} \frac{c_{gd}}{I_g} dV. \tag{40}$$

As a result,  $t_{\rm off} = 18.5$  ns for the D-MOSFET and  $t_{\rm off} = 1.1$  ns for the FP-MOSFET were calculated using the proposed model. In the calculation, gate–source charge ( $Q_{\rm gs}$ ), circuit resistance ( $R_{\rm c}$ ), and stray inductance ( $L_{\rm s}$ ) are not considered.

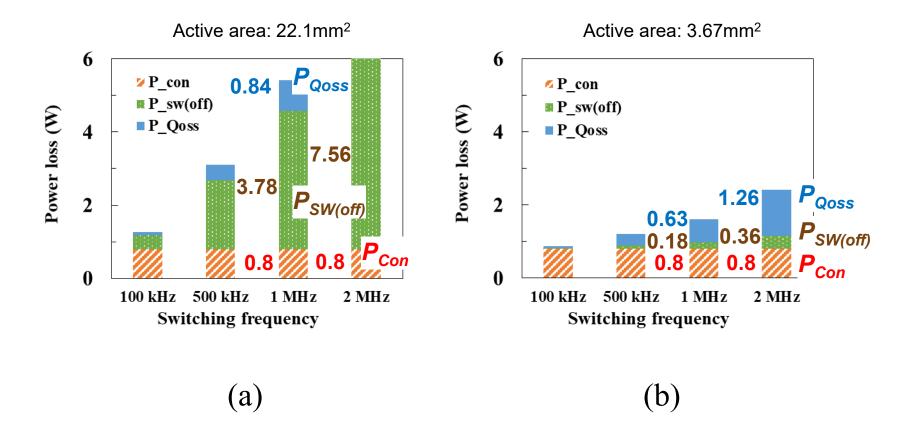

## 4.3 Power loss analysis

As a comprehensive evaluation of the proposed model, we estimated the power loss assuming a low-side MOSFET of a buck converter circuit for the D-MOSFET and FP-MOSFET. Each active area was designed for the same  $R_{\rm ON}$  of 10 m $\Omega$ . The operation conditions were  $V_{\rm IN} = 50$  V, output current  $I_{\rm O} = 10$  A, duty ratio D = 80%, and switching

frequency  $f_{SW} = 100$  kHz to 2 MHz. Here, the calculated conduction loss  $P_{CON}$ , turn-off loss  $P_{SW(off)}$ , and output charge loss  $P_{Qoss}$  are given by

$$P_{CON} = I_O^2 R_{ON} D, (41)$$

$$P_{SW(off)} = I_0 V_{IN} t_{off} f_{SW}, (42)$$

$$P_{Qoss} = E_{oss} f_{SW} = f_{SW} \int_0^{V_{IN}} C_{oss} V_{ds} dV.$$

(43)

As shown in Figs. 10(a) and 10(b), all  $P_{\text{CON}}$  values were constant at 0.8 W in both MOSFETs because of the same  $R_{\text{ON}}$ .  $P_{\text{SW(off)}}$  was greatly influenced by  $C_{\text{rss}}$ . Thus, in the D-MOSFET,  $P_{\text{SW(off)}}$  was the most dominant component and increased to 7.56 W at 2 MHz, because of the large  $R_{\text{ON}} \cdot C_{\text{rss}}$ , as shown in Table III. On the other hand, in the FP-MOSFET, the total power loss was drastically suppressed by the low  $R_{\text{ON}} \cdot C_{\text{rss}}$ , and was mainly increased by  $P_{\text{Qoss}}$ , which depended on  $f_{\text{SW}}$ . This analysis reveals that  $P_{\text{Qoss}}$  may become a significant issue in the case of high-frequency operation, in not only the latest FP-MOSFETs but also next-generation FP-MOSFETs.

### 4.4 Application to other MOSFET structures

As mentioned above, we validated the proposed model for the D-MOSFET and FP-MOSFET. In the case of the U-MOSFET structure, the modeling method is similar that for the D-MOSFET, which uses  $C_{\rm ds}$ ,  $C_{\rm gox}$ , and  $C_{\rm dep}$ . However, additional  $C_{\rm gox}$  and  $C_{\rm dep}$  components of the trench side wall have to be considered, if the trench gate penetrates the pn-junction deeply. Besides, in the case of a conventional FP-MOSFET structure, which has a nearly uniform field-plate oxide thickness, the model may be applied. In particular, the results of calculation of Eqs. (17) and (26) change depending on both  $T_{\rm FPOX\_t}$  and  $T_{\rm FPOX\_b}$ . In our future work, we would like to investigate a wider application range of the proposed model.

## 5. Conclusions

We proposed the structure-based capacitance model for the latest 100 V FP-MOSFET. The calculated  $C_{\rm oss}$ – $V_{\rm ds}$ ,  $Q_{\rm oss}$ – $V_{\rm ds}$ , and  $E_{\rm oss}$ – $V_{\rm ds}$  curves corresponded very well to TCAD results. Although errors of 10-14% were seen at any points of the  $C_{\rm oss}$  curves, other regions showed less than 5% errors. Moreover, the modeling curves of  $Q_{\rm oss}$  and  $E_{\rm oss}$  showed good accuracy, with errors of 6 and 5%, respectively. We analyzed the power loss depending on switching frequency using the model and found that the  $Q_{\rm oss}$  loss may become a significant issue, even in the latest slant FP-MOSFET. Regarding next-generation and ultimately high-efficiency FP-MOSFETs, it is expected that the proposed model is useful for the prediction of device performance.

## References

- 1) R. K. Williams, M. N. Darwish, R. A. Blanchard, R. Siemieniec, P. Rutter, and Y. Kawaguchi, IEEE Trans. Electron Devices **64**, 674 (2017).

- 2) Y. Baba, N. Matsuda, S. Yanagiya, S. Hiraki, and S. Yasuda, Proc. Int. Symp. Power Semiconductor Devices and ICs, 1992, p. 300.

- 3) B. J. Baliga, U.S. Patent 5637898 (1997).

- 4) B. J. Baliga, U.S. Patent 5998833 (1999).

- 5) G. E. J. Koops, E. A. Hijzen, R. J. E. Hueting, and M. A. A. in't Zandt, Proc. Int. Symp. Power Semiconductor Devices and ICs, 2004, p. 185.

- 6) M. Kodama, E. Hayashi, Y. Nishibe, and T. Uesugi, Proc. Int. Symp. Power Semiconductor Devices and ICs, 2004, p. 463.

- 7) M. A. Gajda, S. W. Hodgskiss, L. A. Mounfield, and N. T. Irwin, Proc. Int. Symp. Power Semiconductor Devices and ICs, 2006, p. 109.

- 8) P. Goarin, G. E. J. Koops, R. van Dalen, C. L. Cam, and J. Saby, Proc. Int. Symp. Power Semiconductor Devices and ICs, 2007, p. 61.

- 9) J. Yedinak, D. Probst, G. Dolny, A. Challa, and J. Andrews, Proc. Int. Symp. Power Semiconductor Devices and ICs, 2010, p. 333.

- 10) K. Kobayashi, T. Yamaguchi, S. Tokuda, S. Tsuboi, and H. Ninomiya, Proc. Joint Technical Meeting, IEE Japan EDD-12-068 (2012) [In Japanese].

- 11) G. Deboy, N. Marz, J. P. Stengl, H. Strack, J. Tihanyi, and H. Weber, IEDM Tech. Dig., 1998, p. 683.

- 12) H. Ninomiya, Y. Miura, and K. Kobayashi, Proc. Int. Symp. Power Semiconductor Devices and ICs, 2004, p. 177.

- 13) H. Takaya, K. Miyagi, K. Hamada, Y. Okura, N. Tokura, and A. Kuroyanagi, Proc. Int. Symp. Power Semiconductor Devices and ICs, 2005, p. 43.

- 14) P. Rutter and S. T. Peake, Proc. Int. Symp. Power Semiconductor Devices and ICs, 2010,p. 325.

- 15) Y. Kawashima, H. Inomata, K. Murakawa, and Y. Miura, Proc. Int. Symp. Power Semiconductor Devices and ICs, 2010, p. 329.

- 16) P. Rutter, S. Peake, and A. Elford, Proc. Int. Symp. Power Semiconductor Devices and ICs, 2013, p. 83.

- 17) H. Okubo, K. Kobayashi, and Y. Kawashima, Proc. Int. Symp. Power Semiconductor Devices and ICs, 2013, p. 87.

- 18) R. K. Williams, M. N. Darwish, R. A. Blanchard, R. Siemieniec, P. Rutter, and Y.

- Kawaguchi, IEEE Trans. Electron Devices 64, 692 (2017).

- 19) R. Sodhi, S. Brown Sr., and D. Kinzer, Proc. Int. Symp. Power Semiconductor Devices and ICs, 1999, p. 241.

- 20) B. Yang, J. Yuan, and Z. J. Shen, IEEE Trans. Electron Devices 58, 4004 (2011).

- 21) M. Tsukuda, I. Omura, T. Domon, W. Saito, and T. Ogura, Proc. Int. Power Electronics Conf., 2005, p. 1184.

- 22) M. Tsukuda, I. Omura, W. Saito, and T. Domon, Proc. Int. Conf. Integrated Power Electronics Systems, 2006, p. 1.

- 23) I. Omura, M. Tsukuda, W. Saito, and T. Domon, Proc. Power Conversion Conf., 2007, p. 575.

- 24) A. Schlögl, F. Hirler, J. Ropohl, U. Hiller, M. Rösch, N. Soufi-Amlashi, and R. Siemieniec, European Conf. Power Electronics and Applications, 2005, p. 1.

- 25) J. Roig, D. Lee, F. Bauwens, B. Burra, A. Rinaldi, J. McDonald, and B. Desoete, European Conf. Power Electronics and Applications, 2011, p. 1.

- 26) R. Sodhi, A. Challa, J. Gladish, S. Sapp, and C. Rexer, Proc. PCIM Europe, 2010, p. 273.

- 27) W. Choi, D. Son, and S. Young, Annual IEEE Applied Power Electronics Conf. and Exposition, 2012, p. 1676.

- 28) T. Sarkar, S. Sapp, and A. Challa, Annual IEEE Applied Power Electronics Conf. and Exposition, 2013, p. 507.

- 29) W. Saito, Proc. Int. Symp. Power Semiconductor Devices and ICs, 2013, p. 241.

- 30) T. Nishiwaki, T. Hara, K. Kaganoi, M. Yokota, Y. Hokomoto, and Y. Kawaguchi, Proc. Int. Symp. Power Semiconductor Devices and ICs, 2014, p. 382.

- 31) P. Rutter and S. T. Peake, Annual IEEE Applied Power Electronics Conf. and Exposition, 2011, p. 491.

- 32) K. Kobayashi, M. Sudo, and I. Omura, Ext. Abstr. Solid State Devices and Materials, 2017, p. 709.

- 33) Y. Chen, Y. C. Liang, and G. S. Samudra, Jpn. J. Appl. Phys. 44, 847 (2005).

- 34) Y. Chen, Y. C. Liang, and G. S. Samudra, IEEE Trans. Power Electronics **22**, 1303 (2007).

- 35) Y. Wang, H. F. Hu, W. L. Jiao, and C. Cheng, IEEE Electron Device Lett. 31, 1281 (2010).

- 36) K. Kobayashi, T. Nishiguchi, S. Katoh, T. Kawano, and Y. Kawaguchi, Proc. Int. Symp. Power Semiconductor Devices and ICs, 2015, p. 141.

- 37) Sentaurus Device User's Manual (Synopsys, Inc., 2014).

- 38) I. Budihardjo and P. O. Lauritzen, IEEE Trans. Power Electronics 10, 379 (1995).

- 39) S. Shinohara, Proc. Int. Symp. Power Semiconductor Devices and ICs, 1998, p. 347.

- 40) R. J. E. Hueting, E. A. Hijzen, A. Heringa, A. W. Ludikhuize, and M. A. A. in't Zandt, IEEE Trans. Electron Devices **51**, 1323 (2004).

- 41) O. Alatise, N. A. Parker-Allotey, M. Jennings, P. Mawby, I. Kennedy, and G. Petkos, IEEE Electron Device Lett. **32**, 1269 (2011).

- 42) M. Shintani, Y. Nakamura, M. Hiromoto, T. Hikihara, and T. Sato, Jpn. J. Appl. Phys. **56**, 04CR07 (2017).

- 43) B. J. Baliga, Fundamentals of Power Semiconductor Devices (Springer, New York, 2008).

## **Figure Captions**

- **Fig. 1.** Schematic cross sections and representative structural parameters of (a) conventional D-MOSFET and (b) slant FP-MOSFET. (c) Comprehensive structural parameters of FP-MOSFET (half-cell structure) to describe capacitance model.

- **Fig. 2.** Components of output capacitance ( $C_{oss}$ ) and reverse transfer capacitance ( $C_{rss}$ ) for D-MOSFET and FP-MOSFET.

- Fig. 3. TCAD simulated FP-MOSFET half-cell structures, which represent  $V_{ds}$  dependence of equal-potential contours. Potential contours and depletion layer boundaries are shown as black lines and white lines, respectively. Three capacitance components are shown as dominant regions; (a) main pn-junction, (b) field-plate oxide and depletion layer along trench side wall, (c) field-plate oxide and depletion layer of trench bottom.

- **Fig. 4.**  $C_{\text{oss}}$  components of FP-MOSFET calculated using proposed model compared with TCAD simulation results.

- Fig. 5.  $C_{\rm oss}$ – $V_{\rm ds}$  curves calculated using proposed model compared with TCAD results for D-MOSFET and FP-MOSFET. (a)  $V_{\rm ds}$  linear scale and (b)  $V_{\rm ds}$  log scale in X-axis. Each active area is designed for the same  $R_{\rm ON}$  of 10 mΩ.

- Fig. 6. (a)  $Q_{\text{oss}}$ – $V_{\text{ds}}$  and (b)  $E_{\text{oss}}$ – $V_{\text{ds}}$  curves calculated using proposed model compared with TCAD results for D-MOSFET and FP-MOSFET. Each active area is designed for the same  $R_{\text{ON}}$  of 10 mΩ.

- **Fig. 7.** Explanation of switching operation concerning  $C_{oss}$  and  $Q_{oss}$ .

- Fig. 8.  $C_{rss}$ – $V_{ds}$  curves calculated using proposed model compared with TCAD results for D-MOSFET and FP-MOSFET. (a)  $V_{ds}$  linear scale and (b)  $V_{ds}$  log scale in X-axis. Each active area is designed for the same  $R_{ON}$  of 10 mΩ.

**Fig. 9.** Switching waveforms calculated using proposed model for (a) D-MOSFET and (b) FP-MOSFET.

**Fig. 10.** Estimated power losses for D-MOSFET and FP-MOSFET, assuming 50 V input, 10 A output, 80% duty ratio, and 100 kHz-to-2 MHz switching operation. Each active area is designed for the same  $R_{\rm ON}$  of 10 m $\Omega$ .

Table I.

Structural parameters for 100-V-class D-MOSFET and FP-MOSFET.

| Symbol        | Parameters                     |          | D-MOSFET             | FP-MOSFET            | Unit                  |

|---------------|--------------------------------|----------|----------------------|----------------------|-----------------------|

| $N_D$         | Drift layer concentration      |          | $2.8 \times 10^{15}$ | $3.0 \times 10^{16}$ | atoms/cm <sup>3</sup> |

| $N_A$         | p-Base layer concentration     |          | $5.0\times10^{16}$   | $1.0\times10^{17}$   | atoms/cm <sup>3</sup> |

| $W_{Cell}$    | Cell width                     |          | 6.0                  | 2.6                  | μm                    |

| $W_G$         | Gate width                     |          | 3.4                  | N/A                  | μm                    |

| $W_B$         | p-Base width                   |          | 2.6                  | N/A                  | μm                    |

| $W_T$         | Trench width                   |          | N/A                  | 1.5                  | μm                    |

| $W_{Mesa}$    | Mesa width                     |          | N/A                  | 1.1                  | μm                    |

| $D_T$         | Trench depth                   |          | N/A                  | 6.0                  | μm                    |

| $D_G$         | Gate depth                     |          | N/A                  | 1.0                  | μm                    |

| $T_{GOX}$     | Gate oxide thickness           |          | 0.05                 | 0.05                 | μm                    |

| $T_{FPOX\_t}$ | Field-plate oxide thickness    | (top)    | N/A                  | 0.1                  | μm                    |

| $T_{FPOX\_b}$ |                                | (bottom) | N/A                  | 0.75                 | μm                    |

| $T_{FPOX\_c}$ |                                | (center) | N/A                  | 0.75                 | μm                    |

| $X_{JB}$      | p-Base junction depth          |          | 0.75                 | 0.9                  | μm                    |

| $X_{JB\_l}$   | p-Base junction lateral length |          | 0.60                 | N/A                  | μm                    |

Table II.

Physical constants.

| Symbol                      | Description                             | Property                | Unit                  |

|-----------------------------|-----------------------------------------|-------------------------|-----------------------|

| $\overline{q}$              | Elementary charge                       | $1.60 \times 10^{19}$   | С                     |

| k                           | Boltzmann's constant                    | $1.38 \times 10^{-23}$  | J/K                   |

| T                           | Absolute temperature                    | 300                     | K                     |

| $n_{\mathrm{i}}$            | Intrinsic carrier density               | $1.50\times10^{10}$     | atoms/cm <sup>3</sup> |

| <b>E</b> 0                  | Permittivity in vacuum                  | $8.854 \times 10^{-14}$ | F/cm                  |

| $\mathcal{E}_{\mathrm{Si}}$ | Dielectric constant of Si               | 11.7                    |                       |

| <b>€</b> OX                 | Dielectric constant of SiO <sub>2</sub> | 3.9                     |                       |

**Table III.** TCAD simulated basic characteristics for 100-V-class D-MOSFET and FP-MOSFET.

| Symbol           | Characteristics      | Condition             | D-MOSFET | FP-MOSFET | Unit                  |

|------------------|----------------------|-----------------------|----------|-----------|-----------------------|

| $V_B$            | Breakdown voltage    |                       | 111.3    | 110.1     | V                     |

| $V_{TH}$         | Threshold voltage    | $V_{ds}=10V$          | 2.09     | 2.03      | V                     |

| $R_{ON}A$        | On-resistance        | $V_{gs}=10 \text{ V}$ | 199.1    | 32.8      | $m\Omega{\cdot}mm^2$  |

| $Ron \cdot Crss$ | FOM <sup>a)</sup> _1 | $V_{ds}=50 \text{ V}$ | 1364     | 5.7       | $m\Omega\!\cdot\! pF$ |

| $Ron \cdot Coss$ | FOM_2                | $V_{ds}=50 \text{ V}$ | 4205     | 2040      | $m\Omega\!\cdot\! pF$ |

| $Ron \cdot Qoss$ | FOM_3                | $V_{ds}$ =50 V        | 390      | 309       | $m\Omega\!\cdot\! nC$ |

<sup>&</sup>lt;sup>a)</sup> FOM, figure of merit.

**Table IV.** List of  $C_{\text{oss}}$  and  $C_{\text{rss}}$  model equations for D-MOSFET and FP-MOSFET.

$$\begin{aligned} \text{D-MOSFET} & \frac{\mathcal{E}_{OX}\varepsilon_{0}}{\sqrt{\frac{2V_{dx}\varepsilon_{OX}^{2}\varepsilon_{0}}{qN_{D}\varepsilon_{Si}}} + T_{gox}^{2}} \cdot \frac{W_{G} - 2X_{JB\_l}}{W_{Cell}} \\ \hline \\ & C_{OSS\_DMOS} = \sqrt{\frac{qN_{D}\varepsilon_{Si}\varepsilon_{0}}{2\left(V_{ds} + \frac{kT}{q}\ln\frac{N_{d}N_{D}}{n_{l}^{2}}\right)} \cdot \frac{W_{B} + 2X_{JB\_l}}{W_{Cell}} + C_{rSS\_DMOS}} \\ \hline \\ & C_{TSS\_FPMOS} = \sqrt{\frac{qN_{D}\varepsilon_{Si}\varepsilon_{0}}{\sqrt{\frac{2V_{ds}\varepsilon_{OX}^{2}\varepsilon_{0}}{qN_{D}\varepsilon_{Si}}} + T_{gox}^{2}} \cdot \frac{2\left(D_{G} - X_{JB}\right)}{W_{Cell}} \cdot \frac{W_{Mesa} - 2W\left(V_{ds}, y\right)}{W_{Mesa}} \\ \hline \\ & W\left(V_{ds}, y\right) = -\frac{\varepsilon_{Si}\cos\theta_{3}}{\varepsilon_{OX}\cos\theta_{2}} \cdot T\left(y\right) + \sqrt{\left(\frac{\varepsilon_{Si}\cos\theta_{4}}{\varepsilon_{OX}\cos\theta_{2}} \cdot T\left(y\right)\right)^{2} + \frac{2\varepsilon_{Si}\varepsilon_{0}}{qN_{D}}} \cdot V_{ds}} \\ \hline \\ & C_{ds1} = \begin{cases} C_{j0} = \frac{qN_{D}\varepsilon_{Si}\varepsilon_{0}}{\sqrt{2\left(V_{ds} + V_{Di}\right)}} \cdot \frac{W_{Mesa}}{W_{Cell}} & , \quad V_{ds} < 1(V) \\ C_{j1} = \frac{\varepsilon_{Si}\varepsilon_{0}}{y_{0} + X} \cdot \frac{W_{Mesa} - 2W\left(V_{ds}, y\right)}{W_{Cell}} & , \quad V_{ds} \geq 1(V) \\ C_{ds2} = \begin{cases} C_{OX} = \frac{2\left(D_{T} - X_{JB} - X - T_{FPOX\_c}\right)\varepsilon_{OX}\varepsilon_{0}}{W_{Cell}} & , \quad V_{ds} < 1(V) \\ C_{FP}\left(V_{ds}\right) = \frac{2 \cdot \int_{y_{0}}^{y_{0}} qN_{D}\frac{d}{dV}\left(W\left(V_{ds}, y\right)\right)dy}{W_{Cell}} & , \quad V_{ds} \geq 1(V) \\ W\left(V_{ds}, y\right) = -\frac{\varepsilon_{Si}\cos\theta_{4}}{\varepsilon_{OX}\cos\theta_{2}} \cdot T\left(y\right) + \sqrt{\left(\frac{\varepsilon_{Si}\cos\theta_{4}}{\varepsilon_{OX}\cos\theta_{2}} \cdot T\left(y\right)\right)^{2} + \frac{2\varepsilon_{Si}\varepsilon_{0}}{qN_{D}}} \cdot V_{ds}} \\ C_{ds3} = \frac{2 \cdot \int_{0}^{T_{FPOX\_b}} qN_{D}\frac{d}{dV}\left(W_{btm}\left(V_{ds}, l\right)\right)dl}{W_{Cell}} \\ W_{btm}\left(V_{ds}, l\right) = -\frac{\varepsilon_{Si}\cos\theta_{4}}{\varepsilon_{OX}\cos\theta_{4}} \cdot T\left(l\right) + \sqrt{\left(\frac{\varepsilon_{Si}\cos\theta_{4}}{\varepsilon_{OX}\cos\theta_{4}} \cdot T\left(l\right)\right)^{2} + \frac{2\varepsilon_{Si}\varepsilon_{0}}}{qN_{D}}} \cdot V_{ds}} \\ C_{aa} \sim 0 \end{cases} \end{aligned}$$

Fig. 1. (Color online)

Kenya KobayashiKyushu Institute of Technology

(a)

(b)

Kyushu Institute of Technology

Fig. 5. (Color online)

Kenya KobayashiKyushu Institute of Technology

Fig. 8. (Color online)

Kenya KobayashiKyushu Institute of Technology

(a)

(b)