## Paper

# Impact of the passive component structure for high efficiency and fast response POL using Power Supply on Chip

KENJI KAJIHARA $^{*\dagger}$  Non-member, SEIYA  $ABE^{\dagger}$  Member SATOSHI MATSUMOTO $^{\dagger}$  Non-member

(Received September 25, 2019, revised December 18, 2019)

**Abstract:** Power-SoC, which integrates MCU, power device, control circuits and passive devices on the same chip has been attracted attention. In this paper, we discuss the impact of passive component structure for high efficiency and fast response POL using 3D Power-SoC (Supply on Chip). We propose the optimal structure according to the switching frequency based on simulations.

Keywords: high efficiency, fast response, DC-DC converter, Power supply on chip, Point of load, high frequency,

#### 1. Introduction

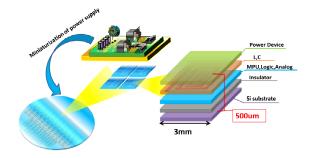

In recent years, LSIs like MCU (Micro Controller Unit) face the problems such as voltage drop, voltage fluctuation and loss cause by line impedance at lower voltage and high current operations. Therefore, a POL (Point of Load) plays an important role in LSIs and it becomes main stream to implement the POL near the load (LSIs)[1]. Power supply on chip (Power-SoC), which integrates MCU, power device, control circuits and passive devices on the same chip is shown in Fig. 1, has been attracted attentions [2]~[4] because it can realize ultimate miniaturization of the POL.

The passive components such as inductors and capacitors occupy large part of power supplies. Increase the switching frequency is one of the most effective ways to miniaturize the passive components. Thus, the switching frequency of more than multi tens MHz is required for Power-SoC and the traditional PWM control faces the problem that cannot follow feedback control.

In addition, Power-SoC can miniaturize the POLs, however it cannot handle larger power.

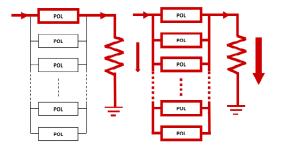

In such a scheme, we previously proposed a control technique suitable for Power-SoC[5]~[7], which is based on parallel connected POLs. The proposed control technique changes the number of working POLs (Fig. 2).

The key applications of Power-SoC are DVFS (Dynamic Voltage and Frequency Scaling) and envelope tracking. These applications are required high efficiency and fast response. We previously reported design guideline for high efficiency Power-SoC based on 3D Power-SoC [8]. However, it has not been considered design guideline for fast response.

In this paper, we report design consideration of high efficiency and fast response POL using 3D Power-SoC.

Figure 1: Power-SoC.

Figure 2: Parallel connected POL system.

#### 2. Experimental set up

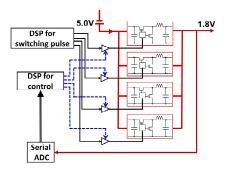

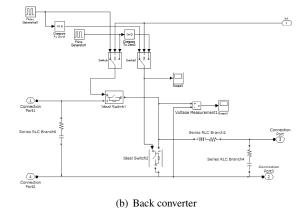

Figure 3 illustrates the block diagram of experimental system for evaluations. We use buck converters. Fig. 4 shows the picture of experimental circuits. Table 1(a) and Table 1(b) show the circuit parameters and system specifications for evaluations respectively.

#### 3. Simulations

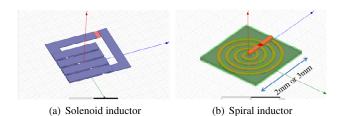

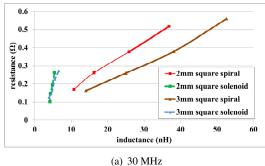

**3.1 Inductor** We simulated the performance of spiral and solenoid inductors using HFSS (High Frequency Structure Simulator) [9]. Chip size is  $2 \sim 3 \text{ mm} \times 2 \sim 3 \text{ mm}$  and number of turns are from 3 to 6 (Fig. 5).

<sup>\*</sup> Corresponding: kajihara.kenji653@mail.kyutech.jp

<sup>†</sup> Kyushu Institute of Technology

<sup>1-1</sup> Sensui-cho, Tobata-ku, Kitakyushu-shi, Fukuoka, Japan

Figure 3: The block diagram of experimental system.

Figure 4: The picture of experimental circuits.

Table 1: Circuit parameters and system specifications.

| (a) Circuit parameters |                           |               |  |

|------------------------|---------------------------|---------------|--|

| Symbol                 | Description               | Value         |  |

| L                      | Smoothing Inductor        | 4.7 μH        |  |

| C                      | Input / Output Capacitor  | $4.7 \mu H$   |  |

| R                      | Direct Current Resistance | $0.24~\Omega$ |  |

|        | (b) System specifications |       |

|--------|---------------------------|-------|

| Symbol | Description               | Value |

| Vim    | Input Voltage             | 5 V   |

| Vset   | Target Voltage            | 1.8 V |

| Fs     | Switching Frequency       | 1 MHz |

Figure 5: The model of inductors.

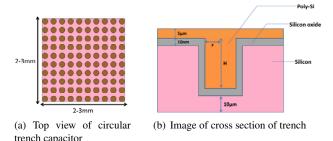

- **3.2 Capacitor** We calculated the capacitance and equivalent resistance (ESR) of trench capacitor using analytical model[10]. Trench capacitor is shown in Fig. 6. We decide to trench depth (H) is  $20 \, \mu \text{m}$ , thickness of silicon oxide layer is 10 nm, and space between trenches is  $0.5 \, \mu \text{m}$ . We changes radius of trench capacitor.

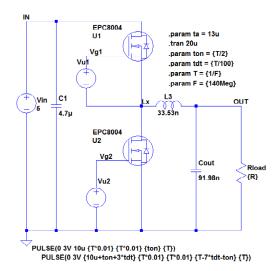

- **3.3 Buck converter** We use LT-spice [11] for circuit simulations and calculated efficiency and output power of

Figure 6: The schematics of trench capacitor.

Figure 7: Circuit diagram of buck converter on LTspice.

buck converter which use inductor simulated in "A" and capacitor calculated in "B". Circuit diagram is shown in Fig. 7. Switching device is GaN power device (EPC8004). The input voltage is 5 V and the duty ratio is 50% (output voltage: 2.5 V). The switching frequency are 30 MHz, 100 MHz and 140 MHz, respectively. 30 MHz is the lowest frequency which can use air core spiral inductor at high efficiency. In addition, we have already developed 30 MHz gate driver IC for GaN power devices [12]. 100 MHz is a frequency where solenoid inductors are more efficient than spiral inductors. 140 MHz is a previously reported silicon based converter [13].

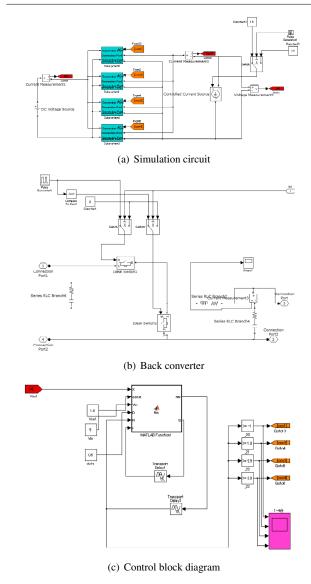

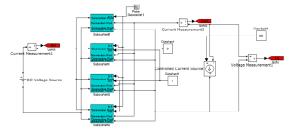

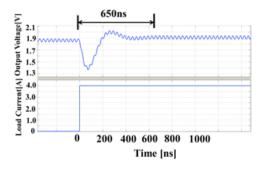

**3.4** Transient response We use MATLAB/Simulink [14] to calculate transient response using the inductor simulated in "A" and the capacitor calculated in "B". The calculated transient response is sudden load change and sudden duty change. Fig. 8 and Fig. 9 show the circuit diagram of sudden load change and that sudden duty change, respectively.

#### 4. Result and discussion

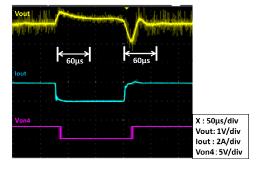

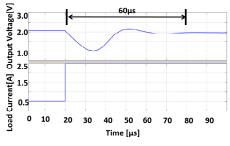

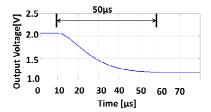

**4.1 Experimental results** Figure 10 shows the transient response of output voltage at sudden load change. The output voltage stabilized in 60  $\mu$ s at both increase and decrease output current. We changed it from 0.5 A to 2.5 A, and from 2.5 A to 0.5 A at the same time.

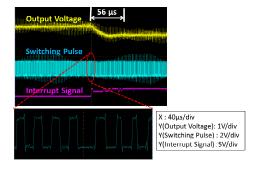

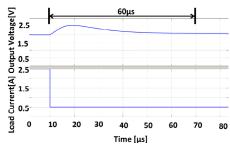

Figure 11 shows the transient response of output voltage

Figure 8: Circuit diagram of load sudden change.

at sudden duty change. The number of working POL is 1 and duty ratio changes from 50% to 33%. The output voltage stabilized in  $56~\mu s$ .

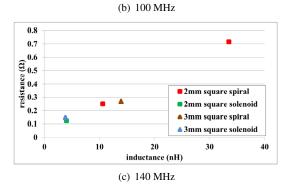

**4.2 Passive components** The performance of spiral and solenoid inductors at 30 MHz, 100 MHz and 140 MHz is shown in Fig. 12 [8]. The resistance and inductance increases as the number of turns increases.

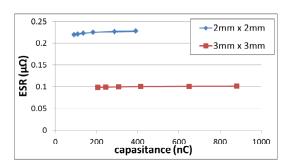

Figure. 13 shows the performance of trench capacitor whose trench radius is changed to  $0.5{\sim}5~\mu m[8]$ . We choose capacitance and ESR is 91.98 nF, 0.220  $\mu\Omega$ , (chip size: 2 mm sq.), and 207 nF and 0.099  $\mu\Omega$  (chip size: 3 mm sq.) when the trench depth is  $20~\mu m$ .

**4.3 Simulated transient response** Simulated transient response of sudden load changes of buck converter at 1 MHz is shown in Fig. 14. Simulated transient response of sudden duty change of buck converter at 1 MHz is also shown in Fig. 15. The circuit parameters and specifications used in the simulations are listed in Table 1(a) and Table 1(b). The simulation results are good agreement with ex-

(a) Simulation circuit

Figure 9: Circuit diagram of DVS.

Figure 10: Output voltage waveform at load sudden change.

Figure 11: Output voltage waveform at duty sudden change.

perimental results.

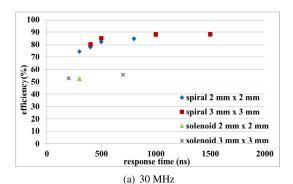

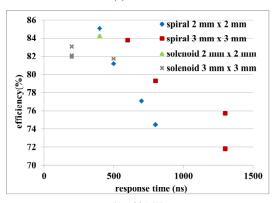

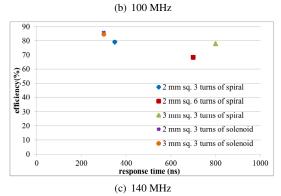

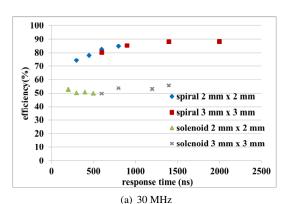

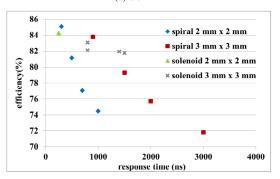

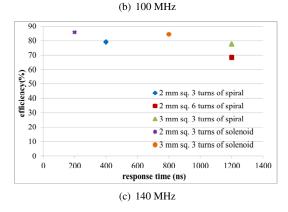

Relationship between efficiency and response time of sudden load changes is shown in Fig. 16. Relationship between efficiency and response time of sudden duty changes is shown in Fig. 17.

At switching frequency of 30 MHz, fast response time and high efficiency are obtained at chip size of 2 mm sq.

0.9

0.8

0.7

© 0.6

2 0.5

2 0.1

0 0 10 20 30 40 50 60 inductance (nH)

Figure 12: Performance of spiral and solenoid inductors.

Figure 13: The performance of trench capacitor.

and 5 turns of spiral inductor and chip size of 3 mm sq. and 3 turns of spiral inductor. Also, the response time is faster when the chip size is 2 mm, and spiral inductor is more efficient. For the same size, the efficiency increases as the number of turns increases, but the response time decreases. At 100 MHz, fast response time and high efficiency are obtained at chip size of 2 mm sq. and 3 turns of spiral and solenoid inductor. The response time is faster when the chip size is 2 mm sq., and there is no difference between spiral inductor and solenoid inductor. At 140 MHz, fast response time and high efficiency are obtained at chip size of

(a) Increase output current

(b) Decrease output current

Figure 14: Simulated transient response of load sudden changes.

Figure 15: Simulated transient response of duty sudden changes.

2mm sq. and 3 turns of solenoid inductor. The effect of the chip size is small, and there is no difference between spiral inductor and solenoid inductor. At over 100 MHz, for the same size, the efficiency and the response time decreases as the number of turns increases.

Also, this Eq. 1 and Eq. 2 are transfer function of sudden load change and sudden duty change.

The Eq. 3 is the transient response of sudden load change using the Eq. 1. The Eq. 4 is that response of sudden duty change using the Eq. 2.

$$\begin{split} \frac{\Delta v_0(t)}{\Delta i_0(t)} & \Delta V_i = 0\\ \Delta D = 0 \end{split}$$

$$= r_L - \sqrt{(r_L - r_C)^2 + \left(\frac{C(r_L^2 + r_C^2) - 2L}{\sqrt{4LC - C^2(r_L + r_C)^2}}\right)^2} e^{-\frac{r_L + r_C}{2L}t}$$

$$\times \sin\left(\frac{\sqrt{4LC - C^2(r_L + r_C)^2}}{2LC}t + \tan^{-1}\frac{\sqrt{4LC - C^2(r_L + r_C)^2}(r_L - r_C)}{C(r_L^2 + r_C^2) - 2L}\right) \tag{1}$$

$$\frac{\Delta v_0(t)}{\Delta D(t)} \begin{vmatrix} \Delta V_i = 0 \\ \Delta i_0 = 0 \end{vmatrix}$$

$$= V_i - V_i \sqrt{1 + \frac{C^2(r_L - r_C)^2}{4LC - C^2(r_L + r_C)^2}} e^{-\frac{r_L + r_C}{2L}t}$$

$$\times \sin\left(\frac{\sqrt{4LC - C^2(r_L + r_C)^2}}{2LC}t + \tan^{-1}\frac{\sqrt{4LC - C^2(r_L + r_C)^2}}{C(r_L - r_C)}\right)$$

(2)

$$T_{s} = -\frac{2L}{r_{L} + r_{C}} \ln \left( \frac{0.01 r_{L}}{(r_{L} - r_{C})^{2} + \left\{ \frac{C(r_{L}^{2} + r_{C}^{2}) - 2L}{\sqrt{4LC - C^{2}(r_{L} + r_{C})^{2}}} \right\}^{2}} \right)$$

(3)

Figure 16: Efficiency vs. response time of load sudden changes.

$$T_s = -\frac{2L}{r_L + r_C} \ln \left( \frac{0.01}{\sqrt{1 + \frac{C^2(r_L - r_C)^2}{4LC - C^2(r_L + r_C)^2}}} \right)$$

(4)

From the results of 30 MHz, 100 MHz, and 140 MHz

Figure 17: Efficiency vs. response time of duty sudden changes.

Figure 18: Simulated sudden load changes and sudden duty change at the same time.

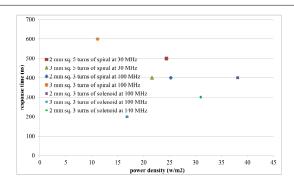

Figure 19: Response time vs. power density.

and Eq. 3 and Eq. 4, the response time is almost the same when the same inductance. The solenoid inductor can be use over 100 MHz because smaller inductance can be used as the frequency increases.

Figure 18 shows the result of simulating when 30 MHz, chip size of 2 mm sq. and 6 turns of spiral inductor sudden load changes and sudden duty change at the same time. Form the result of Fig. 18, confirmed that sudden load changes and sudden duty change can be performed simultaneously.

Figure 19 shows the relationship between response time of sudden load changes and power density at fast response time and high efficiency (>80%). From the results of Fig. 19, inductors which are suitable for fast response, high efficiency, and power density are chip size of 2 mm sq. and 5 turns of spiral inductor and chip size of 3 mm sq. and 5 turns of spiral inductor at 30 MHz. At 100 MHz, chip size of 2 mm sq. and 3 turns of solenoid inductor are suitable for fast response time, high efficiency, and power density. At 140 MHz, chip size of 2 mm sq. and 3 turns of solenoid inductor are suitable for fast response time, high efficiency, and power density.

#### 5. Conclusions

We clarify design guideline for high efficiency and first response POL. At 30 MHz, spiral inductor meets fast response time, high efficiency, and high power density. At 100 MHz, solenoid inductor is better than spiral inductor because power density of solenoid inductor is higher than spiral inductor. At 140 MHz, the solenoid inductor can realize fast response time, high efficiency, and high power density. Therefore, when switching frequency is 30 MHz, the spiral inductor is suitable. The solenoid inductor is suitable over 100 MHz.

### References

- [1] TIDesigns, TEXAS INSTRUMENTS, http://www.tij.co.jp/analog/jp/docs/analogsplash.tsp?contentId=46073, access date: 2018.7.23

- [2] S. Matsumoto, "Future Power Electronics for Realizing Sustaining Society", *International Workshop on Power Supply On Chip 2010 (PwrSoc'10)*, Session 6.6, 2010.

- [3] K. Bharath and S. Venkataraman, "Power Delivery Design and Analysis of 14 nm Multicore Server CPUs with Integrated Voltage Regulators", 2016 IEEE 66th Electronic Components and Technology Conference(ECTC 2016), pp.368-373, 2016. DOI: 10.1109/ECTC.2016.322

- [4] T. Phillips, "Delivering the Inner Power of SoCs: The Value of Fully Integrated Voltage Regulator", *International Workshop on Power Supply On Chip 2018(PwrSoc'18)*, session 6-2, 2018.

- [5] T. Yamamoto, J. Rikitake, S. Matsumoto, T. Ninomiya and S. Abe, "A new control strategy for power supply on chip using parallel connected DC-DC converter", 2013 IEEE 10th International Conference on Power Electronics and Drive Systems (PEDS 2013), pp.109-112, 2013. DOI: 10.1109/PEDS.2013.6526998

- [6] M Higashida, T Yamamoto, S Abe and S Matsumoto, "A Concept of field programmable power supply array utilizing power supply on chip—fully digital controlled multiple input and output voltages POL", 2015 17th European Conference on Power Electronics and Applications (EPE'15 ECCE-Europe), LS1e4, 2015. DOI: 10.1109/EPE.2015.7309289

- [7] S. Abe, S. Matsumoto and T. Ninomiya, "A Novel Load Regulation Technique for Power-SoC with Parallel Connected POLs", *IEEJ Journal of Industry Application*, Vol.4 No.6, pp.732-737, 2015. DOI: 10.1541/ieejjia.4.732

- [8] K. Ono, K. Hiura and S. Matsumoto, "Design Consideration of a 3D Stacked Power Supply on Chip", 2018 IEEE 68th Electronic Components and Technology Conference(ECTC 2018), Session 27.7, 2018. DOI: 10.1109/ECTC.2018.00196

- [9] ANSYS HFSS, ANSYS, http://www.ansys.com/ja-jp/ products/electronics/ansys-hfss, access date: 2019.4.23

- [10] K. Hiura, Y. Ikeda, Y. Hino and S. Matsumoto, "Impact of three-dimensional stacked power supply on chip for high-frequency DC-DC converter", *Japanese Journal of Applied Physics*, Vol.56, PP.04CR13, 2017. DOI: 10.7567/JJAP.56.04CR13

- [11] MYANALOG, ANALOG DEVICES, https:

//www.analog.com/jp/design-center/

design-tools-and-calculators/

ltspice-simulator.html/LTspice, access date:

2019.2.12

- [12] T. Akagi, S. Miyano, S. Abe and S. Matsumoto, "A silicon based multi-tens MHz gate driver IC for GaN power device", 2017 IEEE Applied Power Electronics Conference and Exposition, (APEC 2017), pp.1978-1982, 2017. DOI: 10.1109/APEC.2017.7930969

- [13] E. A. Burton, G. Schrom, F. Paillet, J. Douglas, W. J. Lambert, K. Radhakrishnan and M. J. Hill, "FIVR-Fully integrated voltage regulators on 4th generation Intel Core<sup>TM</sup> SoCs", 2014 IEEE Applied Power Electronics Conference and Exposition(APEC 2014), pp.432-439, 2014. DOI: 10.1109/APEC.2014.6803344

- [14] Simulink, *MathWorks*, https://jp.mathworks.com/products/simulink.html/MATLAB/Simulink, access date: 2018.9.12

Kenji Kajihara (Non-member) had been a bachelor course student in Department of Electrical and Electronic Engineering, Kyushu Institute of Technology, Fukuoka, Japan, since 2015 and he was received the B. E degrees in Electrical and Electronic Engineering from Kyushu Institute of Technology in 2019. He has been a master course student of Kyushu Institute of Technology in 2019.

nology since 2019. He has been studying about miniaturization of switching power supply, Power-SoC which implements power semiconductor devices, passive components, and control circuits on silicon wafers, control technology of high frequency switching power supply other than PWM control, and transient response of switching power supply since 2018.

Seiya Abe (Member) received the M. E. and Dr. Eng. Degree in Electronics from Kyushu University, Japan in 2002 and 2005, respectively. Since 2005 he had been Research Assistant in the Department of Electrical and Electronic Systems Engineering of the Graduate School of Information Science and Electrical Engineering, Kyushu University, and since 2006 he had been Research

Associate, and since 2006 he had been Assistant Professor. Since 2010 he had been Research Assistant Prof. in The International Centre for the Study of East Asian Development (ICSEAD). Currently, he is Associate Professor in Kyushu Institute of Technology. His research interests are Switch-Mode Power Supplies.

Satoshi Matsumoto (Non-member) received B.E., M.E., and Dr.Eng. degrees in applied chemistry from Waseda University, Tokyo, Japan, in 1982, 1984, and 1996, respectively. In 1984, he joined NTT LSI Laboratories, Kanagawa, Japan, where he worked on research and development of power ICs, analog high frequency devices and circuits, and energy harvest-

ing systems. In 2010, he moved to Kyushu Institute of Technology, Fukuoka, Japan, where he has been engaged in research and development of 3D integrated electronics system based on power supply on chip. Dr. Matsumoto is a member of the institute of Electronics, Information, and Communication Engineer and a senior member of IEEE.