# An Investigation on FPGA Implementation of Model Predictive Control for Three-Phase Voltage Source Inverters: Model-Based Design (MBD)

Approach, Hardware-in-the-Loop (HIL) Simulation and FPGA Resource Optimization

By

#### SINGH VIJAY KUMAR

Supervisor

Prof. Tsuyoshi Hanamoto

A dissertation submitted in the partial fulfilment for the degree of 'Doctor of Philosophy' in Engineering

to

Department of Life Science and Systems Engineering

Kyushu Institute of Technology

Wakamatsu-ku, Kitakyushu-shi, Fukuoka, Japan

February 2019

#### **ACKNOWLEDGEMENTS**

Completing this doctoral dissertation could not be possible without the help and support of many people to whom I would like to express my deepest gratitude.

First and foremost, I would like to express my deepest gratitude to my supervisor Prof. Tsuyoshi Hanamoto for granting such a wonderful atmosphere in the laboratory where every student can do his/her research with the full freedom of thoughts and with own working style. He has been always supportive of each and every moment whenever I need any support or suggestion. I feel fortunate that I had a chance to work under his supervision.

I would like to give sincere thanks to my dissertation committee members, Prof. Ichiro Omura, Prof. Shyam S. Pandey and Prof. Satoshi Matsumoto for their patiently reading my dissertation and giving me valuable suggestions and comments towards the improvement of my dissertation.

I would take this opportunity to thank Prof. Shyam S. Pandey who guided me to do my research in Hanamoto Laboratory and provided support like a guardian/mentor during my study in Japan.

I am also very thankful to all my laboratory members for helping and supporting me during my period of doctoral study especially, Ravi Kant, Maehata, Akabae, Ono, Hashimoto, Ipsita, Ikeura, Ishibashi, Tatsuki, Rajesh. These guys made the environment of the laboratory like a family where we enjoyed a lot by doing parties, trips, and games.

I wish to give my special thanks to Gaurav Kapil, Mallikarjun Yelameli, Ravi Nath Tripathi, Atul and Ankur for their enjoyable company in Kitakyushu. Also, being graduated from the same laboratory, a lot of fruitful research discussions with Ravi Nath Tripathi helped me to widen my research area and knowledge.

I would like to express my gratitude to Kyutech teaching and non-teaching staff, JASSO, Kyutech foundation, ASSURAN international scholarship foundation, FAIS for supporting my study and stay in Japan. I wish to thank Japanese language teachers for their experienced teaching and effort to teach the Japanese language.

I would like to thank my Master's supervisor Prof. Rajesh Gupta in India, who had provided a nice research background, motivated me for higher studies during my master's study and developed an interest in the learning process.

Last, but by no means least, I would like to express my sense of gratitude to my parents, my wife and my sons for supporting me throughout my academic career and life. Without their support, it has not been possible for me to study in Japan.

#### **ABSTRACT**

Model predictive control (MPC), a modern switching control method, has gained considerable interest in performing control objectives of power converters. One of the categories in a wide family of MPC is finite control set-MPC (FCS-MPC) that utilizes the discrete-time model of a power converter having a limited number of switching states for solving the optimization problem online. In FCS-MPC, a discrete-time model of the power converter is used to predict future values of control parameters and an optimization function (cost function) is used to select the optimized switching state of the converter. High computational requirements of the FCS-MPC is a concern for the system implementation. Field-programmable gate array (FPGA) is an effective alternative to handle the computational burden of the control algorithm because of its parallel processing nature.

In general, the MPC algorithm is performed through a programming approach either for DSP or FPGA. However, digital resource utilization is another concern for the development and real-time system implementation. Digital resource optimization requires a high value of in-depth knowledge to write the hardware descriptive code. Moreover, debugging is also a tedious and time-consuming task that is not appropriate for the development and analysis of the controller as well as prototyping. In this work, the implementation of FCS-MPC is performed by adopting the modelling approach in a digital simulator that provides a virtual FPGA environment for system development. In addition, hardware-in-the-loop (HIL) technique is used for testing of controller performance before experimental validation.

The current prediction is a core part of the FCS-MPC and a coefficient used for the current prediction that is computed using the system parameters affects the controller performance. In this work, a novel approach is presented to update the predictive model, called an adaptive predictive model, corresponding to a change in the load resistance while keeping a fixed value of load inductance. The fixed, approximated and adaptive values of a coefficient are adopted for current prediction to investigate the behaviour of the controller.

The performance of the FCS-MPC depends on the sampling frequency used for the discretization of the converter model that governs the switching frequency of the

converter. The performance can be improved with higher sampling frequency, however, resulting in higher switching frequency that ultimately increases the switching losses in the power devices. Apart from that, a non-zero steady-state error is one of the concerns of the FCS-MPC implementation.

In general, dedicated constraints for the reduction in average switching frequency and SSE are incorporated inside a cost function in conventional FCS-MPC. Nevertheless, that ultimately increases the computational burden. A modified cost function based on a novel constraint is proposed for the improvement in SSE as well as a reduction in the switching frequency using the modified FCS-MPC approach. To validate the performance of the proposed constraint, a comparative analysis is presented with the constraint of a change in switching state considering indices SSE as well as average switching frequency. Moreover, the different load currents and sampling time are considered to evaluate SSE considering similar load current ripples. To evaluate the robustness of the FCS-MPC algorithms, a step-change in reference current is considered for the demonstration of dynamic performance.

Moreover, an analytical approach based implementation strategies is proposed for FPGA resource optimization of the FCS-MPC development in a digital simulator for the FPGA-based system implementation. The implementation of FCS-MPC in stationary  $\alpha\beta$  and rotating dq frames is adopted for in-depth system analysis. The implementation strategies are compared based on FPGA resource requirements for the FCS-MPC in both frames corresponding to the fixed, approximated and adaptive coefficient values of the predictive model.

The optimum design based controller model is used for the FPGA-based experimental system implementation. Xilinx system generator (XSG) as a digital simulator that is an integrated platform with MATLAB/Simulink is used for the development of the controller. The FCS-MPC is implemented for the load-side current control of a three-phase voltage source inverter (VSI) system. A Xilinx FPGA board (Zedboard Zynq Evaluation and Development Kit) is used for the HIL simulation as well as the real-time system implementation.

### TABLE OF CONTENTS

| ACKNOWLEDGEMENTS                                                | i   |

|-----------------------------------------------------------------|-----|

| ABSTRACT                                                        | iii |

| TABLE OF CONTENTS                                               | v   |

| LIST OF FIGURES                                                 | vii |

| LIST OF TABLES                                                  | xi  |

| PUBLICATIONS                                                    | xii |

| Chapter 1: INTRODUCTION                                         | 1   |

| 1.1 Energy Demand and Challenges                                | 1   |

| 1.2 Role of Power Electronics                                   | 2   |

| 1.3 Power Converter Control                                     | 4   |

| 1.4 Literature Background                                       | 7   |

| 1.5 Objectives                                                  | 12  |

| 1.6 Organization and Overview                                   | 14  |

| <b>Chapter 2:</b> FINITE CONTROL SET – MODEL PREDICTIVE CONTROL | 17  |

| 2.1 Fundamental Principle                                       | 17  |

| 2.1.1 System model                                              | 18  |

| 2.1.2 Cost function design                                      | 20  |

| 2.2 Current Control of Three-Phase VSI                          | 21  |

| 2.2.1 Three-phase VSI system model                              | 22  |

| 2.2.2 Cost function                                             | 26  |

| 2.3 Summary                                                     | 28  |

| <b>Chapter 3:</b> MODEL-BASED DESIGN AND HIL SIMULATION         | 29  |

| 3.1 Introduction                                                | 29  |

| 3.1.1 MBD approach                                              | 30  |

| 3.1.2 HIL Overview                                              | 31  |

| 3.2 Modelling of FCS-MPC Algorithm                              | 32  |

| 3.2.1 Computation of cost function                              | 32  |

| 3.2.2 Selection of optimum switching state                      | 34  |

| 3.2.3 Generation of switching signal and index number           | 35  |

| 3.3 HIL Co-simulation Methodology                               | 36  |

| 3.4 Simulation Results                                          | 39  |

| 3.4.1 Intermediate response                                     | 41  |

| 3.4.2 Effect of sampling time                                                   | 42    |

|---------------------------------------------------------------------------------|-------|

| 3.4.3 Tracking performance                                                      | 44    |

| 3.5 Experimental Results                                                        | 45    |

| 3.5.1 Experimental setup                                                        | 45    |

| 3.5.2 System performance                                                        | 48    |

| 3.6 Summary                                                                     | 56    |

| Chapter 4: ADVANCED FCS-MPC: ADAPTIVE PREDICTIVE MODE                           | L AND |

| MODIFIED COST FUNCTION                                                          | 58    |

| 4.1 Introduction                                                                | 58    |

| 4.2 Adaptive Predictive Model                                                   | 60    |

| 4.2.1 Performance with adaptive predictive model                                | 62    |

| 4.3 Modified Cost Function                                                      | 70    |

| 4.3.1 Cost function with the constraint of change in switching state            | 71    |

| 4.3.2 Modified cost function with proposed constraint                           | 72    |

| 4.3.3 System performance                                                        | 73    |

| 4.4 Summary                                                                     | 81    |

| Chapter 5: FPGA RESOURCE OPTIMIZATION                                           | 83    |

| 5.1 Introduction                                                                | 83    |

| 5.2 Implementation Strategy                                                     | 84    |

| 5.2.1 Fundamental mathematical blocks                                           | 84    |

| 5.2.2 MCode blocks                                                              | 85    |

| 5.3 Resource Utilization                                                        | 87    |

| 5.3.1 Coefficient $k_1$ : fixed ( $k_1 = 0.95$ ) and approximated ( $k_1 = 1$ ) | 88    |

| $5.3.2$ Adaptive $k_1$                                                          | 89    |

| 5.4 Summary                                                                     | 89    |

| Chapter 6: CONCLUSIONS AND FUTURE WORK                                          | 90    |

| 5.1 Conclusions                                                                 | 90    |

| 5.2 Future Scope of Work                                                        | 93    |

## LIST OF FIGURES

| Fig. 1. 1. Geography of global energy demand by region in the new policies scenario (source    | <b>:</b> : |

|------------------------------------------------------------------------------------------------|------------|

| International Energy Agency (IEA), WEO-2016) [1]                                               | . 1        |

| Fig. 1. 2. Energy consumption forecast with the share of various energy resources (source: a   |            |

| book '2052-A Global Forecast for the Next Forty Years') [2].                                   | . 2        |

| Fig. 1. 3. General block diagram of power conversion system with VSI.                          | . 4        |

| Fig. 1. 4. Classification of control schemes for power converters and drives.                  | . 5        |

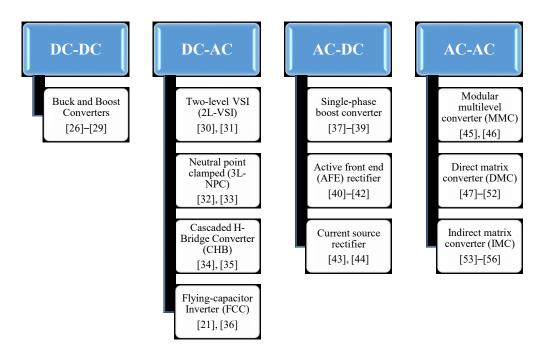

| Fig. 1. 5. A literature review for the application of FCS-MPC in different power converters.   | . 9        |

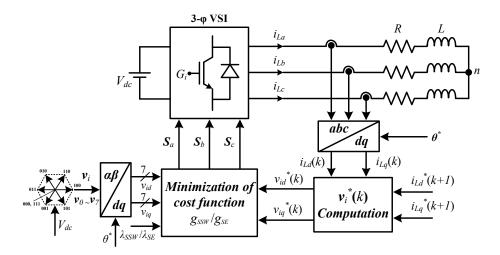

| Fig. 2. 1. General block diagram of FCS-MPC scheme for power converters [32]                   | 18         |

| Fig. 2. 2. Schematic diagram for the current control of three-phase VSI using FCS-MPC          |            |

| [83]                                                                                           | 21         |

| Fig. 2. 3. A flow diagram representing the control algorithm of the FCS-MPC [32]               | 22         |

| Fig. 2. 4. Schematic diagram for the current control of three-phase VSI using FCS-MPC          | 23         |

| Fig. 2. 5. Voltage vectors generated by the inverter.                                          | 24         |

| Fig. 2. 6. A schematic diagram representing the load current control using the FCS-MPC in (a)  | )          |

| $\alpha\beta$ -frame, and (b) $dq$ -frame.                                                     | 27         |

| Fig. 3. 1. Schematic diagram for the current control of three-phase VSI using FCS-MPC          | 31         |

| Fig. 3. 2. Block diagram to demonstrate the modelling steps in the cost function computation   | 1          |

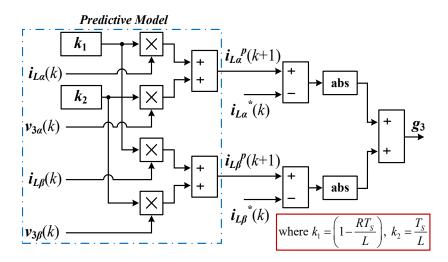

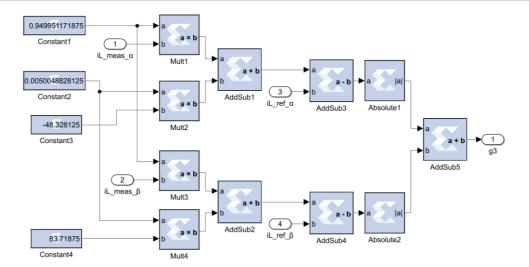

| for the FCS-MPC in $\alpha\beta$ -frame.                                                       | 32         |

| Fig. 3. 3. The modelling steps for the cost function computation developed in the digital      |            |

| platform of XSG for the FCS-MPC in $\alpha\beta$ -frame.                                       | 33         |

| Fig. 3. 4. Block diagram to demonstrate the modelling steps in the cost function computation   | 1          |

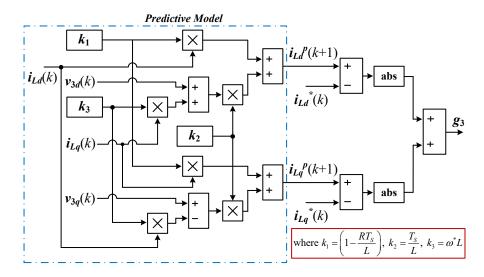

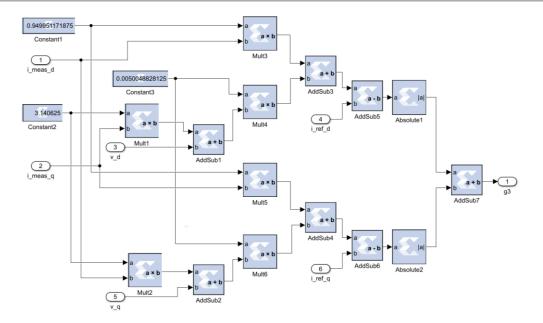

| for the FCS-MPC in dq-frame.                                                                   | 33         |

| Fig. 3. 5. The modelling steps for the cost function computation developed in the digital      |            |

| platform of XSG for the FCS-MPC in dq-frame.                                                   | 34         |

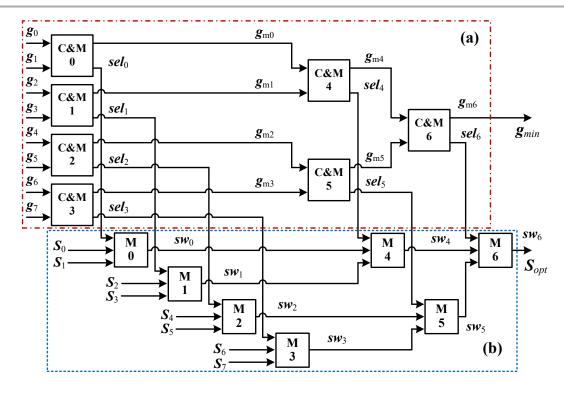

| Fig. 3. 6. Block diagram to represent logic for the (a) selection of minimum of cost function, | ,          |

| and (b) selection of optimum switching state.                                                  | 35         |

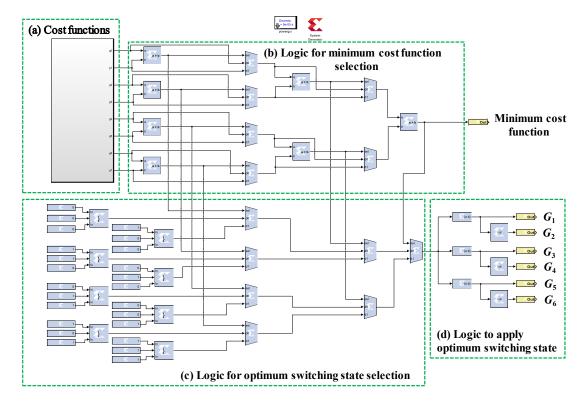

| Fig. 3. 7. XSG modelling of the FCS-MPC: (a) computation of cost function, (b) selection of    | f          |

| minimum cost function, (c) selection of optimum switching state, and (d) application of        |            |

| optimum switching state.                                                                       | 36         |

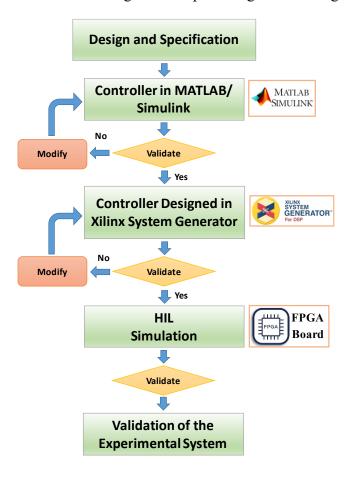

| Fig. 3. 8. Flowchart of HIL co-simulation using FPGA.                                          | 37         |

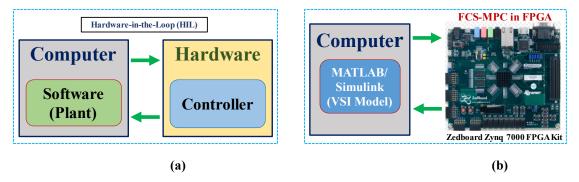

| Fig. 3. 9. HIL co-simulation for controller in hardware (a) general block diagram; (b) VSI     |            |

| interaction with controller in FPGA.                                                           | 38         |

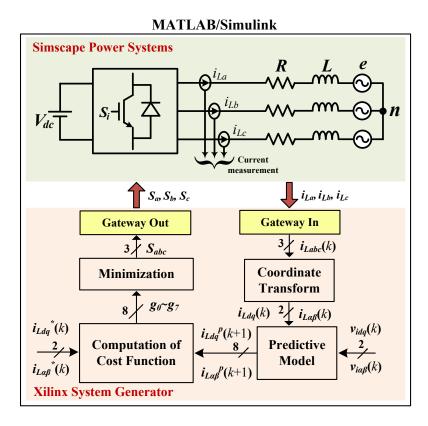

| Fig. 3. 10. FCS_MPC implementation in XSG and HII. co-simulation                               | 38         |

| Fig. 3. 11. Block diagram representation of methodology for simulation                                                    |

|---------------------------------------------------------------------------------------------------------------------------|

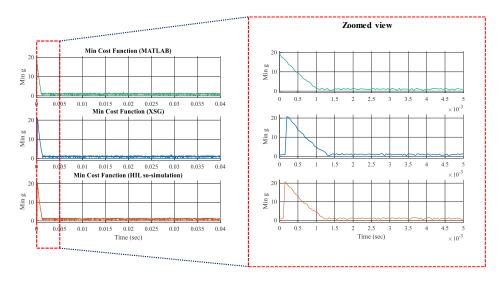

| Fig. 3. 12. Minimum cost function $g_{min}$ in each sampling interval obtained using simulation                           |

| through MATLAB/Simulink, XSG and HIL                                                                                      |

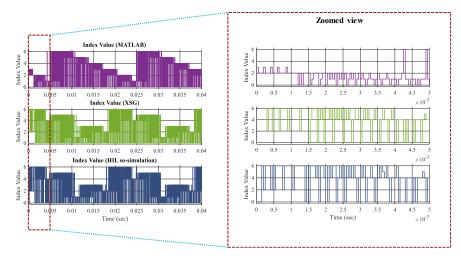

| Fig. 3. 13. Index value of selected optimum switching state $S_{opt}$ obtained using simulation                           |

| through MATLAB/Simulink, XSG and HIL                                                                                      |

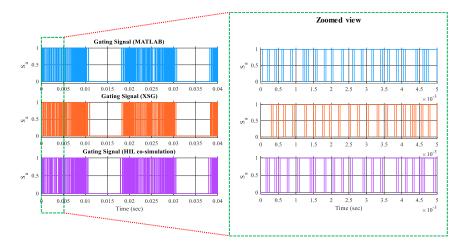

| Fig. 3. 14. Switching signal for upper switch $(S_a)$ of leg 'a' in VSI obtained using simulation                         |

| through MATLAB/Simulink, XSG and HIL                                                                                      |

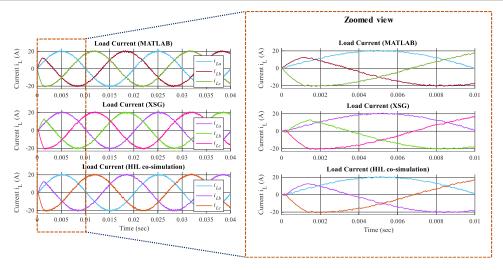

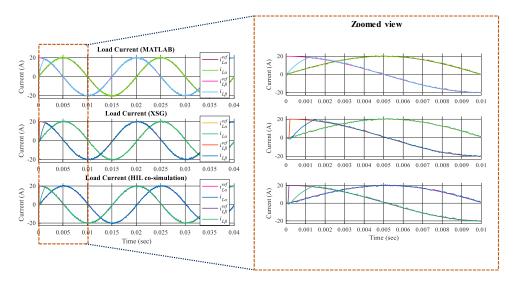

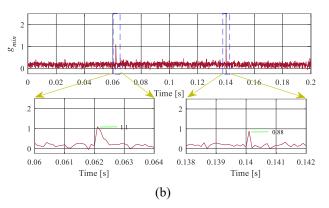

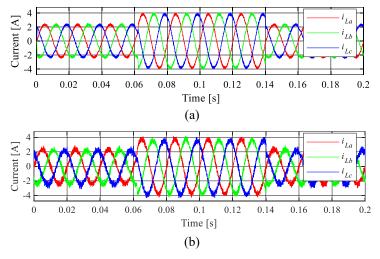

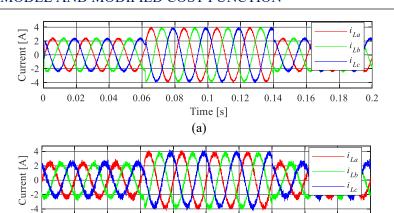

| Fig. 3. 15. Three phase load currents ( $i_{La}$ , $i_{Lb}$ , $i_{Lc}$ ) obtained using simulation through                |

| MATLAB/Simulink, XSG and HIL with $T_S = 50 \mu s$                                                                        |

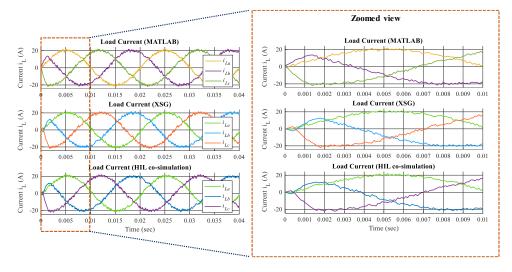

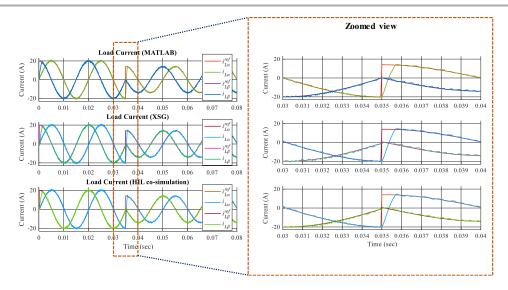

| Fig. 3. 16. Three phase load currents ( $i_{La}$ , $i_{Lb}$ , $i_{Lc}$ ) obtained using simulation through                |

| MATLAB/Simulink, XSG and HIL with $T_S = 100 \mu s$                                                                       |

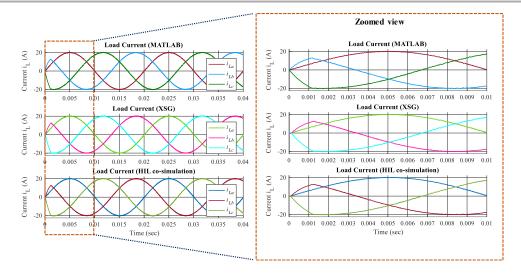

| Fig. 3. 17. Three phase load currents ( $i_{La}$ , $i_{Lb}$ , $i_{Lc}$ ) obtained using simulation through                |

| MATLAB/Simulink, XSG and HIL with $T_S = 20 \mu s$                                                                        |

| Fig. 3. 18. Current tracking for real and imaginary components of load current $(i_{L\alpha \text{ and }}i_{L\beta})$     |

| obtained using simulation through MATLAB/Simulink, XSG and HIL for $T_S = 50 \mu s44$                                     |

| Fig. 3. 19. Current tracking for real and imaginary components of load current $(i_{L\alpha \text{ and }}i_{L\beta})$ for |

| step change in reference obtained using simulation through MATLAB/Simulink, XSG and                                       |

| HIL for $T_S = 50 \mu\text{s}$                                                                                            |

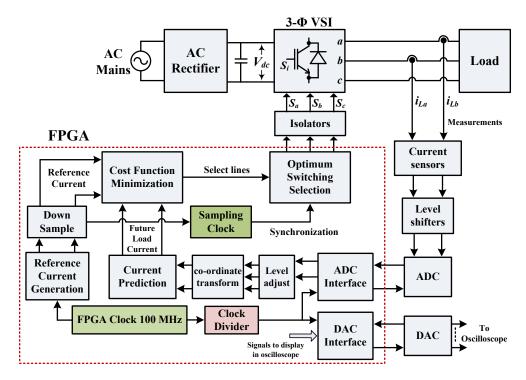

| Fig. 3. 20. FPGA architecture of the FCS-MPC with the schematic block diagram of                                          |

| experimental setup                                                                                                        |

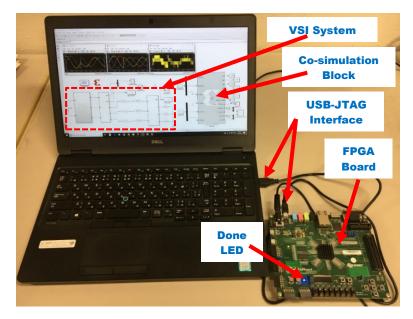

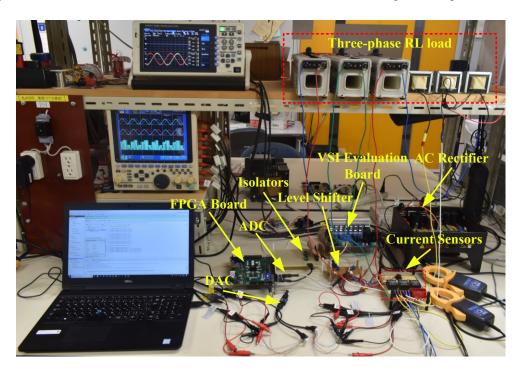

| Fig. 3. 21. Laboratory prototype of the experimental setup                                                                |

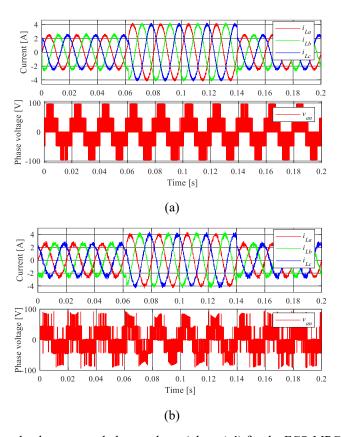

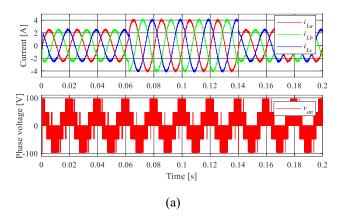

| Fig. 3. 22. Three-phase load current and phase voltage (phase 'a') for the FCS-MPC in $\alpha\beta$ -                     |

| frame through the (a) simulation, and (b) experiment                                                                      |

| Fig. 3. 23. Three-phase load current and phase voltage (phase 'a') for the FCS-MPC in dq-                                 |

| frame through the (a) simulation, and (b) experiment                                                                      |

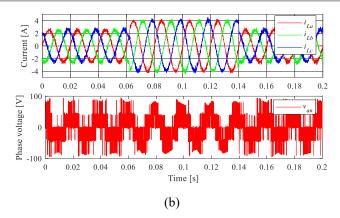

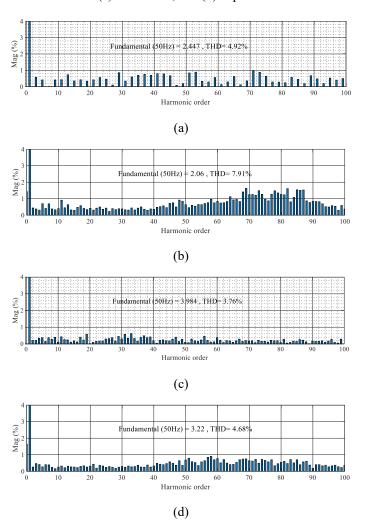

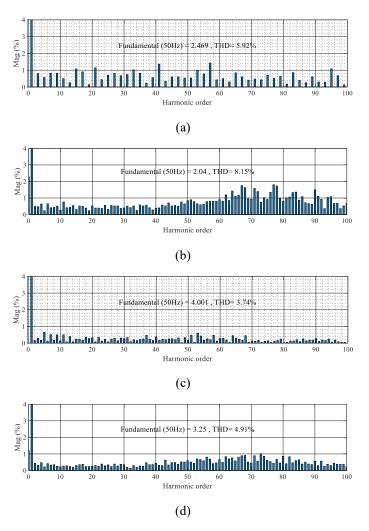

| Fig. 3. 24. THD spectrum in the load current for reference amplitude 2.5 A through (a)                                    |

| simulation, (b) experiment; and for 4 A through the (c) simulation, (d) experiment using the                              |

| FCS-MPC in $\alpha\beta$ -frame                                                                                           |

| Fig. 3. 25. THD spectrum in the load current for reference amplitude 2.5 A through (a)                                    |

| simulation, (b) experiment; and for 4 A through the (c) experiment using simulation, (d) the                              |

| FCS-MPC in dq-frame                                                                                                       |

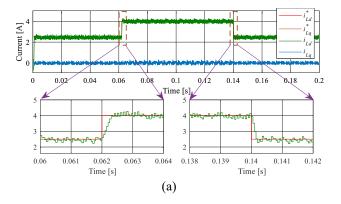

| Fig. 3. 26. Tracking performance of load current $i_{La}$ , $i_{L\beta}$ for the FCS-MPC in $\alpha\beta$ -frame through  |

| the (a) simulation, (b) experiment                                                                                        |

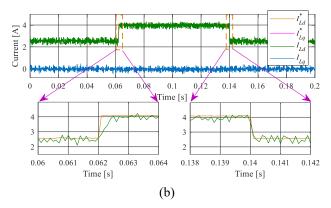

| Fig. 3. 27. Tracking performance of load current $i_{La}$ , $i_{L\beta}$ for the FCS-MPC in $dq$ -frame through           |

| the (a) simulation, (b) experiment                                                                                        |

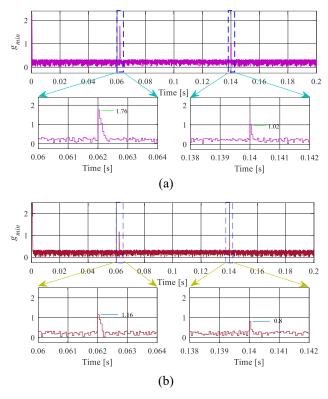

| Fig. 3. 28. Simulation results: The values of minimum cost function $g_{min}$ for the FCS-MPC in                          |

| (a) $\alpha\beta$ -frame and (b) $da$ -frame.                                                                             |

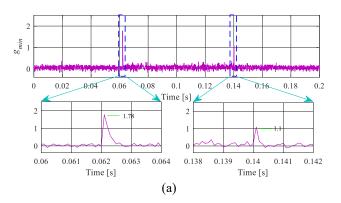

| Fig. 3. 29. Simulation results: The index number of selected optimum switching state $S_{opt}$ in                       |

|-------------------------------------------------------------------------------------------------------------------------|

| each sampling interval for the FCS-MPC in (a) $\alpha\beta$ -frame and (b) $dq$ -frame                                  |

| Fig. 3. 30. Experimental results: The values of minimum cost function $g_{min}$ for the FCS-MPC                         |

| in (a) $\alpha\beta$ -frame and (b) $dq$ -frame.                                                                        |

| Fig. 3. 31. Experimental results: The index number of selected optimum switching state $S_{opt}$ in                     |

| each sampling interval for the FCS-MPC in (a) $\alpha\beta$ -frame and (b) $dq$ -frame                                  |

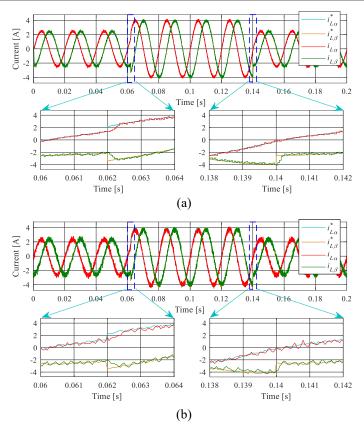

| Fig. 4. 1. Three-phase load current for the FCS-MPC in $\alpha\beta$ -frame with $k_1 = 1$ through (a)                  |

| simulation and (b) experiment                                                                                           |

| Fig. 4. 2. Three-phase load current for the FCS-MPC in $dq$ -frame with $k_1 = 1$ through (a)                           |

| simulation and (b) experiment                                                                                           |

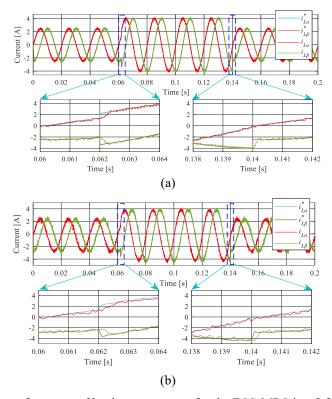

| Fig. 4. 3. Load current tracking performance for the FCS-MPC in $\alpha\beta$ -frame with $k_1 = 1$                     |

| through (a) simulation, (b) experiment                                                                                  |

| Fig. 4. 4. Load current tracking performance for the FCS-MPC in $\alpha\beta$ -frame with adaptive $k_1$                |

| through (a) simulation, (b) experiment                                                                                  |

| Fig. 4. 5. Load current tracking performance for the FCS-MPC in $dq$ -frame with $k_1 = 1$                              |

| through (a) simulation, (b) experiment. 67                                                                              |

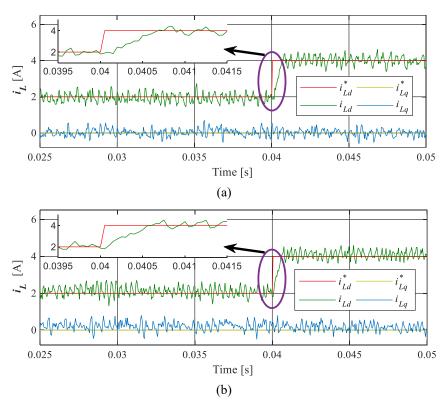

| Fig. 4. 6. Load current tracking performance for the FCS-MPC in $dq$ -frame with adaptive $k_1$                         |

| through (a) simulation, (b) experiment                                                                                  |

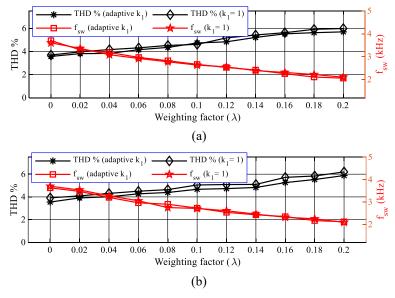

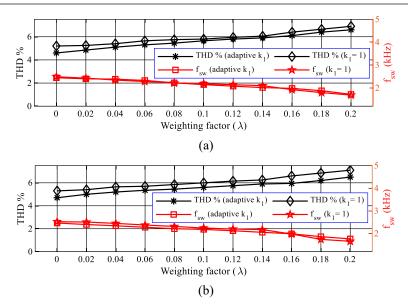

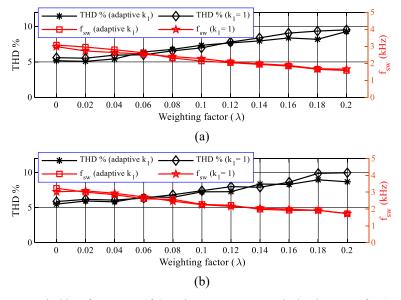

| Fig. 4. 7. Average switching frequency $(f_{sw})$ and percentage THD in load current for $i_L = 4$ A                    |

| during simulation with the FCS-MPC in (a) $\alpha\beta$ -frame, and (b) $dq$ -frame                                     |

| Fig. 4. 8. Average switching frequency $(f_{sw})$ and percentage THD in load current for $i_L = 4$ A                    |

| during experiment with the FCS-MPC in (a) $\alpha\beta$ -frame, and (b) $dq$ -frame                                     |

| Fig. 4. 9. Average switching frequency ( $f_{sw}$ ) and percentage THD in load current for $i_L = 2.5$ A                |

| during simulation with the FCS-MPC in (a) $\alpha\beta$ -frame, and (b) $dq$ -frame                                     |

| Fig. 4. 10. Average switching frequency $(f_{sw})$ and percentage THD in load current for $i_L = 2.5$                   |

| A during experiment with the FCS-MPC in (a) $\alpha\beta$ -frame, and (b) $dq$ -frame70                                 |

| Fig. 4. 11. Schematic diagram of load current control using the simplified FCS-MPC in dq-                               |

| frame using switching state constraint and the proposed constraint                                                      |

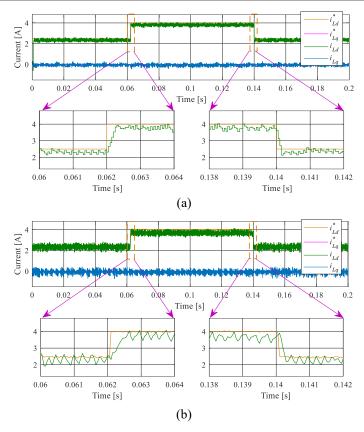

| Fig. 4. 12. Experimental results of load current tracking for the simplified FCS-MPC (a)                                |

| change in switching state constraint ( $\lambda_{SSW} = 0.175$ ), (b) proposed constraint ( $\lambda_{SE} = 3.5$ )74    |

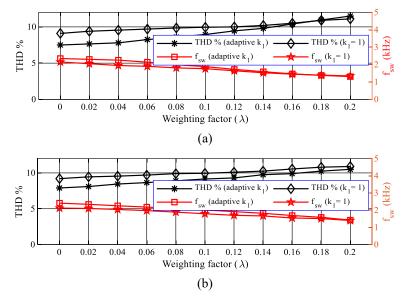

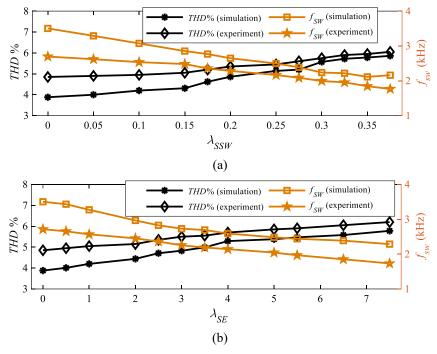

| Fig. 4. 13. Average switching frequency and the percentage THD in the load current vs                                   |

| weighting factors ( $\lambda_{SSW}$ , $\lambda_{SE}$ ) for simplified FCS-MPC (a) change in switching state constraint, |

| (b) proposed constraint                                                                                                 |

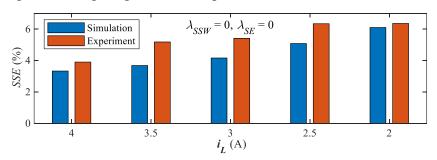

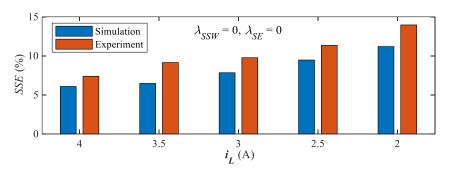

| Fig. 4. 14. SSE performance of simplified FCS-MPC without constraint for $T_S = 50  \mu s$                              |

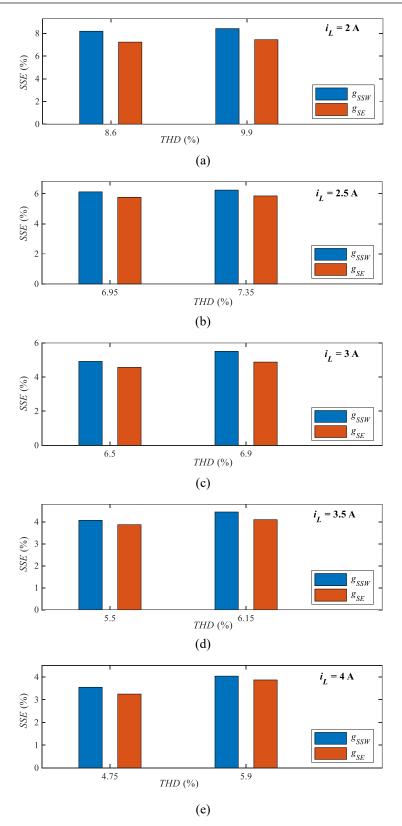

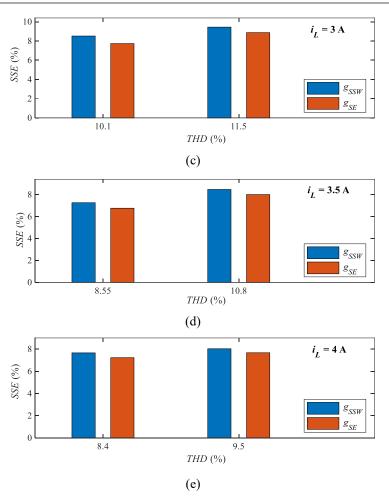

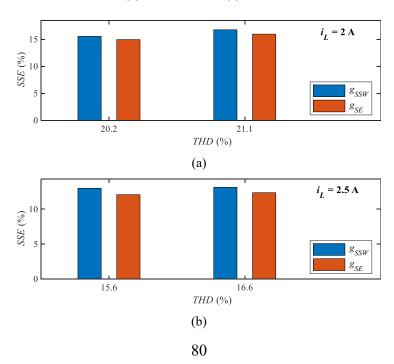

| Fig. 4. 15. Simulation results ( $T_S$ = 50 $\mu$ s) of SSE performance for simplified FCS-MPC with            |

|----------------------------------------------------------------------------------------------------------------|

| the change in switching state constraint $(g_{SSW})$ and the proposed constraint $(g_{SE})$ : (a) $i_L = 2$ A, |

| (b) $i_L = 2.5 \text{ A}$ , (c) $i_L = 3 \text{ A}$ , (d) $i_L = 3.5 \text{ A}$ , and (e) $i_L = 4 \text{ A}$  |

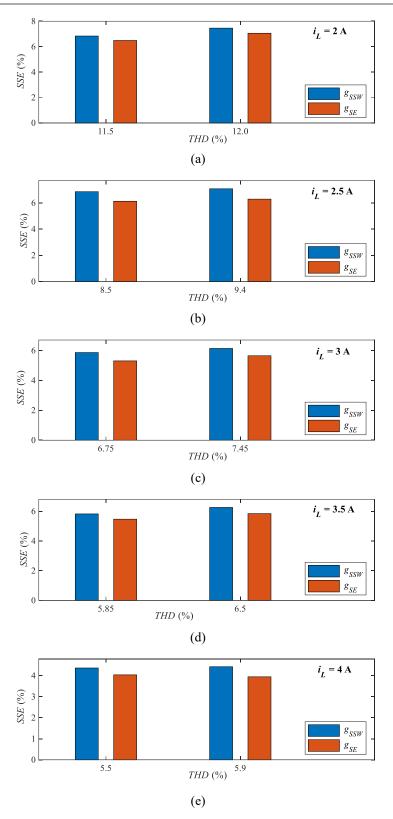

| Fig. 4. 16. Experimental results ( $T_S$ = 50 $\mu$ s) of SSE performance for simplified FCS-MPC               |

| with the change in switching state constraint $(g_{SSW})$ and the proposed constraint $(g_{SE})$ : (a) $i_L =$ |

| 2 A, (b) $i_L = 2.5$ A, (c) $i_L = 3$ A, (d) $i_L = 3.5$ A, and (e) $i_L = 4$ A                                |

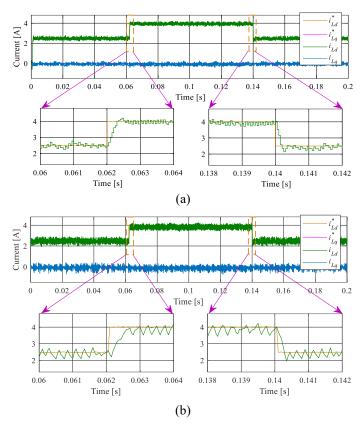

| Fig. 4. 17. SSE performance of simplified FCS-MPC without constraint for $T_S$ = 100 $\mu$ s 79                |

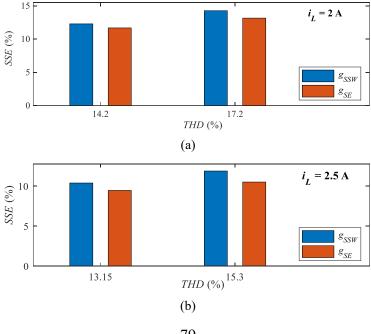

| Fig. 4. 18. Simulation results ( $T_S$ = 100 $\mu$ s) of SSE performance for simplified FCS-MPC with           |

| the change in switching state constraint $(g_{SSW})$ and the proposed constraint $(g_{SE})$ : (a) $i_L = 2$ A, |

| (b) $i_L = 2.5 \text{ A}$ , (c) $i_L = 3 \text{ A}$ , (d) $i_L = 3.5 \text{ A}$ , and (e) $i_L = 4 \text{ A}$  |

| Fig. 4. 19. Experimental results ( $T_S = 100 \mu s$ ) of SSE performance for simplified FCS-MPC               |

| with the change in switching state constraint $(g_{SSW})$ and the proposed constraint $(g_{SE})$ : (a) $i_L =$ |

| 2 A, (b) $i_L = 2.5$ A, (c) $i_L = 3$ A, (d) $i_L = 3.5$ A, and (e) $i_L = 4$ A                                |

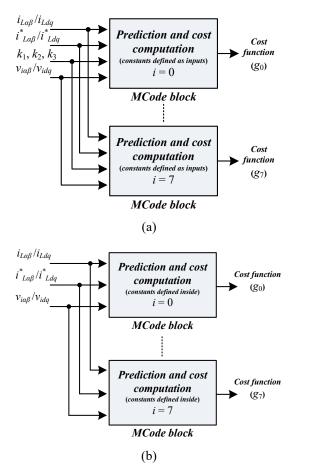

| Fig. 5. 1. Development methodologies for the FCS-MPC in XSG using MCode block (a)                              |

| case-I, (b) case-II86                                                                                          |

## LIST OF TABLES

| Table 2. 1. Gating signals of inverter power switches.                                               | . 23 |

|------------------------------------------------------------------------------------------------------|------|

| Table 2. 2. Switching states and voltage vectors.                                                    | . 24 |

| Table 3. 1. Simulation parameters for the three-phase VSI system.                                    | . 40 |

| Table 3. 2. Parameters for system implementation.                                                    | . 48 |

| Table 4. 1. Performance of the FCS-MPC in $\alpha\beta$ -frame.                                      | . 64 |

| Table 4. 2. Performance of the FCS-MPC in <i>dq</i> -frame.                                          | . 64 |

| Table 5. 1. MATLAB code for the prediction and cost computation in $\alpha\beta$ -frame for case-I   | . 85 |

| Table 5. 2. MATLAB code for the prediction and cost computation in $\alpha\beta$ -frame for case-II. | . 86 |

| Table 5. 3. FPGA resource utilization for the development of the FCS-MPC in $\alpha\beta$ -frame     | . 87 |

| Table 5. 4. FPGA resource utilization for the development of the FCS-MPC in dq-frame                 | . 87 |

#### **PUBLICATIONS**

#### **Journal Papers**

- (1) V. K. Singh, R. Tripathi, and T. Hanamoto, "HIL Co-simulation of Finite Set-Model Predictive Control using FPGA for a Three-Phase VSI System," *Energies*, vol. 11, no. 4, 909, April 2018.

- (2) V. K. Singh, R. Tripathi, and T. Hanamoto, "FPGA-Based Implementation of Finite Set-MPC for a VSI System using XSG-Based Modeling," *Energies*, vol. 13, no. 1, 260, January 2020.

- (3) V. K. Singh, R. Tripathi, and T. Hanamoto, "Implementation Strategy for Resource Optimization of FPGA-Based Adaptive Finite Control Set-MPC using XSG for a VSI System," submitted in *IEEE Journal of Emerging and Selected Topics in Power Electronics* (Revised manuscript submitted).

- (4) V. K. Singh, R. Tripathi, and T. Hanamoto, "Modified Cost Function Based Finite Control Set Model Predictive Control for Improved Steady-State Error," under review in *IEEE Access*.

#### **Conference Papers**

#### **Authored**

- (1) V. K. Singh, R. Tripathi, and T. Hanamoto, "FPGA-based Development of Finite State-MPC for Three-Phase Grid-Connected VSI System", in *10th International Conference on Power Electronics* (ICPE 2019–ECCE Asia), BEXCO, Busan, Korea, May 27–30, 2019.

- (2) V. K. Singh, R. Tripathi, and T. Hanamoto, "Modified Cost Function based Switching Frequency Reduction Analysis for Finite State–MPC," in *IEEE Power Electronics, Drives and Energy Systems Conference* (PEDES 2018), IIT Madras, Tamil Nadu, India, Dec 18–21, 2018.

- (3) V. K. Singh, R. Tripathi, and T. Hanamoto, "Xilinx System Generator Based Modelling of Finite State MPC," in *9th International Power Electronics Conference* (IPEC 2018–ECCE Asia), Niigata, Japan, May 20–24, 2018.

- (4) V. K. Singh, R. Tripathi, and T. Hanamoto, "Model-based Design Approach for Implementation of Finite State MPC," in *Proceedings of the 13th IEEE Conference on Industrial Electronics and Applications* (ICIEA 2018), Wuhan, China, May 31–June 02, 2018.

- (5) V. K. Singh, R. Tripathi, and T. Hanamoto, "Comparative Analysis of Finite Control Set MPC for Voltage Source Inverter," in *5th International Conference on Electric Power and Energy Conversion Systems* (EPECS 2018), Kitakyushu, Japan, April 23–25, 2018.

#### Co-authored

- (1) I. Mishra, R. Tripathi, V. K. Singh, and T. Hanamoto, "Discrete Adaptive HCC based FS-MPC with Constant Switching Frequency for PMSM Drives", in 22<sup>nd</sup> International Conference on Electrical Machines and Systems (ICEMS 2019), Harbin, China, Aug 11–14, 2019.

- (2) I. Mishra, R. Tripathi, V. K. Singh, and T. Hanamoto, "A Hardware-in-the-Loop Simulation Approach for Analysis of Permanent Magnet Synchronous Motor Drive", in *10<sup>th</sup> International Conference on Power Electronics* (ICPE 2019–ECCE Asia), BEXCO, Busan, Korea, May 27–30, 2019.

- (3) I. Mishra, R. Tripathi, V. K. Singh, and T. Hanamoto, "Comparative Analysis of Continuous PWM and Discontinuous PWM for PMSM Drive", in 6<sup>th</sup> International Symposium on Applied Engineering and Sciences (SAES 2018), Kitakyushu, Japan, Dec 15–16, 2018.

#### **INTRODUCTION**

#### 1.1 Energy Demand and Challenges

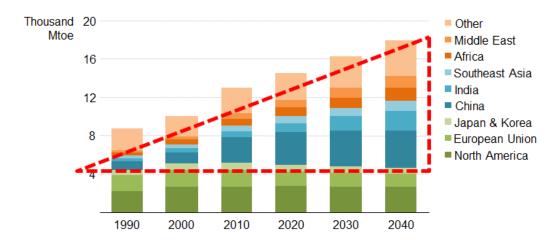

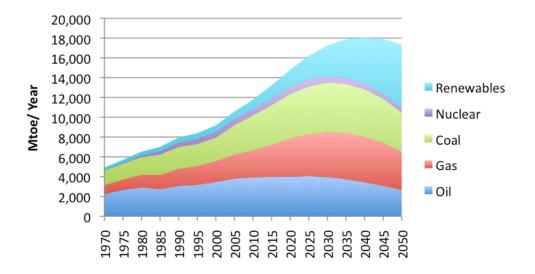

In recent years, the energy demand has been growing at a rapid rate, because of the population, technological advancement, and economic growth. The global energy demand will continue to increase further due to the rapid increase of consumption in domestic as well as industries. Much of the energy demand is concentrated in developing countries (India, China, and others) according to the geography of global energy demand shown in Fig. 1.1, where rising prosperity and improving living standards support increasing energy consumption per head [1]. Since 1970, the energy demand has been mainly satisfied by conventional or non-renewable energy sources such as fossil fuels (mainly oil, coal, and gas) as shown in Fig. 1.2. According to the energy consumption forecast, the increased energy demand will be satisfied mainly by fossil fuels until 2030 [2]. However, dependency on fossil fuels will be decreased significantly due to the revolutionary efforts in other non-conventional energy resources.

Fig. 1. 1. Geography of global energy demand by region in the new policies scenario (source: International Energy Agency (IEA), WEO-2016) [1].

Fig. 1. 2. Energy consumption forecast with the share of various energy resources (source: a book '2052-A Global Forecast for the Next Forty Years') [2].

The higher consumption of fossil fuels leads to higher greenhouse gas emissions, particularly carbon dioxide (CO2), which contribute to global warming. Moreover, the depletion of conventional energy sources has become important matters of global concern due to the rise in energy demand. Hence, while accompanied by greater prosperity, rising demand creates new challenges. The customized living standards, energy security concerns, provide access to modern energy services, use energy more efficiently, protect the global environment and ensure reliable energy supplies, etc. are the possible challenges. A sustainable energy future will require new thinking and new systems – essentially a transformation in the way we produce, deliver and consume energy [3]. The energy generation from non-conventional or renewable sources has to play a major role to fulfill energy demand and to tackle environmental issues. Some adequate renewable sources such as solar, wind, biomass, ocean, and geothermal, are capable of accomplished clean and green energy without affecting the environment. Solar photovoltaic (PV) and wind are prominent among available renewable sources to generate power.

#### 1.2 Role of Power Electronics

To harvest the power from those renewable energy sources, a suitable high-efficiency energy conversion system for the industrial processes are essential. Power Electronics plays a vital role in the control and conversion of electric power with the smart application of solid-state devices [4]. Power electronics have already found an important place in modern technology and are now used in a great variety of high power

product, including heat controls, light controls, electric motor control, power supplies, vehicle propulsion system, high voltage direct current (HVDC) systems and to name a few. The silicon power semiconductor devices such as thyristor, power MOSFET, insulated gate bipolar transistor (IGBT), Triac, gate turn-off thyristor (GTO), and integrated gate-commuted thyristor (IGCT) have been utilized according to the applications.

Power electronics technology is associated with efficient energy conversion as well as control and conditioning of electrical energy from source to load. Power electronics converters are the backbone of the conversion systems that convert the one form of electrical power in another form such as conversion from AC to DC, altering the magnitude, phase or frequency of voltage and current, etc. The improvement in the efficiency of power electronics converters is one of the challenging topics. In this process, the key steps are being taken by researchers such as the evolution of faster devices, improved topologies, and advanced controls. The power converter that converts DC to AC (inverter) has a wide variety of practical applications including adjustable speed drives (ASD), uninterruptible power supplies (UPS), flexible AC transmission systems (FACTS), and voltage compensators [5]. There is two most common type of inverters: voltage source inverter (VSI) and current source inverter (CSI). According to their names, VSIs are fed with constant voltage and CSIs are fed with constant currents.

VSIs are one of the common types of inverters that have been used for various applications such as renewable energy systems, AC motor drives, DC battery, induction heating, AC UPS, high voltage DC (HVDC) power transmission, active power filter, etc. [6]. One very common application of VSI is commercially available inverter units used in homes and offices to power some essential AC loads in case the utility AC supply gets interrupted. The battery supply is used as the input DC voltage source and then the DC voltage is converted into AC voltage of desired frequency as well as amplitude. There are many classifications of VSIs according to different criteria. They can be classified based on the number of phases in the output (commonly single-phase and three-phase). Another type of VSI classification is based on their ability to control the output parameters such as

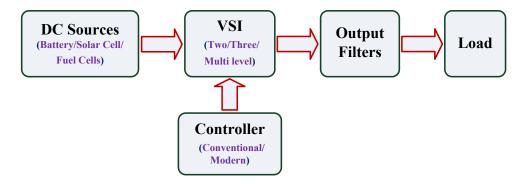

Fig. 1. 3. General block diagram of the power conversion system with VSI.

frequency, voltage, harmonic content. VSIs may also be classified according to their topologies. Some inverter topologies are suitable for low and medium voltage applications (e.g. two-level three-phase VSI) whereas some others are suitable for high voltage applications (e.g. multilevel inverter topologies).

The performance of VSIs is dependent on the controller used to control the desired parameters (e.g. voltage, current, torque, flux). The desired control objectives are satisfied through the appropriate switching of power devices used in the VSI. A general block diagram of a VSI system is depicted in Fig. 1.3. The DC input supply for the VSI system can be connected through the battery, solar PV or fuel cells. The output filters are generally utilized for the desired quality of sinusoidal output voltage and current. The controller is a driving component of the power conversion system. Several control schemes have been utilizing according to the application as well as the power devices. Historically, thyristors with lower switching frequencies have been controlling by regulating the firing angle with the analog control circuit. The analog control circuits were later on replaced by digital control platforms with the possibility of implementing more advanced control schemes with the introduction of power transistors with faster switching frequencies [4]. The control schemes for power converters and drives are briefly summarized in the next subsection.

#### 1.3 Power Converter Control

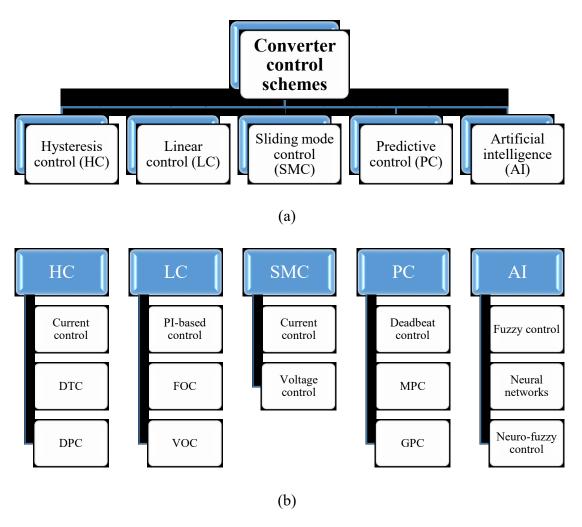

The several conventional and modern control schemes have been studied and proposed in the literature to improve the performance of power converters. The control schemes for power converters and drives are summarized in Fig. 1.4 [7], [8]. The conventional control

Fig. 1. 4. Classification of control schemes for power converters and drives.

schemes are hysteresis control and linear control (mainly pulse width modulation (PWM), space vector modulation (SVM)). There are some categories of modern control strategies such as sliding mode control (SMC), model predictive control (MPC) and artificial intelligence (AI).

Hysteresis control is one of the mature control schemes for industrial applications due to simple nature. It is the type of non-linear control and the switching signals of the power devices are determined by the comparison of the measured variable with the reference variable. The concept is to keep the error within the specified tolerance called hysteresis band/error band. The inversely proportional relation of the switching frequency and hysteresis band results in the varying switching frequency corresponding to the upper and lower specified hysteresis band. This scheme provides a fast dynamic response, but, the variable switching frequency results in a spread spectrum and resonance problems in some applications. Normally this scheme is implemented through analog circuits due to its inherent nature, however, to implement it in a digital

platform, a very high sampling frequency is required. This control scheme has been utilized not only for the simple current control applications but also for complex applications of direct torque control (DTC) [9], [10] as well as direct power control (DPC) [11].

Linear control behavior of power converters can be obtained by a modulation technique such as pulse width modulation (PWM) or space vector modulation (SVM) [12], [13]. SVM is just a variation of regular sampled PWM. The PWM signal is generated by comparing a lower frequency reference signal to a high-frequency carrier. The linear control scheme with a modulation technique normally requires additional coordinate transformations. In a linear control of power converters and drives, there are normally three types of widely used control schemes: proportional-integral (PI) based controllers for both current and voltage control, voltage-oriented control (VOC) [14] for grid-connected inverters and field-oriented control (FOC) [10], [15] for motor drive applications. These control schemes have been widely used in the industries, however, these can be challenging for some converter topologies such as matrix converters and multi-level converters due to several design steps with the additional modulation stage that increases complexity.

Sliding mode control (SMC) is a non-linear control scheme where the control action is discontinuous and follows a predefined control switching law [16], [17]. It works on the principle that the system states can be driven onto a surface in the state space, called a sliding surface. There are mainly two parts of controller design. In the first part, the sliding surface is designed such that the sliding motion satisfies design requirements. The latter part involves the selection of a control law that results in switching surface attractive to the system state. This scheme is suited to control the effect of model parameter uncertainties, disturbance, and nonlinearity in a system. There are some remarkable features of SMC such as accuracy, robustness and easy tuning.

Predictive control has been receiving popularity for the control of power converters and drives [18]–[20]. It comprises a wide family of controllers with different approaches. Predictive control is characterized by the use of a model of the system to predict the future behavior of the controlled variables, and the use of an optimization criterion for selecting the optimum actuation. The deadbeat control, one of the basic predictive control, uses the idea where a prediction is made for the optimum actuation

so that the error between the reference and the controlled variables will be zero at the next sampling instant for the first-order system. Among the various classifications of predictive control, model predictive control (MPC) is one of the most popular control schemes due to its several attractive features. MPC is the main focus of this thesis and the detailed explanation with the literature review is presented in the next subsection.

#### 1.4 Literature Background

MPC is considered as an advanced method of process control for complex multipleinput multiple-output (MIMO) process. The process control using MPC has been performed in the process industries such as chemical plants and oil refineries with low sampling requirements since the 1980s. After that, the idea of MPC was applied in the field of power electronics considering high power systems with low switching frequency. Since the last decade, the availability of high-speed microprocessors has triggered research in MPC for power electronics and drive applications. Although MPC implementation requires high computations, it has gained attention in the power electronic research community due to its distinctive features such as fast dynamic response, intuitive and logical concept, handling complex MIMO cases, flexibility in constraint inclusion and handling system nonlinearities. The role of MPC in the evolution of power electronics was presented in [18] and a comparative description is given with the different control schemes. In [19], a wide review of the applications of MPC in power electronics is presented considering various applications such as gridconnected converters using active front end (AFE) and active power filter (APF), control of a matrix converter, control of multilevel inverters, inverters with output LC filter and high-performance drives. In [20], a survey of various MPC schemes was presented for the power converters and drives with a detailed comparative analysis including future trends.

The basic principle of MPC is based on a model to predict the future behavior of the control variables over a prediction horizon. Then, the control function or cost function is evaluated for the desired behavior of the system and the optimum actuation is selected according to the minimum cost function. One of the major deciding factors for MPC performance is the model precision that gives an accurate prediction. MPC strategies are broadly classified as continuous control set-MPC (CCS-MPC) and finite control set-MPC (FCS-MPC). The CCS-MPC computes continuous control signals

with constant switching frequency by using a modulator, whereas FCS-MPC implements the MPC algorithm by utilizing the discrete nature of the power converter and applies the switching signals directly to the power converter without the need for an external modulator that results in variable switching frequency. FCS-MPC is designed to reduce the computational burden of the algorithm by utilizing the set of possible switching states of power converters for solving the optimization problem online.

One of the characteristics of FCS-MPC is to control multiple variables using a single cost function and is more favorable for controlling complex power converters and electric motor drive systems. Moreover, the direct application of optimized control action without need a modulation stage is an awesome feature of this control scheme. In the literature FCS-MPC is sometimes termed as finite-set model predictive control (FS-MPC) [21], [22] or finite-state model predictive control (FS-MPC) [23], [24] or direct model predictive control (D-MPC) [25]. Various literatures have reported with FCS-MPC application in power converters such as two-level VSI [30], [31], three-level neutral point clamped (NPC) [32], [33], cascaded H-bridge (CHB) multilevel converters [34], [35], flying-capacitor converter (FCC) [21], [36], AFE rectifiers [40]–[42], matrix converters [47]–[56] etc. A list of different power converter topologies is depicted in Fig. 1.5.

The application of FCS-MPC as current control of a two-level inverter is discussed in [30]–[32]. Similarly, the current control of three and four-level inverters using the FCS-MPC is presented in [31]–[33], [57] and [58] respectively. A comparative assessment of FCS-MPC with linear current control schemes based on the comparable switching frequencies is presented in [30], [59]. The FCS-MPC has been implemented for the voltage control of converters with second-order LC output filters in [60]–[62].

Despite several attractive features, the FCS-MPC encounters some major drawbacks. The variable switching frequency is one of the drawbacks of the FCS-MPC scheme which causes switching losses and unwanted resonances [32], [63]. Moreover, variable switching

Fig. 1. 5. A literature review for the application of FCS-MPC in different power converters.

frequency results in a spread spectrum of voltage and current over a wide range of frequencies. In FCS-MPC, the sampling time for the discretization of the converter model governs the switching frequency of the converter and the system performance improves with lower sampling time i.e. higher sampling frequency. However, the higher sampling frequency is one of the causes of higher switching frequency that results in even higher switching losses [63]. The functionality of incorporating additional parameters inside a cost function can be utilized for switching frequency reduction to optimize the switching frequency with primary control parameters simultaneously and to implement the system with lower sampling time depending on the permissible maximum switching frequency of the power devices. The problem of switching frequency has been addressed and some methodologies have been presented towards the reduction of switching frequency for multilevel active rectifiers [64], cascaded H-bridge multilevel converter [65], modular multilevel converter [66] and three-level inverter-fed induction motor drives [67]. The fundamental idea to minimize control effort with switching frequency reduction has been studied and analyzed with the inclusion of constraint inside the cost function such as the change in switching state to control the number of commutations of the power switches [32], [68] and change in voltage vector [32], [69]. Moreover, the computational burden for change in switching state constraint is comparatively low and preferred for implementation as compared to the change in voltage vector constraint.

Another issue with FCS-MPC is the nonzero steady-state error (SSE). This error is more significant when operated with lower switching frequency or lower amplitude of current reference [70-72]. In [70], the concepts of intermediate sampling, as well as integral error term, were proposed to face the problem of SSE and results were presented for the current control of the four-quadrant chopper converter. In [71], the problem of SSE during model parameter mismatch was addressed and an approach to incorporate past current errors as a constraint inside a cost function with a variable weighting factor was proposed towards the elimination of SSE.

In general, dedicated constraints for the reduction in average switching frequency and SSE are incorporated inside a cost function in conventional FCS-MPC. Nevertheless, that ultimately increases the computational burden. An approach presented in [73] for modified FCS-MPC to reduce the computational burden of the conventional FCS-MPC by the elimination of the current prediction step. In the modified FCS-MPC, the reference voltage vector is evaluated once in each sampling interval as a single current prediction. In addition, change in switching state constraint is incorporated with modified FCS-MPC for the reduction of the average switching frequency. However, the SSE is not considered and compared with conventional FCS-MPC. It is desirable to achieve improved SSE with a reduction in average switching frequency considering the computational burden for implementation of the FCS-MPC.

Moreover, due to the high computational requirements, practical implementations of predictive control for power converters mainly depend on micro-processing solutions such as digital signal processor (DSP) [18]–[20]. The FCS-MPC algorithm can be implemented with a single prediction horizon that makes it one of the most suitable schemes of MPC due to less computational requirements than other MPC schemes and ease of implementation. However, real-time implementation of FCS-MPC encounters computational delay issues when the number of switching states increases in a power converter (e.g. multilevel converter [33]–[36]) and hence, requires efforts to overcome computational issues. The computations required for the implementation of an algorithm should strictly complete within a given sampling interval. However, delay in the computation of optimum switching state is a concern that deteriorates the quality of waveforms [30], [74]. To cope with this issue, delay compensation techniques have been often used to compute the optimum switching state within the specified sampling

interval [75], [76]. Nevertheless, delay compensation techniques encounter additional issues of an increased computational burden and average switching frequency [75].

Field programmable gate array (FPGA) is a pragmatic choice for the implementation of MPC because of parallel processing capability [21], [77]–[82]. The real-time controller implementation using FPGA requires the hardware description language (HDL) code for the particular system. However, writing specific HDL codes needs special training and hence, it is considered a complex and time-consuming task even for skilled researchers or engineers with an increase in the level of controller complexity [83], [84]. The different alternative ways to get the HDL code of the system have been utilized for the real-time implementation of the MPC. In [77], a comparative analysis among various digital control platforms including FPGA is presented for the implementation of model predictive control and different implementation approach is adopted for FPGA-based system implementation. In [78], an FPGA platform of NI-CRIO reconfigurable system is utilized to implement MPC for a back-to-back converter. The FPGA implementation of MPC is performed using a model-based design (MBD) through MATLAB/Simulink in [79], [80] and the FPGA code was generated with the help of hardware description language (HDL) coder functionality of Simulink. In [81], a high-speed FCS-MPC implementation is presented with a control algorithm coded in C++ using PROTOIP toolbox and HDL code was generated through Xilinx Vivado HLS. Xilinx system generator (XSG) as a digital simulator adopting the MBD platform was used to implement an FPGA-based predictive current controller in [21], [82]–[85].

The XSG platform provides a virtual FPGA environment for the designing, testing, and development of digital controllers. The integrated platform of MATLAB/Simulink-XSG provides the functionality of automatic HDL code generation that can be further utilized for the straightforward implementation of FPGA-based experimental system prototypes without the additional knowledge of HDL programming [86]–[88]. XSG provides a modelling-based design approach for digital system implementation. Therefore, XSG-based system modelling is required for the development of real-time systems using FPGA through automatic HDL code generation. Further, the recent availability of a model-based FPGA design platform integrated with MATLAB/Simulink provides the functionality of hardware-in-the-loop (HIL) cosimulation.

1.5 Objectives INTRODUCTION

In addition to the implementation approach, FPGA resource utilization is another key aspect of FPGA-based system control implementation. The system control implementation based on FPGA resource utilization is compared in [81] and [82] for Xilinx FPGA. In [81], the prediction horizon is considered for the comparison of FPGA resource utilization. In [82], semi-parallel and fully serial implementation approaches for MPC are adopted and resource utilization is compared for the same. The look-up tables (LUTs), flip-flops and DSP slices are the main digital logic indices that considered for resource utilization in the aforementioned papers. However, a different approach is adopted for FPGA-based control implementation.

There is a possibility to adopt different implementation strategies for a specific FPGA implementation approach to enhance resource utilization. In this way, the MBD approach can be advantageous by allowing different implementation strategies under the same environment and to compare the FPGA resource utilization. Moreover, the MBD approach provides better system visualization and easy debugging that is appealing for rapid controller prototyping.

#### 1.5 Objectives

The various conventional, as well as modern control schemes, have been applied to different power converters for the specific control objectives as discussed in the previous subsections. The control schemes have to deal with various pros and cons, however, every control scheme has its distinctive characteristics that make the particular control scheme more suitable for a specific application. MPC, as a modern control scheme, is used in this study to have an insight into the distinctive characteristics. The objectives that are taken into account and the key contribution of the research are as follows:

The first procedure is to review various literature related to the MPC control applied to different power converters and to search for the issues related to the control. After that, to understand the algorithm of FCS-MPC that is one of the most popular classifications of MPC and to implement it for two-level VSI using MATLAB/Simulink. As the real-time implementation of FCS-MPC is performed on digital platforms, the first objective is to map the control algorithm on to a digital simulator considering an FPGA-based implementation, an alternative way to handle the computational burden of the control algorithm. In order to get a hassle-free HDL code

1.5 Objectives INTRODUCTION

required for FPGA to perform the real-time implementation, there is a need to develop the controller on to a digital simulator having the functionality of an automatic HDL code generation from the developed controller. XSG, as a digital simulator of Xilinx, is used in this work for the design and development of the controller, however, a modelling-based approach is required for the controller design considering the MBD platform of the XSG. The step-by-step validation with the MATLAB/Simulink design is required through simulations for the precise design.

Before the actual experimental system implementation, an intermediate level of system verification between the software simulation and the actual experimental system implementation using the HIL simulation technique is an effective process that may help to prevent the system failure or any component damage that occurs with direct experimental system implementation. As XSG also provides the functionality of HIL co-simulation, the controller performance is validated in this work using this functionality as well.

The key issue of high switching frequency obtained during FCS-MPC implementation with high sampling frequency for enhanced system performance is also considered in this work. In order to have reduced switching frequency, a constraint for a reduction in the average switching frequency of the converter is incorporated inside the same cost function together with the primary control objectives (voltage or current). In this way, the system can be implemented with a higher sampling frequency depending on the permissible maximum switching frequency of the power devices. The performance of the controller with the constraint aiming switching frequency reduction is validated through the simulation as well as real-time implementation using FPGA.

The performance of the FCS-MPC is highly dependent on the model used for the prediction of the control variables that depend on the system parameters. Any change in system parameters because of any reasons leads to a model parameter mismatch. Considering the issue of model parameter mismatch in the FCS-MPC implementation, an approach is proposed to compensate for the effect of change in model parameters during physical system implementation. The performance is verified through the simulation and experimental results.

Apart from the issue of model parameter mismatch in the FCS-MPC, an issue of a non-zero steady-state error (SSE) is a concern for the FCS-MPC. This error is more

prominent when the system is operated with lower switching frequency or lower reference currents. The functionality of constraint inclusion inside a single cost function has been normally used to control the additional parameters together with the primary control parameters, however, the dedicated constraints are required to handle the individual objectives. In this work, a modified cost function based on a novel constraint is proposed considering the improvement in SSE together with a reduction in the switching frequency. To validate the effectiveness of the proposed constraint, a comparative analysis is presented with the constraint of a change in switching state.

The FPGA resource utilization is another key aspect of the FPGA-based system control implementation considering an optimum design and development of the controller to reduce the overall resource requirements. Considering the same issue, there is a need to analyze the design by incorporating different implementation strategies aiming reduction in the overall FPGA resource utilization. An analytical approach based on implementation strategies using the MBD approach is adopted in this study to determine the appropriate strategy considering a reduction on FPGA resources.

#### 1.6 Organization and Overview

The dissertation is divided into the following chapters:

#### **Chapter 1: Introduction**

This chapter presents an overview of world energy demand and future challenges, role of power electronics to fulfill the energy demand and to solve energy issues, the different control schemes used to handle the various control objectives of the power electronic converters, and applications of model predictive control (MPC) in power electronics that is the main controller used in this work. Moreover, detailed literature background of finite control set-MPC (FCS-MPC) with the fundamental concepts is presented including the objectives of the dissertation.

#### **Chapter 2: Finite control set-model predictive control**

This chapter presents the working principle of the FCS-MPC algorithm including the formulation of the discrete-time model of a three-phase two-level voltage source inverter (VSI). The predictive model and design of cost function for load current control of the three-phase VSI are presented for the FCS-MPC in stationary  $\alpha\beta$  as well

as rotating dq coordinates. The modelling and implementation of the FCS-MPC in both frames are discussed in the next chapter.

#### Chapter 3: Model-based controller design and HIL simulation

A model-based design (MBD) approach for the design and development of the FCS-MPC algorithm is presented in this chapter. Moreover, the controller design in a digital simulator of the Xilinx system generator (XSG) is presented considering the straightforward FPGA-based system implementation. After the controller developed in XSG, the controller performance is validated through the simulation results and a comparative analysis is presented with the controller developed in MATLAB/Simulink.

This chapter also presents the hardware-in-the-loop (HIL) simulation methodology to validate the digitally developed controller. The controller performance is further verified through the experiment conducted with FPGA-based system implementation. The system implementation without any constraint is considered in this chapter considering the only primary objective of the load current control of the three-phase VSI system. The results obtained through the real-time experiments are compared with the results obtained through the HIL simulation for the proper validation of the experimental results.

## Chapter 4: Advanced FCS-MPC: Adaptive predictive model and modified cost function

This chapter presents an approach to compensate for the effect of any system parameter mismatch that occurred during the real-time system implementation. To update the predictive model, the effect of a change in load resistance is considered and the model is named as an adaptive predictive model. The system performance with the adaptive predictive model is validated and a comparative analysis is presented considering an exact and approximated model of the system. The performance is also investigated with the constraint of a switching frequency reduction. The system performance is verified through the simulation as well as experimental results considering the performance indices: THD in load current and average switching frequency.

The novel constraint for the reduction in steady-state error as well as switching frequency is also proposed in this chapter. A simplified FCS-MPC is utilized considering the reduction in computational complexity and the optimization function is designed based on the reference voltage vector. A constraint of change in reference

voltage vector is proposed in this chapter and a comparative analysis with the constraint of a change in switching state is performed for the validation of the steady-state error reduction.

#### **Chapter 5: FPGA resource optimization**

This chapter describes the digital logic resources utilized in the FPGA-based system design including the fundamental FPGA architecture. An analytical approach to reduce the overall FPGA resource requirements is presents in this chapter. Moreover, in-depth analysis of the system implementation with the fixed, approximated and adaptive values of the coefficient used in current prediction is presented. Furthermore, a comparative analysis with different implementation strategies is presented for the selection of the optimum design with respect to the system performance.

#### Chapter 6: Conclusions and future work

The conclusions of the work presented in the dissertation and the possibility of future research work followed by the presented work are mentioned in this chapter.

## FINITE CONTROL SET – MODEL PREDICTIVE CONTROL

#### 2.1 Fundamental Principle

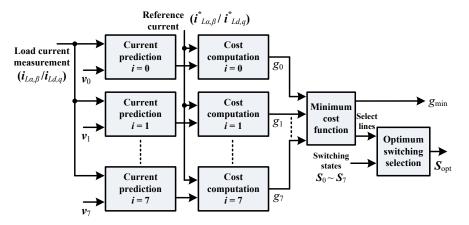

Finite control set-model predictive control (FCS-MPC) is one of the most trendy control schemes of the wide family of model predictive control (MPC). It is characterized by the use of a discrete-time model of the system to predict the future behavior of the variables to be controlled based on the possible switching states of the power converter. The FCS-MPC does not require a cascaded structure of the control loop and does not need a modulator to generate switching signals of the power switches.

The system is considered as a finite set of linear discrete-time models corresponding to the finite switching states. These models are used for the prediction of the future behavior of controlled variables for each switching state to determine the optimum actuation in each sampling interval to achieve the control objectives. The control objectives are governed by a predefined objective function or cost function that is formulated considering controlled variables and desired references. The optimum actuation is selected according to the minimum cost function in each sampling interval and directly applied to the power converter.

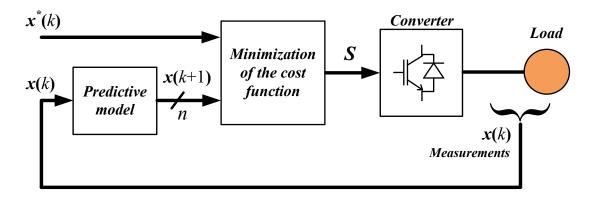

The block diagram of a general FCS-MPC scheme applied to power converters and drives is depicted in Fig. 2.1. The power converter shown in the figure can be of any one of the power converter topologies and any number of phases. The generic load in the figure can be represented by any form of electrical load such as passive load, active load, electrical

Fig. 2. 1. General block diagram of the FCS-MPC scheme for power converters [32].

machine, and the grid. In the FCS-MPC scheme, a sampled form of measured variables x(k) is used in the model to calculate predicted controlled variables x(k+1) for each one of the n possible actuations, that is, switching states, voltages, or currents. After the completion of the prediction step, the values of the corresponding cost functions are evaluated with respect to the error between the predicted x(k+1) and reference values  $x^*(k)$ . Finally, the optimum actuation S is selected corresponding to the minimum cost function and applied to the converter.

#### 2.1.1 System model

In FCS-MPC, the converter is considered as a finite set of linear models, where each model is treated with a specified switching state. In each phase arm (leg) of a power converter, there are two power switches and both switches operates in a complementary fashion, that is, when the upper switch will be turned *on* (state '1'), the lower switch will be turned *off* (state '0') and vice-versa. The number of possible switching combinations or switching states of a power converter is given by

$$N = 2^{m} \tag{2.1}$$

where N is the number of switching states and m is the number of converter legs. If, for instance, a full-bridge converter is used, there are two legs (m = 2) and hence,  $N = 2^2 = 4$ . Similarly, there are 3 legs (m = 3) in a two-level three-phase VSI, and hence,  $N = 2^3 = 8$ .

The model of a system is defined by deriving equations that describe the dynamic behavior of the controlled variables. In power electronics, when choosing voltages, currents, flux linkages as state and output variables, the system is usually modelled by a linear continuous-time state-space representation as

$$\frac{dx(t)}{dt} = A_c x(t) + B_c u(t)$$

(2.2a)

$$y(t) = C_c x(t) + D_c u(t)$$

(2.2b)

where  $A_c$ ,  $B_c$ ,  $C_c$ , and  $D_c$  are the system matrix, input matrix, output matrix, and any system disturbance matrix respectively.

The FCS-MPC algorithm is formulated in the discrete-time domain using a constant sampling interval  $T_S$ . The value of state variables is restricted to change only at discrete sampling instants, that is, at the time instant  $t = kT_S$ , where  $k = 0, 1, 2, \ldots, N_S$  (number of samples) denotes the time steps. The discrete-time state-space representation can be easily computed by integrating (2.2a) from  $t = kT_S$  to  $t = (k+1)T_S$  and maintaining constant u(t) during this time interval and equal to u(k). The resulting discrete-time state-space equation is expressed as

$$x(k+1) = A_d x(k) + B_d u(k)$$

(2.3a)

$$y(k) = \boldsymbol{C}_{d}x(k) + \boldsymbol{D}_{d}u(k)$$

(2.3b)

where discrete-time state-space matrices  $A_d$ ,  $B_d$ ,  $C_d$ , and  $D_d$  can be computed from their continuous-time counterparts and formulated as

$$A_d = e^{A_c T_S} (2.4a)$$

$$\boldsymbol{B}_{d} = \int_{0}^{T_{S}} e^{A_{c}\tau} \boldsymbol{B}_{c} d\tau \tag{2.4b}$$

$$C_d = C_c \tag{2.4c}$$

$$\boldsymbol{D}_d = \boldsymbol{D}_c \tag{2.4d}$$

The discrete-time state-space representation (2.3a) is further used as the predictive model for the calculation of the future values of the controlled sate variables.

#### 2.1.2 Cost function design

The cost function describes an objective function that considers each control variable or system parameter. The additional control parameters or constraints can be incorporated inside a single cost function simultaneously with the primary control parameters such as voltage, current, torque or flux [83]. However, handling of two or more parameters inside a single cost function is not an easy task because of the non-identical nature of parameters like different units and different magnitudes. Any additional control parameter can be managed inside a cost function using a multiplying factor called the weighting factor which is used for the tuning of the additional parameter with the other control parameters. Hence, the general form of a cost function is as follows

$$g = \sum_{n=1}^{l} \lambda_n \left| x_n^* - x_n^p \right| + \sum_{n=l+1}^{m} \lambda_n C_n, \quad n < l < m$$

(2.5)

where  $\lambda_n$  is the weighting factor associated with each term,  $x_n^*$  is the desired reference input,  $x_n^p$  is the predicted value of the controlled state variables, and  $C_n$  is any additional constraints. The first two terms denote a reference tracking by evaluating the respective tracking errors. The examples of reference tracking with respect to the power converter and drive are the objectives to control current, voltage, power, torque and speed.

The tracking error is defined as the distance between the reference and the predicted state variables. It can be formulated using absolute value or the squared value of the error. In this case, the cost function can be expressed as

$$g = |x^* - x^p|$$

(absolute value) (2.6)

$$g = (x^* - x^p)^2$$

(squared value) (2.7)

When the cost function contains only one control objective, the system performance will be similar for the absolute value and squared value error. However, when more than two control variables are incorporated inside a cost function, the squared value error performs better tracking and reduced ripple [32].

The next section describes the current control application of the FCS-MPC in a two-level three-phase VSI system.

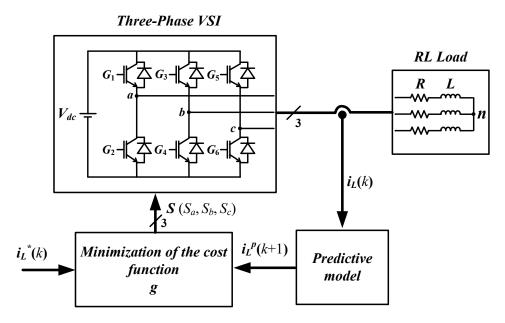

Fig. 2. 2. Schematic diagram for the current control of three-phase VSI using FCS-MPC [83].

#### 2.2 Current Control of Three-Phase VSI

The block diagram of the FCS-MPC applied to a two-level three-phase VSI for the control of the load current is shown in Fig. 2.2. The steps of current control using FCS-MPC is as follows:

- The load side three-phase current  $i_L(k)$  at the  $k^{th}$  sampling interval is measured and provided to the predictive model for the prediction of the future variables.

- The discrete-time model of the inverter system is used to predict the value of the load current in the (k+1)<sup>th</sup> sampling interval for each of the possible switching states of the inverter.

- The value of cost function g is evaluated for all the predicted load currents based on the error between predicted load current  $i_L^p(k+1)$  and desired reference current  $i_L^*(k)$ , obtained from an outer control loop.

- According to the minimum cost function, the optimum switching state is selected and applied to the inverter in the next sampling interval.

The cost function for only one control objective, that is, load current control can be expressed using absolute value error as

$$g = \left| \mathbf{i}_L^* - \mathbf{i}_L^p \right| \tag{2.8}$$

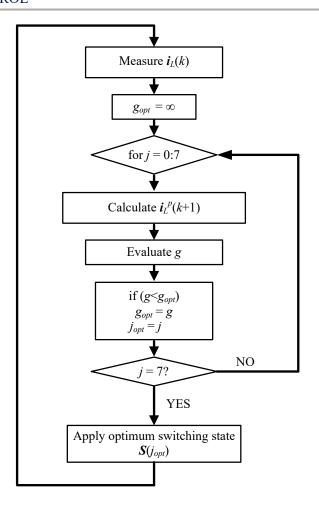

Fig. 2. 3. A flow diagram representing the control algorithm of the FCS-MPC [32].

The control algorithm is also represented as a flow diagram shown in Fig. 2.3. According to the diagram, the outer loop is executed in each sampling interval, and the inner loop is executed for each possible switching state to obtain the optimum switching state to be applied to the power converter during the next sampling period.

#### 2.2.1 Three-phase VSI system model

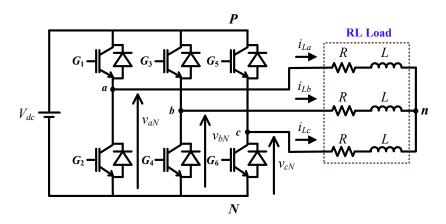

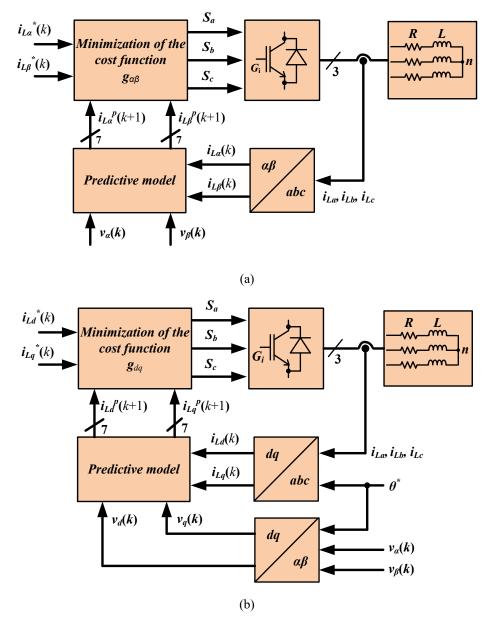

The power circuit of a three-phase VSI system in Fig. 2.4 consists of a three-phase RL load and a dc supply to the VSI, where  $V_{dc}$  is the dc voltage;  $v_{aN}$ ,  $v_{bN}$ , and  $v_{cN}$  are the phase-to-neutral voltages of the inverter;  $i_{La}$ ,  $i_{Lb}$ , and  $i_{Lc}$  are the load currents; R is the load resistance; L is the load inductance. The three-phase VSI consists of three legs (a, b, and c) with two power switches (e.g. IGBT) in each leg:  $G_1$ - $G_2$  (leg 'a'),  $G_3$ - $G_4$  (leg 'b') and  $G_5$ - $G_6$  (leg 'c').  $G_1$ ,  $G_3$ ,  $G_5$  are termed as upper switches and  $G_2$ ,  $G_4$ ,  $G_6$  lower switches.

Fig. 2. 4. Schematic diagram for the current control of three-phase VSI using FCS-MPC.

Table 2. 1. Gating signals of inverter power switches.

| Leg a, $S_a$                | Leg b, $S_b$         | Leg c, $S_c$         |

|-----------------------------|----------------------|----------------------|

| <i>G</i> <sub>1</sub> ON, 1 | G <sub>3</sub> ON, 1 | G <sub>5</sub> ON, 1 |

| $G_2$ OFF, 0                | $G_4$ OFF, 0         | $G_6$ OFF, 0         |

| $G_1$ OFF, 0                | $G_3$ OFF, 0         | $G_5$ OFF, 0         |

| $G_2$ ON, 1                 | $G_4$ ON, 1          | $G_6$ ON, 1          |

#### 2.2.1.1 Inverter model

Switching states of VSI are interpreted corresponding to the switching signals applied to the upper and lower switches that are complementary to each other. The switching states  $S_a$ ,  $S_b$ ,  $S_c$  in Table 2.1 denotes the switching signals applied to the power switches corresponding to three legs. The switching states S can be expressed in vector form as

$$S = \frac{2}{3} \left( S_a + e^{j(2\pi/3)} S_b + e^{j(4\pi/3)} S_c \right)$$

(2.9)

The output voltage space vectors generated by the inverter are defined by

$$\mathbf{v} = \frac{2}{3} \left( v_{aN} + e^{j(2\pi/3)} v_{bN} + e^{j(4\pi/3)} v_{cN} \right)$$

(2.10)

Then, the load voltage vector  $\mathbf{v}$  can be related to the switching state vector  $\mathbf{S}$  by

$$\mathbf{v} = \mathbf{S}V_{dc} \tag{2.11}$$

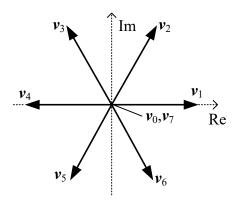

Considering all possible switching combinations of gating signals, eight switching states and hence, eight voltage vectors are obtained as shown in Table 2.2. The two voltage

| Switching states      |       |       |       | Voltage vectors                                | Index  |

|-----------------------|-------|-------|-------|------------------------------------------------|--------|

| S                     | $S_a$ | $S_b$ | $S_c$ | ν                                              | number |

| $S_0$                 | 0     | 0     | 0     | $v_0 = 0$                                      | 0      |

| $S_1$                 | 1     | 0     | 0     | $\mathbf{v}_1 = 2V_{dc}/3$                     | 4      |

| $S_2$                 | 1     | 1     | 0     | $\mathbf{v}_2 = V_{dc}/3 + j\sqrt{3}V_{dc}/3$  | 6      |

| <b>S</b> <sub>3</sub> | 0     | 1     | 0     | $\mathbf{v}_3 = -V_{dc}/3 + j\sqrt{3}V_{dc}/3$ | 2      |

| $S_4$                 | 0     | 1     | 1     | $v_4 = -2V_{dc}/3$                             | 3      |

| $S_5$                 | 0     | 0     | 1     | $v_5 = -V_{dc}/3 - j\sqrt{3}V_{dc}/3$          | 1      |

| $S_6$                 | 1     | 0     | 1     | $v_6 = V_{dc}/3 - j\sqrt{3}V_{dc}/3$           | 5      |

| $S_7$                 | 1     | 1     | 1     | $v_7 = 0$                                      | 7      |

Table 2. 2. Switching states and voltage vectors.

Fig. 2. 5. Voltage vectors generated by the inverter.