# DDS を用いた 10MHz 級デジタル制御 DC-DC コンバータの検討

梶原 健志 \* 安部 征哉 \* 今給黎 明大 \* 松本 聡 \*

† †九州工業大学大学院工学府 〒804-8550 北九州市戸畑区仙水町 1-1 教育研究 5 号棟 1F E7-125

E-mail: † {kajihara.kenji653@mail.kyutech.jp, abe@ele.kyutech.ac.jp, smatsu@ele.kyutech.ac.jp} **あらまし** 電源の小型化に対してスイッチング周波数の高周波化が有効な手段であり、シリコン基板上にパッシブ部品、パワーデバイス、駆動・制御用回路などを搭載した Power SoC(Power Supply on Chip)が注目されている。 Power SoC は大量生産が可能なため、汎用性が実現可能なデジタル制御が有望となる。また、高周波スイッチングを実現するため、高周波のパルスを生成する方法も必要となる。そこで本研究では、パルス生成に Direct Digital Synthesizer(DDS)を用い、デジタル制御の高周波実現に向け検討した結果について報告する。その結果、Duty 比は周波数に依存せず、Duty 比を 0.1%程度に制御するためには 18bit の DAC が必要となる。

キーワード DC-DC コンバータ, デジタル制御, DSP, DDS, Power SoC

## Examination of 10MHz class digital control DC-DC converter using DDS

Kenji KAJIHARA<sup>†</sup> Seiya ABE<sup>‡</sup> and Akihiro IMAKIIRE<sup>‡</sup> and Satoshi MATSUMOTO<sup>‡</sup>

† Faculty of Engineering, Kyushu Institute of Technology 1-1 Sensui-cho, Tobata-ku, Kitakyushu, 804-8550 Japan E-mail: † {kajihara.kenji653@mail.kyutech.jp ,abe@ele.kyutech.ac.jp ,smatsu@ele.kyutech.ac.jp}

**Abstract** Power SoC (Power Supply on Chip), which integrates passive components, power devices, drive / control circuits, etc. on a silicon substrate, is attracting attention as a means to increase the switching frequency to reduce the size of the power supply. The digitally control, which can realize versatility, is promising because power SoC can be mass-produced. To generate high frequency pulses is required in order to realize high frequency switching. In this study, we report the results of studies for the realization of high-frequency digital control using Direct Digital Synthesizer (DDS) for pulse generation. We clarified that the duty ratio does not depend on the frequency, and an 18-bit DAC is required to control the duty ratio to about 0.1%.

Keywords DC-DC Converter, Digital Control, DSP, DDS, Power SoC

## 1. はじめに

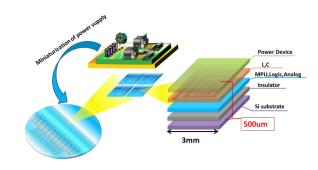

現在、世界ではエネルギー消費が急速に増大しており、電気エネルギーの有効利用が求められてきている[1]。近年ではLSIの低電圧、大電流化に伴い、配線抵抗による損失の増大や効率の低下が問題となってきなった。このような背景のもと、コンデンサやインダクタなどのパッシブ部品、パワーデバイス、それらを駆動・制御のでもをワンチップ上に搭載することにより電源の究極の小型化が可能なPower SoC(Power Supply on Chip)が注目されている[3-5](図 1)。Power SoC は LSI やMEMSの製造技術を用いて生産することが可能であるため、大量生産が可能で1台当たりの製造コストを削減することができる。また、配線距離が短いため、電子機器のさらなる小型化・高性能化が期待できる。

また、Power SoC は大量生産が可能な反面、大量生産に見合った汎用性が必要となる。このため、アナログ制御ではなくデジタル制御が有望視されている。

さらに、Power SoC の実現のためには電源回路中で 大きな体積を占めているパッシブ部品を小型化するこ とが最も有効な手段であり、これに対してスイッチング周波数の高周波化が進められている。

図 1 Power SoC

現在報告されている、Digital Signal Processor(DSP)を用いた制御電源では、スイッチングパルスを DSP を用いて生成しているが、スイッチング周波数がデジタル制御における制御遅れやデジタル PWM の分解能に依存しているため、最終的に DSP のクロック周波数に依存しているという問題点がある。そこで本研究ではスイッチングパルスの生成に DSP のクロック周波数に依存しない Direct Digital Synthesizer(DDS)を用いる方

法がある[6]。

本研究では DDS を用いた 10MHz 級のデジタル制御 DC-DC コンバータの検討を行った結果を報告する。

#### 2. 制御方法

#### 2.1. DAC を用いた Dutv 比の切り替え制御

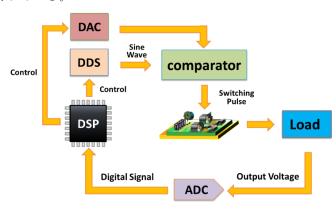

本研究で用いた Duty 比の切り替え制御の原理図を図2に示す。DDS から正弦波を出力し、コンパレーターに入力する。コンパレーターにおける基準電圧はDAC を使用し、DAC からの出力電圧を変更することで矩形波の Duty 比を変更する。この Duty 比の変更によってバックコンバータの出力電圧を制御することが可能である。

また、DAC や DDS への入力信号は DSP を用いて生成している。

図 2 Duty 比の切り替え制御の原理図

#### 3. 実験方法

### 3.1. 実験回路

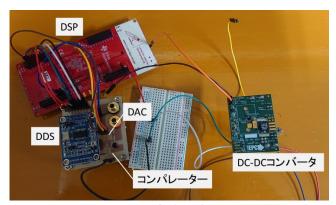

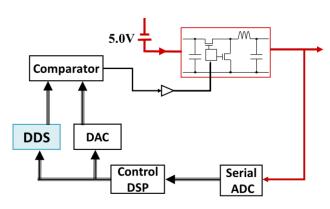

本研究で用いた実験回路を図3に、ブロック図を図4に示す。また、実験回路の仕様を表1に、制御回路の仕様を表2に示す。今回の実験回路のコンバータはGaNパワーデバイスを使用しており、高周波化に向けた回路構成となっている。本実験で用いたDSPにクロック周波数は200Mz、DDSのクロック周波数は180MHz、DACは14ビット、最大50MHzの物を使用した。また、DSPよりも遅いクロック周波数のDDSを使用した。

図3 実験回路

図 4 ブロック図

表1 実験回路の仕様

| 記号      | 説明        | 数值            |  |

|---------|-----------|---------------|--|

| Vin     | 入力電圧      | 5.0V          |  |

| Vout    | 出力電圧      | 1.8V          |  |

| L       | インダクタ     | 10μΗ          |  |

| R       | 内部抵抗      | $0.033\Omega$ |  |

| С       | 平滑コンデンサ   | 1μF           |  |

| Fs      | スイッチング周波数 | 5MHz          |  |

| GaN FET | EPC8004   | Ron:80mΩ      |  |

表 2 制御回路の仕様

| 2 4.4 1.1 - 2.1 - 12.14. |         |                |  |  |  |  |

|--------------------------|---------|----------------|--|--|--|--|

| 部品                       | 部品番号    | 会社             |  |  |  |  |

| DSP                      | F28379D | TEXAS          |  |  |  |  |

|                          |         | INSTRUMENTS    |  |  |  |  |

| DDS                      | AD9851  | ANALOG DEVICES |  |  |  |  |

| AD コンバータ                 | ADS7884 | TEXAS          |  |  |  |  |

|                          |         | INSTRUMENTS    |  |  |  |  |

| DA コンバータ                 | DAC7311 | TEXAS          |  |  |  |  |

|                          |         | INSTRUMENTS    |  |  |  |  |

| コンパレーター                  | LTC6752 | ANALOG DEVICES |  |  |  |  |

また、本実験では DDS、DSP、DAC、コンパレーターを用い、矩形波を出力し、その矩形波をバックコン

バータのスイッチングパルスとして用い、負荷特性、効率特性、負荷急変時の過渡応答の測定を行った。本回路では、DDS および DAC の制御には 1 台の DSP を用いた。

## 4. 実験結果

### 4.1. コンパレーターの出力結果

DDS、DAC、コンパレーターを用いて出力した矩形波を出力した。DACの出力電圧はスイッチング周波数が100kHzの時に測定を行い、今回用いたDACの出力電圧は0.02V おきに変化させることができ、各周波数でDACの出力電圧を0.02V変化させたときのDuty比の変化を測定した。また、その結果を比較することで周波数を変化させたときのDACの分解能の違いについて検討した。

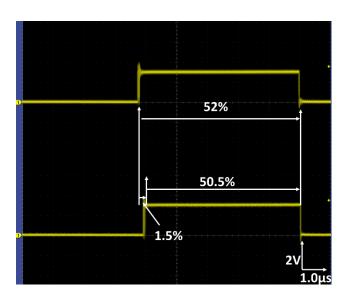

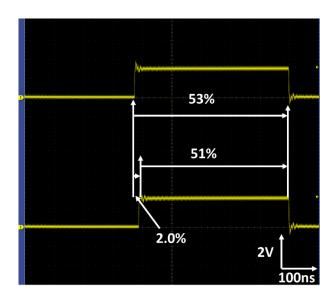

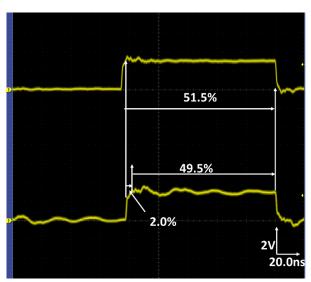

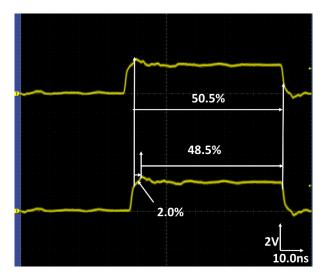

矩形波の周波数が 100kHz、1MHz、5MHz、10MHz の 場合をそれぞれ図 5、図 6、図 7、図 8 に示す。

結果の矩形波の上側の波形が DAC の出力電圧が 0.49V の時で下側の波形が 0.51V の時の波形を示している。

また、実験結果は矩形波の ON 状態を示しており、 Duty 比を示している。

図 5 スイッチング周波数 100kHz の時の矩形波

図 6 スイッチング周波数 1MHz の時の矩形波

図7 スイッチング周波数 5MHz の時の矩形波

図 8 スイッチング周波数 10MHz の時の矩形波

表3に図5から図8までの結果をまとめる。

|            |       | スイッチング周波数 |      |       |       |  |  |

|------------|-------|-----------|------|-------|-------|--|--|

|            |       | 100kHz    | 1MHz | 5MHz  | 10MHz |  |  |

| DAC Ø      | 0.49V | 52%       | 53%  | 51.5% | 50.5% |  |  |

| 出力電圧       | 0.51V | 50.5%     | 51%  | 49.5% | 48.5% |  |  |

| Duty 比の変化量 |       | 1.5%      | 2.0% | 2.0%  | 2.0%  |  |  |

表 3 実験結果の比較

以上の実験結果より、スイッチング周波数が変化しても Duty 比の変化量は変わらない。これらの結果より Duty 比を 0.1%程度に制御するためには 18bitの DAC が必要となる。

しかし、スイッチング周波数が上昇すると矩形波が 歪んでいく。

また、スイッチング周波数が 10MHz の場合には生成された矩形波をバックコンバータに入力しても正常に動作しなかった。

従って、10MHz以上の矩形波を生成する場合にはより高速なコンパレーターが必要になる。DACに関してはスイッチング周波数によらず、Duty比をどの程度の間隔で変化させたいかで決めるとよいことが確認できた。

10MHz 以上のスイッチング周波数では矩形波が大きく歪む問題があるので、DDS、DAC、コンパレーター、バックコンバータを同一基板上に実装しないと測定できないことも確認できた。

#### 4.2. 静特性

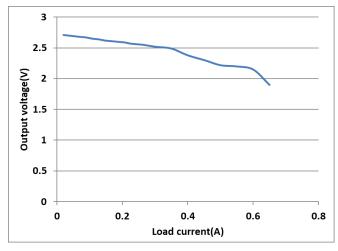

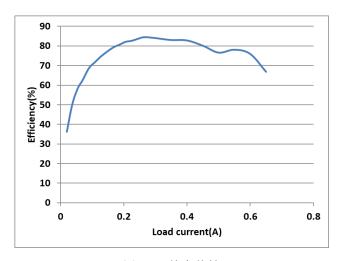

負荷特性および効率特性を図9,図10に示す。

図 9 負荷特性

図 10 効率特性

スイッチング周波数が 5MHz であり、ノイズなど回路の問題で理想的な負荷特性や効率特性にならなかったと考えられる。

## 4.3. 動特性

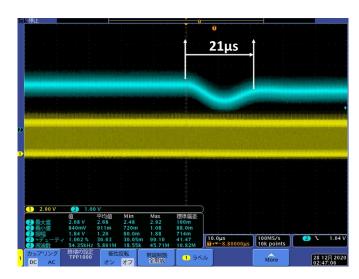

静特性の時と同じ回路を用いて動特性を評価した。 DAC の出力電圧は 0.5V と 0.68V に設定した。 Duty 比はそれぞれ 50%と 32%である。負荷電流の大きさが増加した場合の応答の結果を図 11 に示す。なお、実験条件は 10ut = 0.1A, 0.7A 、1 = 100 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10 、10

図 11 スイッチング周波数 5MHz での 負荷急変時の応答

応答結果は  $21 \mu s$  であった。また、入力電圧 5.0 V に対して、出力電圧は 2.2 V と 1.7 V に収束しており、負荷の大きさに応じてデジタル制御電源が正確に動作していることがわかる。

また、この応答速度についてはコンデンサやインダ

クタの値が一番影響していると考えられる。スイッチング周波数が 5MHz であるため出力電圧の波形のリプルが 20%程あり、改善が必要なことも確認できた。

#### 5. 結論

DAC の分解能の周波数依存性について評価を行い、また、Direct Digital Synthesizer を用いた 10MHz 級のデジタル制御 DC-DC コンバータの静特性および動特性の評価を行った。その結果、

- (1) DAC の分解能には周波数依存性が確認されなかった。

- (2) スイッチング周波数 5MHz での測定を行 うことができ、十分な応答性を得ることが できた。

- (3) しかし、スイッチング周波数 10MHz 以上 の測定を行う場合には改善が必要なこと が確認できた。

以上の結果より 10MHz 級のデジタル制御 DC-DC コンバータを実装するには、バックコンバータも含め DAC、DDS,コンパレーターなどの素子を同一基板上に 実装し、生成した矩形波にノイズがのらないような工夫をする必要があることが確認できた。

## 文 献

[1] 資源エネルギー庁 令和元年度エネルギーに関 する年次報告 (エネルギー白書 2020)

$https://www.enecho.meti.go.jp/about/whitepaper/2020ht \ ml/$

- [2] http://www.tij.co.jp/analog/jp/docs/analogsplash.tsp? contentId=46073

- [3] S.Matsumoto "Future Power Electronics for Realizing Sustaining Society", International Workshop on Power Supply On Chip 2010 (PwrSoc'10), Session 6.6,2010

- [4] K.Bharath, S. Venkatraman, "Power Delivery Design and Analysis of 14nm Multicore Server CPUs with Integrated Voltage Regulators" 2016 IEEE 66th Electronic Components and Technology Conference (ECTC2016), pp.368-373, 2016.

- [5] T. Phillips, "Delivering the Inner Power of SoCs: The Value of Fully Integrated Voltage Regulator", International Workshop on Power Supply On Chip 2018(PwrSoc'18), session 6-2, 2018.

- [6] 友弘真実、安部征哉、松本聡 "Direct Digital Synthesizer のデジタル制御電源への適用の検討" 2020 電子情報通信学会 EE2019-56 pp.43-47