# Academic Year 2020 DISSERTATION

# パワー半導体産業の比較分析と 微細化技術の導入効果に関する研究

Comparative analysis of the power semiconductor industry and a study on the effects of introducing miniaturization technology

馬場 嘉朗

九州工業大学 大学院 生命体工学研究科 生命体工学専攻

福岡県北九州市若松区ひびきの2番4号

#### 概要

本論文では、パワー半導体に注目して半導体産業を詳細に比較分析することでパワー半導体産業が抱える課題を明確化にするとともに、積極的な微細構造の導入で高い競争力を保持できることを示した。さらに微細プロセスの工程能力を考慮した量産設計の新しいモデルを提案しその有効性を示した。

現在までの三十年間で半導体産業全体が大きく変化した。例えばかつて世界的に高い売上を誇った国内半導体メーカのうち現在も上位 10 社に入っているのはキオクシア(旧東芝メモリ)のみとなった。その中にあって比較的市場規模の小さなパワー半導体産業は国内パワー半導体メーカを中心に内製による高性能化と投資コストの圧縮で高い収益性を確保してきたが、海外メーカの成長による影響を受け始めている。

本論文の目的は、半導体産業を比較分析しパワー半導体への微細化構造導入の必要性を 明確にすることと、その際の技術課題である微細化による特性への影響と工程欠陥が歩留 に与える影響をモデル化し定量化することである。さらに実際の半導体工場でのデータを 基にモデルの有効性を示すことである。

第 1 章では、半導体産業全体の市場変化や製品別ビジネスモデルの細分化からパワー半導体産業が置かれている状況を分析した。その結果、パワー半導体設計は微細化に向かっており、微細化ライン確保と自動車用の品質とコストの達成が重要課題であることが分かった。パワー半導体産業分野で企業が継続的成長するためには既存の生産設備(6 インチ、8 インチライン)を前提とした設計技術力だけでなく、300 mmウェハ対応の生産設備による工程能力の飛躍的な改善やランダム欠陥の影響を考慮した量産コスト設計が必要である。本章では特に、パワー半導体産業で既存生産設備と 300mm ウェハ生産設備を比較し生産設備の能力を考慮した量産設計モデルの構築と体系化の重要性を述べた。

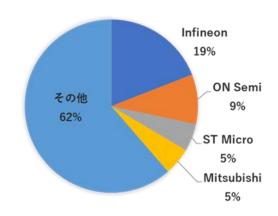

第2章では、パワー半導体産業の特徴を整理するため、世界半導体統計(WSTS)の5分類 (IC4分類+ディスクリート)を独自の視点からビジネスモデル別3分類(旧IDM型:アナログICとディスクリート,専業IDM型:メモリとMPU,ファブレス/ファウンドリ型:システムLSI)に再分類し製品別売上シェアから各半導体メーカの動向を調査した。なお、IDMとは垂直統合型デバイスメーカーを示す。パワー半導体では独Infineon社が最大の市場シェア(19%)を占めており、供給能力確保のため300mmウェハに対応した製造設備を有している。国内メーカは全体でInfineon社に匹敵する規模を持つものの製造設備の整備は遅れていることも明らかになった。特に、300mmウェハに対応した製造設備による工程能力の改善と微細化によるパワー半導体の性能向上が重要であることを述べた。

第3章では、第1章で抽出したパワー半導体産業課題の背景を分析した。メモリやシステム LSI の産業が設備投資型なのに対して、パワー半導体産業は直接労務費の比率が大きく製造の自動化率が低いことが分かった。また製品の品種が多いため直接材料費の比率が大きいことも分かった。また現在パワー半導体の微細化レベルは 200mm 生産ラインの限界設計ルール (130nm) 付近にあり 300mm 生産ラインへの移行が進み始めているが、設備

投資能力が今後の競争力を左右することを示した。

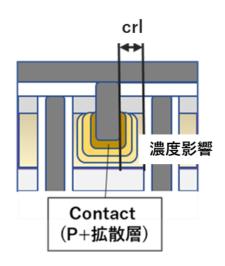

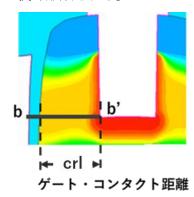

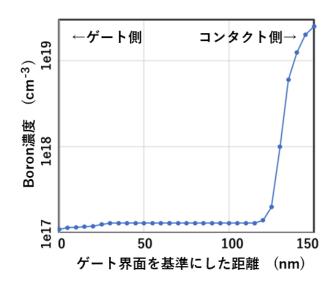

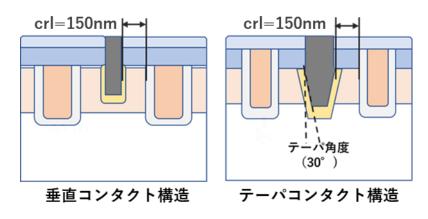

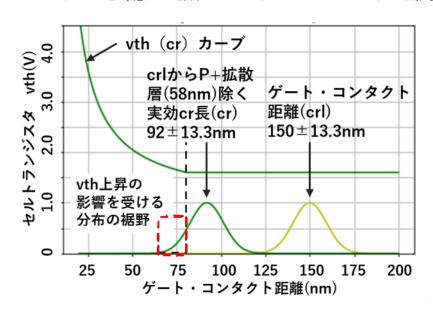

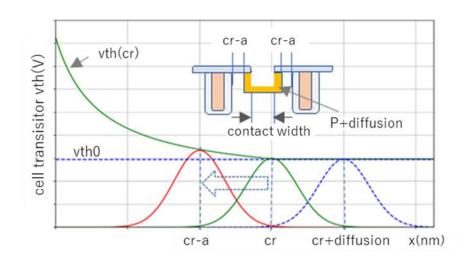

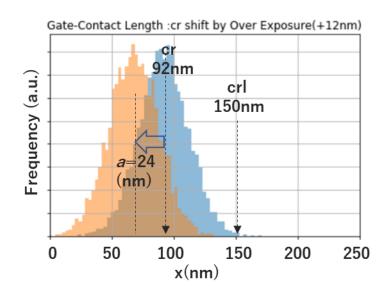

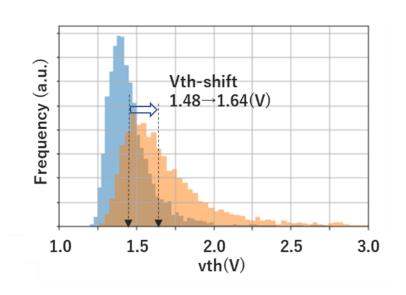

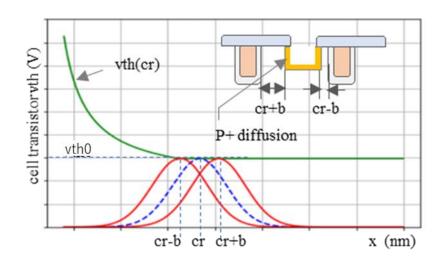

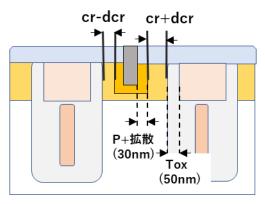

第4章では、微細化が進む中で、加工精度が電気特性に及ぼす影響を検討した。具体的には UMOSFET をモチーフに複数の加工装置によるバラツキの影響を受けるゲート・コンタクト距離 (crl:critical-length) に着目して微細 UMOSFET の Vth 上昇現象を解明した。一般的に考えられているコンタクト P+拡散層によるチャネル濃度上昇は crl<30nm で起こるが、実際には crl<150nm で Vth 上昇が観察されゲート空乏層がコンタクト P+層にパンチスルーすることで Vth 上昇が起こることを明らかにした。微細パワー半導体のセルサイズ縮小に伴ってセルサイズの約 1/10 で縮小が進むゲート・コンタクト距離(crl) は現在 100nm以下になっている。この領域では Vth は crl 依存を始める (crl が小さくなると Vth が急上昇する)。200mm ラインの限界は露光装置のパターニング限界(130nm)ではなく寸法変換差や合わせ精度(10~20nm)が律速している。crl<100nm では Vth 制御が困難になることを示した。

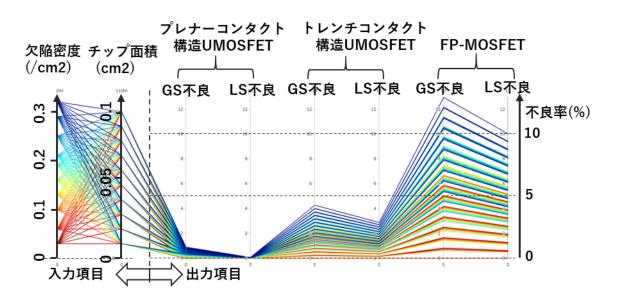

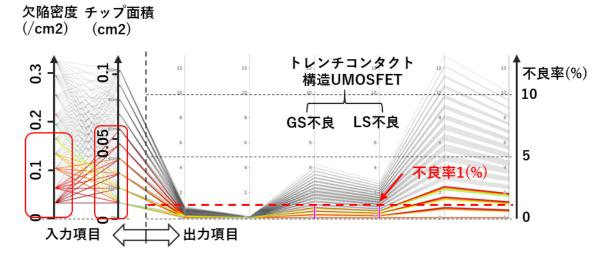

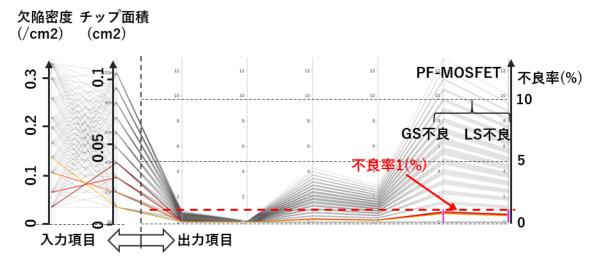

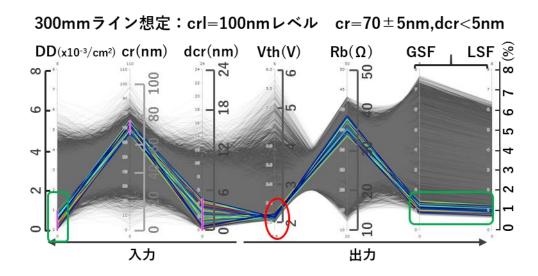

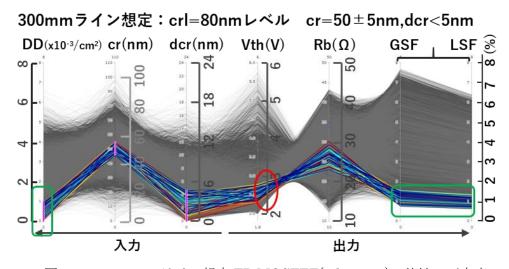

第5章では、まず工程欠陥と製品歩留の関係を解明し、次に第4章との結果を結合したユニバーサルモデルを作成した。具体的には第4章と同じゲート・コンタクト距離(crl)を共通パラメータとしてゲート不良と L 負荷耐量不良のモデルを作成した。ゲート不良については実不良率と良い一致を示した。L 負荷耐量不良については耐量がベース抵抗に逆比例すると仮定してクリティカルエリアモデルを適用した。ランダム欠陥密度(場)とチップサイズ(設計)、ゲート不良と L 負荷不良をデータで結合し動的平行線図で可視化した。これによると crl 縮小に伴い工程欠陥がゲート不良や L 負荷耐量不良の急激な増加を招くこと、現状の加工装置の欠陥管理レベル( $\sim0.01/cm^2$ )でも標準的な  $3mm\Box$ チップの UMOSFET では無視できない歩留低下を起こすことを示した。また、第4章の Vth モデル、ベース抵抗モデルと本章の欠陥モデルを統合したユニバーサルモデルを使って工程能力と欠陥レベルによる特性・不良率影響を 200mm 想定ラインと 300mm 想定ラインで比較した結果、次世代 UMOSFET(crl<80nm)を量産する場合 300mm 想定ラインが必須であることを示した。

第6章では、本研究により得られた結果を総括して本論文の結論と今後の展望と課題をまとめた。

# 目次

| 第 1 章 背景と目的                                 | 1  |

|---------------------------------------------|----|

| 1-1. 半導体産業と市場の変化                            | 1  |

| 1-2. 半導体の分類                                 | 2  |

| 1-3. アナログ IC・ディスクリート半導体産業の課題                | 3  |

| 1-3-1. 旧 IDM 型エコシステム崩壊                      | 4  |

| 1-3-2. 長期供給と高信頼性要求                          | 5  |

| 1-4. パワー半導体の微細化                             | 7  |

| 1-5. UMOSFET 微細化の課題                         | 9  |

| 1-6. 本論文の目的                                 | 11 |

| 第 2 章 半導体メーカの分類                             | 13 |

| 2-1. IDM とファブレス/ファウンドリ                      | 13 |

| 2-2. 半導体メーカの売上                              | 14 |

| 2-3. 半導体専業メーカの売上                            | 16 |

| 2-4. ファブレスメーカの売上                            | 16 |

| 2-5. 半導体部品メーカの売上                            | 18 |

| 2-5-1. アナログ IC                              | 18 |

| 2-5-2. ディスクリート                              | 19 |

| 2-5-2-1. パワー半導体                             | 20 |

| 2-5-2-2. イメージセンサ                            | 21 |

| 2-5-2-3. LED                                | 21 |

| 2-6. まとめ                                    | 22 |

| 第 3 章 アナログ IC・ディスクリート/メモリ・MPU/システム LSI 産業比較 | 23 |

| 3-1. アプリケーション規模とライフサイクル比較                   | 23 |

| 3-2. 半導体コスト構造の比較                            | 24 |

| 3-2-1. DEP 比較                               | 27 |

| 3-2-2. 直材費比較                                | 27 |

| 3-2-3. ロットハンドリングコスト比較                       | 28 |

| 3-3. 半導体製品の信頼性比較                            | 30 |

| 3-4. 販売・生産管理比較                              | 31 |

| 3-5. 生産工場の比較                                | 33 |

| 3-5-1. 口径別 Fab                              | 33 |

| 3-5-2. 口径別ウェハ使用量                            | 34 |

| 3-5-3 国別ウェハ消费县                              | 36 |

| 3-6. ウェハロ径と生産性                           | 38 |

|------------------------------------------|----|

| 3-6-1. ウェハロ径とデザインルール                     | 38 |

| 3-6-2. ウェハロ径とチップ収率                       | 40 |

| 3-7. 半導体製品ロードマップ                         | 41 |

| 3-7-1. MPU とムーアの法則                       | 41 |

| 3-7-2. フラッシュメモリと GB 単価                   | 42 |

| 3-8. まとめ                                 | 43 |

| 第 4 章 微細パワーMOSFET の Vth モデル              | 44 |

| 4-1. 微細化による Vth の上昇現象                    | 44 |

| 4-1-1. Vth の一般モデル                        | 44 |

| 4-1-2. UMOSFET の Vth 一般モデル               | 45 |

| 4-1-3. 微細化による Vth 上昇の一般論                 | 47 |

| 4-1-4. トレンチ側壁からの P+拡散長                   | 48 |

| 4-2. トレンチコンタクト構造 UMOSFET のウェハ面内 Vth バラツキ | 49 |

| 4-3. ゲート・コンタクト距離が短い場合の Vth モデル           | 52 |

| 4-3-1. ゲート空乏層パンチスルーモデル                   | 52 |

| 4-3-2. 製造工程バラツキ                          | 55 |

| 4-3-3. 製造工程バラツキを考慮したチップ Vth の計算          | 56 |

| 4-3-4. 製造パラメータ感度解析                       | 62 |

| 4-3-5. モデル検証                             | 63 |

| 4-4. 微細化による Vth 制御性の課題                   | 65 |

| 4-5. まとめ                                 | 67 |

| 第 5 章 微細化による工程欠陥の影響                      | 68 |

| 5-1. 工程欠陥と不良モード                          | 68 |

| 5-1-1. パワー半導体の不良モード                      | 68 |

| 5-1-2. 欠陥の種類と不良モード                       | 69 |

| 5-2. ゲート不良のモデル化                          | 71 |

| 5-2-1. ゲート不良のクリティカルエリアモデル                | 71 |

| 5-2-2. セル微細化とゲート歩留                       | 75 |

| 5-2-3. 偏在欠陥による歩留のチップ面積依存性                | 78 |

| 5-3. L 負荷破壊と欠陥サイズ                        | 80 |

| 5-3-1. P+インプラ遮蔽欠陥によるベース抵抗上昇モデル           | 80 |

| 5-3-2. 欠陥サイズとセルトランジスタの耐量低下率              | 82 |

| 5-3-3. ゲート不良/L 負荷耐量不良の欠陥密度とチップサイズ依存性     | 83 |

| 5-4. 微細化パラメータによるユニバーサルモデル生成              | 86 |

| 5-5. まとめ                                 | 90 |

| 第 6 章 結論      | 91  |

|---------------|-----|

| 謝辞            | 92  |

| 参考文献          | 93  |

| 図一覧           | 97  |

| 表一覧           | 100 |

| 研究業績論文        | 101 |

| 講演実績          | 102 |

| 委託研究          | 102 |

| Abbreviations | 103 |

| 半導体メーカ略名称一覧   | 105 |

| 付録            |     |

#### 第1章 背景と目的

# 1-1. 半導体産業と市場の変化

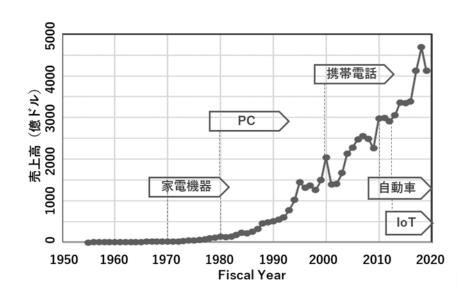

半導体産業は過去六十年間成長を続けている。図 1-1-1.に 1955 年から 2019 年までの世界半導体売上高の推移を示した[1][2](1986 年以降は[1]、以前は[2])。1959 年の売上は 4.6億ドル、2019 年には 4123 億ドルで年平均売上成長率(CAGR:Compound Annual Growth Rate)は 12%と大きな成長を遂げた。最近十年間でも 2009 年 2262 億ドルを基準にすると CAGR は 5.8%で成長を続けている。半導体産業の成長の背景には、過去六十年間にテレビ、エアコン等の家電機器やパーソナルコンピュータや携帯電話等のアプリケーションが途絶えることなく現れ半導体品種増加と購買層増加の相乗効果で成長が続いている。2019 年は米中貿易摩擦、2020 年はコロナ影響で減少傾向にあるが長期的には成長は続くと考えられる。2020 年の統計データは現時点で未公開であり第 2 章の売上分析には 2018 年(売上最大)と第 3 章の生産や投資に関する分析は 2019 年のデータを使用した。

過去六十年間に半導体製品の主役の変化も起こっている。1970年代には、トランジスタ等のディスクリート部品やオペアンプ等アナログICがラジオやテレビに搭載され機器の小型化・省エネを推進した。1980年代には、メモリ・MPU等のLSIがパーソナルコンピュータのキー部品になり半導体産業のけん引役となった。2000年代には、通信機能を取り込んだシステムLSIがメモリ製品と合わせて携帯電話のキー部品となった。2010年代にはパワー半導体やセンサが自動車分野や産業分野でのIoTブームを背景に拡大が始まっている。

図 1-1-1. 世界半導体市場とアプリケーションの変化 ([1][2]を基に作成)

#### 1-2. 半導体の分類

世界半導体市場統計(WSTS:World Semiconductor Trade Statistics)の製品分類(IC4分類+ディスクリート(光半導体とセンサを含む))と各製品群を構成する製品を表 1·2·1.に示した。製品分類ごとに製品提供プレーヤの状況が異なっている。第 2 章で詳細分析を行うが、メモリやマイクロプロセッサはメーカの寡占化が特徴である。メモリは Samsung、SK Hynix、Micron、Kioxia(旧東芝メモリ)の4社が売上の90%を占めている。マイクロプロセッサは Intel 1 社で90%でありプレーヤが限られている。システム LSI は Qualcomm、Broadcom等の通信半導体メーカや AI 分野で拡大する Nvidia 等の存在は大きいがアプリケーションは家電や産業・車載領域まで応用分野が広いためプレーヤ数が多い。アナログ IC、ディスクリート製品は市場登場の歴史が古く製品寿命が長い。また産業や車載向けのカスタム製品に応用されてきたため品種数が非常に多い。そのため製品個々の規模が小さくプレーヤ数はシステム LSI 以上に多い。市場登場はディスクリート・アナログ IC、メモリ、MPU、システム LSI の順番であった。歴史の古いディスクリート・アナログ IC 製品は、機能がシンプルであるため抵抗器やコンデンサと同じく一般的な電子部品として広まり、電子部品カタログに掲載されるほどの定番製品となっている。

表 1-2-1. 半導体分類と代表製品

| メモリ      | MPU | システムLSI   | アナログIC       | ディスクリート |

|----------|-----|-----------|--------------|---------|

| DRAM     | MPU | ASIC/ASSP | オペアンプ        | トランジスタ  |

| SRAM     | MCU | SoC       | コンパレータ       | ダイオード   |

| フラッシュメモリ | DSP | FPGA      | タイマーIC       | サイリスタ   |

| その他      |     | その他       | パワーマネージメントIC | LED     |

|          |     |           | インターフェースIC   | フォトカプラ  |

|          |     |           | 通信IC         | センサ     |

|          |     |           | 車専用IC(IPD)   | その他     |

|          |     |           | その他          |         |

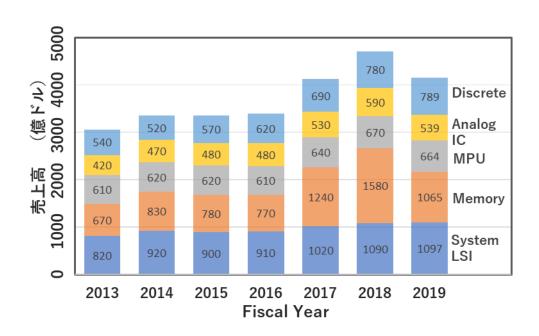

図 1-2-1.に最近 7年の半導体分類別売上の推移を示した[1]。2013 年から 2019 年までの CAGR は+4.4%であった。分類別ではメモリが+7.3%、システム LSI が+3.5%、MPU が+2.5%、アナログ IC が+4.1%、ディスクリート(センサー含む)が+4.5%ですべての分類でプラス成長している。メモリが全体の CAGR を牽引している一方で変動が激しい。アナログ IC とディスクリートは 4%以上で安定的に成長を続けている。パワー半導体やセンサ製品が自動車産業や IoT で応用拡大されていることが成長の背景にはあると思われる。

図 1-2-1. 半導体製品分類別売上高の推移

#### 1-3. アナログ IC・ディスクリート半導体産業の課題

1990 年代は国内の NEC、富士通、東芝、日立等が世界半導体トップメーカであったが 2020 年現在日本国内において世界規模の半導体メーカは Kioxia (旧東芝メモリ) と Sony (CMOS センサ) の 2 社くらいである。システム LSI 分野でも国内には世界規模のファブレスメーカは存在しない[3]。第 3 章で日本は国別ウェハ消費量(面積消費量)では世界 3 位であるが口径 200mm 以下の生産比率 40%と大きいことを示す。これは国内の半導体メーカの大部分は付加価値の小さいアナログ IC とディスクリート製品を製造していることを意味する。アナログ IC・ディスクリートは、前節で示したとおり衰退期にあるのではなく自動車や産業分野で年率 4%以上の成長を続けている。多くの製造ラインを有する国内半導体メーカにとっては再成長のチャンスでもある。しかし歴史あるアナログ IC・ディスクリート産業の成長課題は大きく 2 つある。それは"IDM 型エコシステム崩壊後の微細化対応"と "高品質要求への対応"である。

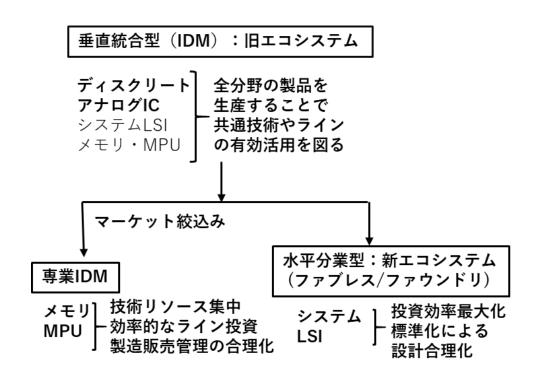

# 1-3-1. IDM 型エコシステム崩壊

1990 年代までは、半導体メーカの主流は垂直統合型(IDM:Integrated Device Manufacturer)で研究開発、設計、量産を一貫して行ってきた。この方式はディスクリートからメモリまでを製造販売する国内の総合半導体メーカには大きなメリットがあった。メモリやシステム LSI 製品の開発や生産で古くなった設備や製造ラインをアナログ IC やディスクリートに活用するというエコシステムが成り立っていた。しかし 2000 年以降システム LSI はファブレス/ファウンドリが新しいビジネスモデルになり、製品規模が大きいメモリや MPU は設備投資に必要な資金や技術リソースを専業化することでオーバーヘッドを減らした専業 IDM に発展した。図 1・3・1.に 2000 年以降に垂直統合 (IDM) から専業 IDM や水平分業型へ変化した様子を示した。新しいビジネスモデルに変わった製品群はメモリ・MPU・システム LSI であり、それぞれが新しいエコシステムに移行した。

図 1-3-1. 垂直統合型 (IDM) ビジネスモデルの変化

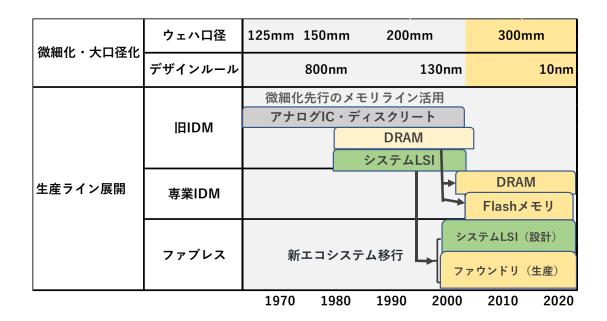

一方で、アナログ IC とディスクリート半導体は社内のメモリやシステム LSI 事業部からの設備調達や技術リソース活用のアドバンテージを失った。特に製品コスト改善のベースとなる大口径化や微細化技術を易く入手することが困難になった。図 1-3-2.に総合半導体メーカの強みであった微細化大口径化投資の有効活用(旧エコシステム)が 2000 年以降(特

にウェハロ径 300mm 化を境界にして) に崩壊していく様子を示した。メモリは専業 IDM、システム LSI はファブレスに転換したがアナログ IC・ディスクリート半導体は取り残された。(200mm ラインでの限界設計ルールは露光装置で律速され 130nm で停滞)

図 1-3-2. ウェハロ径変化と製品群の生産ライン展開

#### 1-3-2. 長期供給と高品質要求

表 1-3-1.に半導体応用製品寿命と主要半導体を示した。個人消費製品スマートフォンの年間出荷台数は 13.7 億台、PC(パーソナルコンピュータ)は 2019 年 WindowsOS 更新時期でもあり年間出荷台数は 2.6 億台であった[4][5]。半導体の大量消費を支えるこれら情報通信機器の寿命は約  $2\sim4$  年、新製品上市サイクルは  $0.5\sim1$  年と短い。情報通信機器市場は、メモリ・MPU・システム LSI 各社のターゲット市場でもある。常に性能改善が行われているため陳腐化するスピードも速く使用される半導体製品の寿命も短い。

| 用途            | 代表製品    | 製品寿命 | 主要半導体                   |

|---------------|---------|------|-------------------------|

| 体也'不信         | スマートフォン | 2    | メモリ・MPU・システムLSI         |

| 情報通信          | PC      | 4    | Y T J · IMIPU · YXTALSI |

| <b>中</b> 面    | T V     | 7    | システムLSI・ディスクリート         |

| 家電            | エアコン    | 10   | VATALSI · T1AV I - F    |

| <b>辛类,丰</b> 卦 | 自動車     | 10   | アナログIC・ディスクリート          |

| 産業・車載         | 電車      | 20   | アテログル・ディスグリート           |

表 1-3-1. 半導体応用製品寿命と主要半導体

TVやエアコン等の家電製品寿命は  $7\sim10$  年と長く液晶バックライト、電源回路やインバート回路にはディスクリート半導体が使用される。液晶 TVなど家電製品の単価が下がっており、お客様の製品が故障した場合に修理するよりも交換保障することが一般的になっている。半導体に対して長期供給と高信頼性が要求されている産業・車載市場については、車や電車の寿命は  $10\sim20$  年であり、部品の故障が人命に関わるため高信頼性が要求されている。特に走行系に使用されるパワー半導体は車両メーカ毎に仕様が異なる(多品種)ことに加え製造ライン(設備や製造プロセス)の変更は基本的に認められない。生産ラインを維持したままで 10 年以上の供給責任を果たさねばならない場合もある。

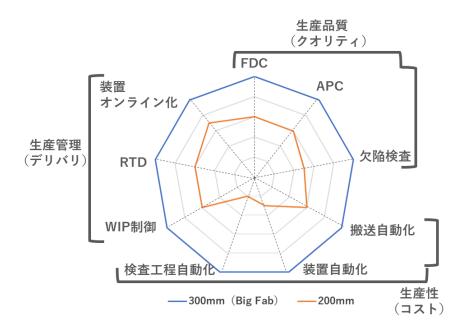

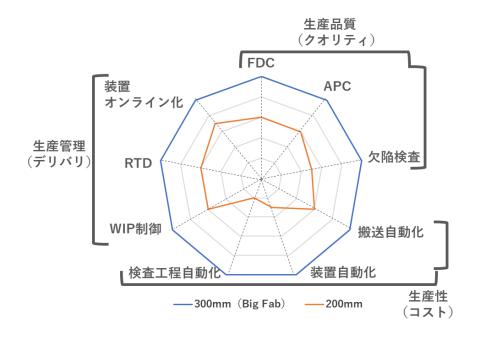

図 1-3-3.は、複数の半導体製造ラインを経験した有識者からのアンケートに基づき作成した 200mm ラインと 300mm ラインを比較したレーダーチャートである。各項目について 300mm ラインをフルマーク (青線) とした場合の 200mm ラインの点数を赤線でプロットした。 (ただし比較の 300mm ラインはメモリラインなどの全自動 Big Fab である。)

図 1-3-3. 200mm/300mm ラインの品質・生産性・生産管理能力比較

自動化による生産性や生産管理は、圧倒的に 300mm ラインが優位である。品質についても 装置ログデータから異常を予測する FDC (Failure Detect Control) や工程バラツキを自動 でフィードバックする APC (Advanced Process Control) 等、300mm の装置オンライン化 による相乗効果が 200mm ラインでは不足している。また、200mm ラインでは工程中の欠 陥検査の自動化が進んでおらず品質を管理するための情報の質や量に乏しい。そのため製品事故が発生した場合に原因系の特定と出荷製品への影響を直ちに分析できないこともあ

る。大規模な 300mm ラインは 200mm ラインに比べ生産管理・生産性・品質の総合的な改 善がなされている。品質管理の観点から高信頼性が要求される産業・車載用途の半導体製品 は 300mm ラインで生産すべきである。しかし長期供給と高品質要求にはジレンマが存在 する。高品質を要求する産業・車載顧客は生産ラインや材料や作業者の変更を基本的に許さ ず 10 年を超えて同一製品供給を要求される。車載メーカが希望する実績のある 200mm ラ インや設備は 20 年近く稼働し老朽化している。 設備保守スタッフも高齢化しており装置レ ベルを人間系で安定に維持することが困難になってきている。 アナログ IC は 300mm 以降 の微細化プロセスもファウンドリから提供準備は完了しておりアナログICメーカは移行を 始めている。 ディスクリート製品 (特にパワー半導体) はトランジスタの独自ルールによる 設計や特殊なプロセスを使うことを他社との差異化技術としているためアナログ IC に比べ てプロセス・デザインの標準化が進んでいない。製造プロセスの標準化が困難なため自前の ラインを維持活用する必要がある。しかしディスクリート製品の中でもパワー半導体のよ うなチップ面積が大きく微細化により更に性能改善が望めるパワーMOSFET や IGBT の 分野では、Infineon が自前で 300mm ライン生産に移行を始めている[6]。 300mm 化で高い 生産性と製造品質が確保されることは間違いない。Infineon の 300mm 製品が車載メーカ に認知されればパワー半導体の 300mm 化は必須になると思われる。その時、国内パワー半 導体メーカは自前で 300mm ラインを整備できるかが課題である。 自前力がない場合、新製 品開発量産はファウンドリ活用が必須となる。

国内パワー半導体メーカは 1990 年以降もデバイス設計・生産で優位性を維持し続け次々と新たな微細構造パワー半導体を世に生み出してきた。しかし微細パワー半導体は 200mm ライン限界の設計ルール(130nm)の端境期に来ている。国内パワー半導体メーカが新しい環境で優位性を維持するためには微細構造設計のみならず微細化による特性影響や欠陥影響を熟知し影響を考慮したデバイス設計を行う必要がある。微細化による特性影響に加え工程能力や欠陥影響が製品歩留に与える影響をモデル化した本論文はその一助になることを期待する。

#### 1-4. パワー半導体の微細化

半導体の微細化を代表する MPU やシステム LSI の集積度ロードマップには、ムーアの 法則が背景にある。法則は半導体の微細化を示す指標で、"チップに搭載されるトランジス タ数は 5 年で 1 桁集積度が向上する" というものである。単純なトランジスタのシュリンクに限定しなければ現在に至る四十年間続いている。微細化による高性能化や速度性能向上に加えてコスト削減の効果がありロードマップを業界全体で共有することで半導体産業成長の原動力となってきた法則である[7]。第3章で MPU とメモリの微細化について詳細分析を行うが、それらの製品とアナログ IC・ディスクリートの微細化レベルは雲泥の差となっている。

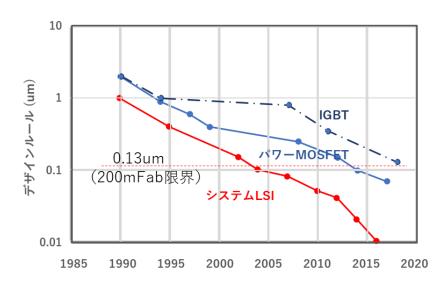

アナログ IC は 200mm ライン限界のデザインルール 0.13um で停滞しているが、ディス クリートはパワー半導体で微細化が継続している。図 1-4-1.に設計/開発レベルのパワー MOSFET と IGBT の微細化レベルの推移を示した。システム LSI に比べ大幅な遅れが生 じていることが判る。微細パワー半導体設計では微細化レベルは 100nm 以下に達しており 200mm ラインで一般的な限界 130nm を超え始めている[8]。300mm 化を視野に入れるべ き時期に来ている。パワー半導体では2010年以降、単純なセル縮小による特性改善ではな く新しいセル構造の提案が行われている。パワーMOSFET は 1990 年にトレンチゲートの UMOSFET から現在の Field Plate 構造 MOSFET (FP-MOSFET)まで進化を続けている。 IGBT も UMOSFET 同様に 1990 年中頃からトレンチゲート構造が採用された。チャネル 抵抗を削減する UMOSFET と異なり IE (Injection Enhancement) 効果により Vce(sat)の 改善が図られる[9]。2012 年にスケーリング IGBT が大村等により提案されセルサイズは一 定で、セル内部のトレンチゲート構造(幅、深さとゲート膜厚)、Si メサ幅、コンタクトサ イズ、ベース深さをスケーリングすることで Vce(sat)の改善が可能なことが示された[10]。 その後、2019年に更屋等により K=1 (メサ幅=3.0um),K=3 (メサ幅=0.6um)の試作結果 が報告された[11]。また 2017 年に Hao Feng 等は Si メサを FIN 構造(side-wall gate 構 造) にした IGBT を提案し FIN 構造の微細化で Vce(sat)が更に改善されることを予想して いる[12]。

Si パワー半導体は微細技術を活用した新しいトランジスタセルの発明により更に進化する可能性がある。

図 1-4-1. パワー半導体の微細化

本論文では、パワー半導体製品で微細化を牽引している UMOSFET をモチーフに微細化 による特性影響や欠陥影響をモデル化し影響の定量化を試みた。得られた知見を次期微細 デバイス設計に役立てることを目的とした。

#### 1-5. UMOSFET 微細化の技術課題

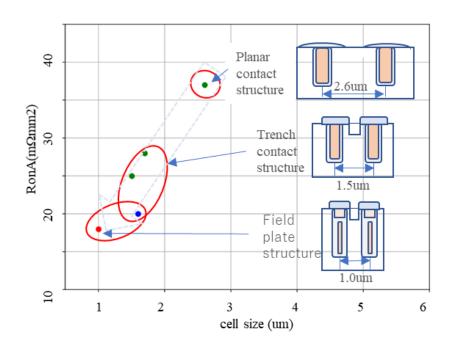

図 1-5-1.に 60V 系 UMOSFET のセルサイズと RonA(面積規格したオン抵抗)のトレンドを示した。1980 年代に主流であった DMOSFET (プレナーゲート構造) はセル間 (Pベース間隔) が短くなると Pベース と N ドレインのビルトインポテンシャルによる空乏層が P ベース間のドレイン領域で広がりオン電流を遮断するピンチオフを起こす構造であるため微細化に限界があった[13]。1990 年に現れたトレンチゲートを使用した UMOSFET は電流経路が上下になりピンチオフによるセル微細化の制約がなくなった[14]。

図 1-5-1. 60V 系 UMOSFET のセルサイズと RonA トレンド

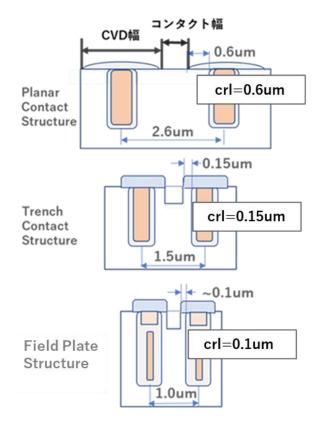

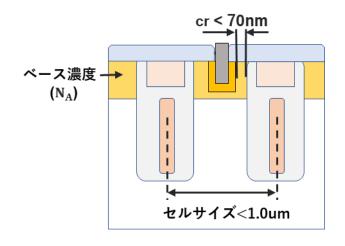

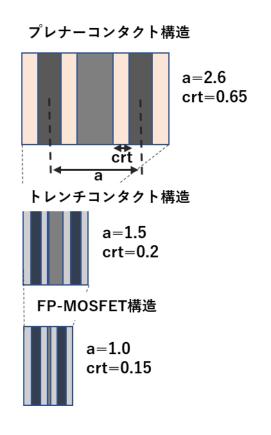

UMOSFET はセルを微細化することでオン抵抗の主要成分であるチャネル抵抗の削減が可能となった。UMOSFET のセルサイズは一般的に 2.6um 程度となった。2000 年代にはメタル埋込技術を応用してプレナーコンタクト構造からトレンチコンタクト構造に変化した[15]。コンタクト領域のシュリンクにより一般的なセルサイズは 1.5um 程度となった。2010 年代には深いトレンチを形成する FP(Field Plate)構造が現れチャネル抵抗のみならずドリフト層抵抗を大幅に削減することが可能となった[16]。トレンチ内にソース FP を形成しゲートはトレンチ構造の上部に組み込まれている。セルサイズは約 1.0um まで微細化

された。また FP-MOSFET は帰還容量が小さく高速動作に向いた構造でもある[17]。

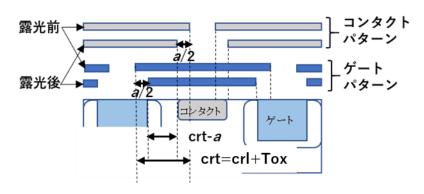

図 1-5-2.にセル構造微細化に伴って、トレンチ幅、コンタクト幅、CVD 幅(ゲート上の 絶縁膜幅) の縮小を図示した。トレンチ内のポリシリコンは CVD 膜を介してソースメタル と絶縁されている。パターン上でトレンチゲート側面からコンタクトエッジまでの距離は ソース電極とゲート電極の絶縁距離でありポリシリコンダストのようなランダム欠陥の影 響を受けやすいクリティカルな距離 (crl:critical length) である。 セル微細化によりこの距 離も小さくなっており初期のプレナーコンタクト構造では 0.6um、トレンチコンタクト構 造では 0.15um、最新の FieldPlate 構造では 0.1um となっている。 セルサイズの約 1/10 で 縮小している。0.1um は 200mm 露光装置の限界寸法 0.13um を超えたレベルである。更 に UMOSFET の製造工程ではトレンチゲートのパターンを基準にコンタクトパターンが 形成されるため上記ゲート・コンタクト距離は、露光装置のバラツキやパターンの合わせず れ、トレンチ形成のドライ加工装置のバラツキ等複数工程の影響を受ける。crl が短くなる ことで製造工程でのランダム欠陥に敏感になることや Vth 等特性の制御が困難になること が予測される。本論文では既存デバイスの特性バラツキや歩留情報を使って解析モデルを 検証し定量的な影響を予測することでパワー半導体の微細化に関する製造設計手法を提案 する。第4章では crl が短くなることによる Vth 上昇現象と Vth 制御性の低下のモデル化 を行った。第5章では工程のランダム欠陥によるゲート不良とL負荷耐量不良をモデル化 した。

図 1-5-2. セル構造微細化とゲート・コンタクト距離(crl)の推移

#### 1-6 本論文の目的

現在パワー半導体の微細レベルは 200mm ラインの限界設計ルール (130nm) 付近にあり更なる微細化 (300mm 化) へのターニングポイントにきている。しかし国内では 300mm 投資しているメモリやシステム LSI メーカは親会社から分社独立したためパワー半導体メーカが従来のように易く 300mm ラインや微細化技術を享受することができない状況になっている。国内パワー半導体メーカが継続成長するためには既存ラインを前提とした T-CAD による設計技術力だけでなく、生産ライン変更 (場) と微細化 (設計) による工程能力の変化やランダム欠陥の影響を把握したコスト設計力が必要である。楢崎等はトレンチコンタクト構造を採用した UMOSFET でゲート・コンタクト距離(crl)が短くなることで L負荷耐量上昇とゲート不良増加を実験データで示した[76]。しかし、製造ラインの工程能力やランダム欠陥を加味したパワー半導体設計は各メーカのノウハウ事項であることや性能重視の学会発表で取り上げられにくい内容であるため情報は少なくモデル化や体系的に取り組まれた報告例は稀有である。本論文の目的は、半導体産業を比較分析しパワー半導体産業の将来課題を明確にするとともに微細化パワー半導体の技術課題として微細化による特性そのものへの影響に加え工程能力や工程欠陥が特性や歩留に与える影響をモデル化し定量化することで将来の微細パワー半導体の量産設計を体系化することである。

第1章では、半導体産業全体の市場変化や製品別ビジネスモデルの細分化からパワー半導体産業が置かれている状況を分析した。結果、微細パワー半導体はデザインルールの端境期にあり微細化ライン確保と車載品質の確保が大きな課題であることを示した。国内メーカが微細パワー半導体分野で成長するためには優位性をもつデバイス設計に加え製造ラインの工程能力やランダム欠陥を考慮したコスト設計と信頼性設計が重要であることが判った。本研究ではUMOSFETをモチーフにセルトランジスタの微細化に伴って起こる特性影響と工程欠陥による歩留や信頼性影響を実験的かつ理論的に明らかにし将来の微細パワー半導体に必要な製造ラインのスペックを明確化することの重要性について述べた。

第2章では、国内のパワー半導体産業の状況を把握するため、世界半導体統計(WSTS)の5分類(IC4分類+ディスクリート)をビジネスモデル別3分類(旧IDM型:アナログICとディスクリート,専業IDM型:メモリとMPU,ファブレス/ファウンドリ型:システムLSI)に再分類し製品別売上シェアから各半導体メーカの動向を調査した。パワー半導体はInfineonがトップシェア(19%)であり300mmラインで既に生産開始している。国内メーカは併せるとInfineonに匹敵する規模を持つが微細化は遅れている。最大のビジネス課題は将来の微細化ライン(300mmライン)の確保であることを示した。

第3章では、第1章で抽出したパワー半導体産業課題の根拠をメモリやシステム LSI 産業と比較することで示した。現在パワー半導体の微細レベルは 200mm 生産ラインの限界設計ルール (130nm) 付近にあり 300mm 生産ラインへの移行が必要な端境期である。しかし日本は他国と比べ 200mm 以下の生産ライン比率が多く微細化後進国となっている。国

内では微細技術や製造技術に対する知見が全体的に乏しくなっている。端境期を迎えた今、連続性が無くなる製造ラインの変化 (200→300mm) に対して工程能力や欠陥レベルを考慮しコストを意識したデバイス設計が重要であることを示した。

第 4 章では、微細化が進む中で加工精度が電気特性に及ぼす影響を検討した。具体的には UMOSFET をモチーフに複数の加工装置によるバラツキの影響を受けるゲート・コンタクト距離 (crl) に着目して微細 UMOSFET の Vth 上昇現象を解明した。一般的に考えられているコンタクト P+拡散層によるチャネル濃度上昇は crl<30nm で起こるが、実際には crl<150nm で Vth 上昇が観察されゲート空乏層がコンタクト P+層にパンチスルーすることで Vth 上昇が起こることを明らかにした。微細パワー半導体のセルサイズ縮小に伴ってセルサイズの約 1/10 で縮小が進むゲート・コンタクト距離 (crl) は現在 100nm 以下になっている。この領域では Vth は crl 依存を始める (crl が小さくなると Vth が急上昇する)。 200mm ラインの限界は露光装置のパターニング限界(130nm)ではなく寸法変換差や合わせ精度(10~20nm)が律速している。crl<100nm では Vth 制御が困難になることを示した。

第5章では、まず工程欠陥と製品歩留の関係を解明し、次に第4章との結果を結合したユニバーサルモデルを作成した。具体的には第4章と同じゲート・コンタクト距離(crl)を共通パラメータとしてゲート不良と L 負荷耐量不良のモデルを作成した。ゲート不良については実不良率と良い一致を示した。L 負荷耐量不良については耐量がベース抵抗に逆比例すると仮定してクリティカルエリアモデルを適用した。ランダム欠陥密度(場)とチップサイズ(設計)、ゲート不良と L 負荷不良をデータで結合し動的平行線図で可視化した。これによると crl 縮小に伴い工程欠陥がゲート不良や L 負荷耐量不良の急激な増加を招くこと、現状の加工装置の欠陥管理レベル( $\sim0.01/cm^2$ )でも標準的な  $3mm\Box$ チップの UMOSFET では無視できない歩留低下を起こすことを示した。また、第4章の Vth モデル、ベース抵抗モデルと本章の欠陥モデルを統合したユニバーサルモデルを使って工程能力と欠陥レベルによる特性・不良率影響を 200mm 想定ラインと 300mm 想定ラインで比較した結果、次世代 UMOSFET(crl<80nm)を量産する場合 300mm 想定ラインが必須であることを示した。

第6章では、本研究により得られた結果を総括する。微細パワーデバイスのセルサイズ縮小に伴ってセルサイズの約1/10で縮小が進むゲート・コンタクト距離(crl)は現在100nm以下になっている。この領域ではVthはcrl依存を始める。200mm露光装置のパターニング限界(130nm)より寸法変換差や合わせ精度の限界(10~20nm)が深刻な影響を与えVth制御が困難になることを示した(第4章)。また、現状の加工装置の欠陥管理レベル(~0.01/cm²)でも標準的な3mm□チップのUMOSFETでは無視できない歩留低下を起こすことを示した。量産を意識した場合、加工装置の欠陥レベルを1桁以上管理改善する必要があることを示した(第5章)。微細化パラメータによるユニバーサルモデルから"現状の200mmラインはcrl<100nmの微細パワー半導体の量産には適しているのか否か""300mmラインでは生産可能か否か"という結論を導き出した。

# 第2章 半導体メーカの分類

# 2-1. IDM とファブレス/ファウンドリ

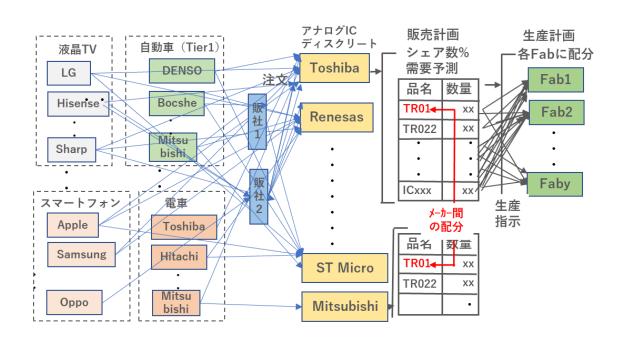

本章では国内のパワー半導体産業の状況を把握するため、世界半導体統計(WSTS)の 5 分類(IC4 分類+ディスクリート)をビジネスモデル別 3 分類(旧 IDM 型:アナログ IC とディスクリート,専業 IDM 型:メモリと MPU,ファブレス/ファウンドリ型:システム LSI)に再分類し製品別売上シェアから各半導体メーカの動向を調査した。第 1 章で 2000 年以降それまでの半導体メーカのビジネスモデルであった IDM(Integrated Device Manufacturer)型のエコシステムが崩壊したことを述べた。システム LSI メーカはファブレス化しファウンドリを活用して製品を供給する水平分業の新エコシステムを構築した [18]。また製品規模が大きいメモリや MPU は設備投資に必要な資金や技術リソースを専業化することで集中する専業 IDM に発展した。図 2-1-1.に新旧 2 つの IDM とファブレス/ファウンドリの半導体メーカのビジネスプロセスを示した([18]に組立/テスト/営業フローを追加)。

| ビジネスモデル             | 垂直統合                                     | 型ビジネス           | 水平分業型ビジネス                                                                                                                            |

|---------------------|------------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------|

| 半導体産業<br>での分類       | IDM<br>(Integrated Device                | e Manufacturer) | Fabless/Faundry                                                                                                                      |

| 半導体<br>ビジネス<br>プロセス | 要素技術・IP開発  チップ設計  チップ生産  組立・テスト 自社 OSAT* |                 | IP開発 IP開発会社 (Arm社等)  チップ設計 Fabless (Qualcomm等)  チップ生産 Faundry (TSMC等)  組立・テスト OSAT* *OutSourced Assembly and Test (ASE等)  営業 (自社/販社) |

| 製品分類<br>(本論文)       | ディスクリート メモリ<br>アナログIC MPU                |                 | システムLSI                                                                                                                              |

| ビジネス分類<br>(本論文)     | 半導体部品半導体専業                               |                 | ファブレス/ファウンドリ                                                                                                                         |

| 分類上の<br>特徴          | 少量多品種生産 多量少品種生産<br>長寿命高品質要求              |                 | 設計ルールと標準化により<br>数量・品種に柔軟に対応                                                                                                          |

図 2-1-1. IDM とファブレス/ファウンドリ

従来の IDM は、要素技術・IP 開発からチップ設計、チップ生産、パッケージ組み立て、テスト、販売までのプロセスを一貫して行っていた。半導体製品の品種と規模が増えてくると問題になるのが、研究開発費と設備投資費であった。Intel は DRAM 事業から撤退し MPU (Micro Processor Unit) のみに注力し全世界の工場で製造プロセスを統一することで投資した設備稼働率を高めた。またムーアの法則に従った業界ロードマップを PC メーカと共有し計画的投資と計画的生産が行える専業 IDM という安定したビジネスモデルを作った。R&D を解散し社外リソースを積極的に活用することで研究開発費の圧縮を図った[19]。

また、ファブレスを代表する Qualcomm は得意の通信技術にアームコアを取り込んだシステム LSI を設計し、世界最大のファウンドリである TSMC のクリーンルームでチップ製造を行っている[20]。 TSMC は Broadcom や Nvidia 等他の巨大ファブレスメーカの製造を請け負うことで各半導体分野の製品市場動向をいち早く入手し自社の生産規模を把握することができる。これにより無駄のない設備投資や設備稼働率を高く維持できるメリットがある。

アナログ IC・ディスクリート半導体メーカは第 1 章でも取り上げた様に扱う製品が多く寿命が長いため他ビジネスのように特定製品特化やファウンドリ委託が困難である。2000年以降旧 IDM のエコシステムが崩壊した後、新たな生産技術や生産ラインの更新スピードが落ちている。また新製品開発や設備投資が回らない状況にある。詳細分析は第 3 章でメモリ・MPU、システム LSI とビジネス構造の比較を行う。本章ではまず各メーカの売上高を分析しビジネスモデルごとの特徴を抽出する。

# 2-2. 半導体メーカの売上

表 2-2-1.に 2019 年(CY)の半導体メーカの売上ランキングを示した[21]。 売上金額(単位:億ドル)と表 2-1-1.で 3 分類したビジネスタイプを併記し色分けした。上位 15 社の売上合計は、3148 億ドルで、半導体全売上(4121 億ドル)の 76%を占める。半導体専業メーカを橙色に着色した。Intel(1位)は MPU 専業メーカであり、Samsung(2位)SK Hynix(4位)、Micron(5位)、Kioxia(9位)はメモリメーカである。

ファブレス/ファウンドリを緑色に着色した。ファウンドリは TSMC (3 位) で、Broadcom (6 位)、Qualcomm(7 位)、 Nvidia (10 位)、 Media Tek(15 位)はシステム LSI メーカで ある。半導体部品メーカを水色に着色した、TI(8 位)、Infineon (12 位)、STMicro (13 位)、 NXP(14 位)はアナログ IC とディスクリート製品の老舗半導体メーカである。国内メーカの多くはこのビジネス分野に属するが CMOS センサの Sony(11 位) を除いてランキング に含まれていない。また日本半導体メーカの 2019 年度売上シェアは僅か 6%となっている。

表 2-2-1. 2019 年半導体売上(CY)ランキング (ファウンドリ含)

| ランキング |           | 売上(億ドル) | タイプ    |

|-------|-----------|---------|--------|

| 1     | Intel     | 698     | 半導体専業  |

| 2     | Samsung   | 556     | 半導体専業  |

| 3     | TSMC      | 345     | ファウンドリ |

| 4     | SK Hynix  | 229     | 半導体専業  |

| 5     | Micron    | 200     | 半導体専業  |

| 6     | Broadcom  | 177     | ファブレス  |

| 7     | Qualcomm  | 143     | ファブレス  |

| 8     | TI        | 135     | 半導体部品  |

| 9     | Xioxia    | 113     | 半導体専業  |

| 10    | Nvidia    | 105     | ファブレス  |

| 11    | Sony      | 96      | 半導体部品  |

| 12    | Infineon  | 95      | 半導体部品  |

| 13    | ST Micro  | 89      | 半導体部品  |

| 14    | NXP       | 89      | 部品     |

| 15    | Media Tek | 79      | ファブレス  |

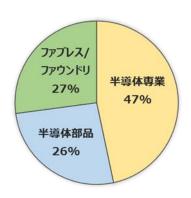

図 2-2-1.に専業メーカ、ファブレス/ファウンドリメーカ、電子部品(アナログ IC・ディスクリート)メーカの売上比率を示す。

図 2-2-1. メーカ分類別売上比率 (上位 15 社:3148 憶ドル)

表 2-2-1.の上位 15 社には各ビジネスタイプ毎 5 社がランクインしている。売上比率は半導体専業が全体の 5 割、ファブレス/ファウンドリと半導体部品が 2.5 割という構成になっている。半導体専業メーカは一社当たりの売上高は他業態の 2 倍であることが判る。また、国内メーカでランクインしているのは Kioxia(旧東芝メモリ)と Sony の 2 社だけである。国内メーカの状況を把握する目的で次節以降で詳細にタイプ別売上分析を行った。

#### 2-3. 半導体専業メーカの売上

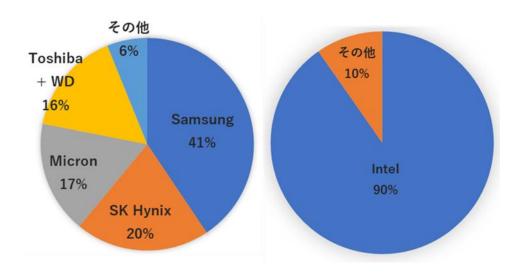

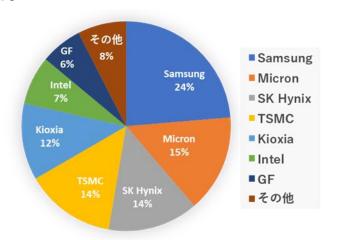

半導体売上ランキングに含まれていた半導体専業メーカ 5 社の専業分野での市場シェアを、図 2-3-1.に示した。メモリ製品は、DRAM と NAND フラッシュメモリ売上を合わせた 2018 年度 (貿易摩擦やコロナ影響がない過去最高)売上を採用した。メモリの総売上は 1633 億ドルであった。1位2位は、韓国の Samsung と SK Hynix であり、両者で 61%を占めている。3位が米の Micron で 17%、4位が東芝メモリ(現 Kioxia)と WD(旧 SanDisk: チップ製造は日本)が 16%となっており、4 社でメモリ全体の 94%を占めている[22]。

MPU 市場(2019年度) の総売上は 773 億ドルで Intel が 698 億ドルで圧倒的シェア (90%) を占めている[23]。一般的にシェア 40%を確保するとセットメーカに対し価格設定が優位になる。Samsung や Intel は PC やスマートフォンメーカーに対し優位な立場にあるといえる。PC やスマートフォン業界の開発や販売のロードマップを共有することで精度の高い開発計画と無駄の少ない投資計画を作成できることも半導体専業メーカのメリットである。

図 2-3-1. 半導体専業メーカの市場シェア (左図:メモリ、右図:MPU)

#### 2-4. ファブレスメーカの売上

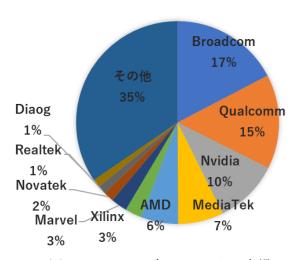

表 2-4-1.に、ファウンドリを除くシステム LSI (ファブレス) メーカの売上ランキング (2018 年) を示した[24]。総売上は 1090 億ドルで上位 10 社が占める割合は 65%である。 この数字はメモリや MPU の専業メーカ比率(90%以上)には及ばない。原因は、プレーヤ数 が多いことにある。ファブレス/ファウンドリは新エコシステムであり今後はシステム LSI のみならずアナログ IC メーカも参入しプレーヤ数は増えると予想される。

表 2-4-1. 2018 年システム LSI (ファブレス) ランキング

| ランキング |          | 売上(億ドル) | 本社 |

|-------|----------|---------|----|

| 1     | Broadcom | 189     | 米  |

| 2     | Qualcomm | 164     | 米  |

| 3     | Nvidia   | 112     | 米  |

| 4     | MediaTek | 79      | 台湾 |

| 5     | AMD      | 65      | 米  |

| 6     | Xilinx   | 29      | 米  |

| 7     | Marvel   | 28      | 米  |

| 8     | Novatek  | 18      | 台湾 |

| 9     | Realtek  | 15      | 米  |

| 10    | Dialog   | 14      | 米  |

通信 LSI の Broadcom(1 位)、Qualcomm(2 位)、GPU や AI チップの Nvidia(3 位)の売上が大きい。MediaTek(4 位)と Novatek(8 位)は台湾のメーカであるがその他はすべて米メーカである。米・台湾メーカがファブレス/ファウンドリビジネスで成功を収めていると言える。図 2-4-1.にファブレス各社の売上比率を示す。

図 2-4-1. ファブレスメーカの市場シェア

残念ながら国内の半導体メーカはランキングに入っていない。2000 年以降旧 IDM システムが崩壊した後、日本のシステム LSI ビジネスはファブレス/ファウンドリという新しいエコシステムへの乗り換えが遅れたのが原因である[25]。

#### 2-5. 半導体部品メーカの売上

アナログI C・ディスクリートメーカは、オペアンプやトランジスタなど製品寿命が長く、抵抗やコンデンサのような電子回路を構成する部品と同じように、品種が多く単価が安いため製品としての付加価値が少なく生産数量は多いものの売上高は小さい場合が一般的である。また、古い歴史があるため製品分野が広く分野ごとに多くのプレーヤが存在する。本章では、アナログ IC とディスクリートで売上規模の大きいパワー半導体、イメージセンサ、LED のプレーヤに着目して分析した。

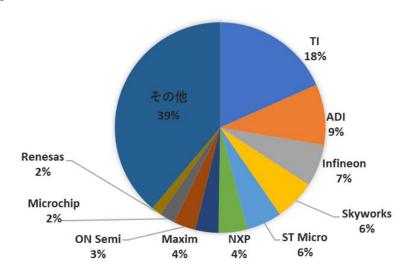

# 2-5-1. アナログ IC

表 2-5-1.に 2018 年度のアナログ I Cメーカランキングを示した[26]。上位 10 社中 6 社は米メーカで他 4 社も日欧メーカが占めている。上位 10 社の売上合計は 361 億ドルでアナログ IC 市場全体(590 億ドル) の 61%である。製品寿命が長く品種が多いビジネスであるため専業半導体メーカに比べプレーヤ数が多いがシステム LSI (ファブレス) の 65%と同レベルにある。2015 年以降、上位のアナログ IC メーカは他社を買収することにより売上シェアを上げている。2 位の ADI(Analog Devices)は 2016 年に Linear Tech (Linear Technology)を買収し 2020 年に7位の Maxim を買収した。3 位の Infineon は 2015 年にパワーデバイスの老舗である IR(International Rectifier) を買収した。このようにアナログ IC 大手メーカの近年売上拡大は新たなヒット商品販売によるものではなく買収によるマーケット獲得によるものである。

| ランキング |           | 売上(億ドル) | 本社所在地 |

|-------|-----------|---------|-------|

| 1     | TI        | 108     | 米     |

| 2     | ADI       | 55      | 米     |

| 3     | Infineon  | 38      | 独     |

| 4     | Skyworks  | 37      | 米     |

| 5     | ST Micro  | 32      | スイス   |

| 6     | NXP       | 26      | オランダ  |

| 7     | Maxim     | 21      | 米     |

| 8     | ON Semi   | 20      | 米     |

| 9     | Microchip | 14      | 米     |

| 10    | Renesas   | 9       | 日本    |

表 2-5-1. 2018 年アナログ IC 売上メーカランキング

図 2-5-1.にアナログ IC の市場シェアを示した。また、10 位までのメーカは米国、欧州、

日本であり韓国や台湾メーカの参入は見られない。米メーカ 6 社で全体シェアの 40%を占めている。

図 2-5-1. 2018 年 アナログ IC の市場シェア

今後、パワーIC や通信 IC 等の付加価値の高い新製品の開発や生産はアナログファウンドリや 300mm アナログ混載プロセスを提供する TSMC 等の巨大ファウンドリを活用したファブレスに移行すると思われる。

#### 2-5-2. ディスクリート

ディスクリート製品は、アナログ IC より更に品種数が多い。ディスクリート製品を構成する製品群には、パワー半導体、センサ・アクチュエータ、イメージセンサ、LED、光半導体、小信号半導体等がある。表 2-5-2.に、2018 年度ディスクリート製品群の売上を示した[27]。ディスクリート全体の売上は778 億ドルでアナログ IC の約 1.3 倍であるが、全く性質の異なる製品群ごとにプレーヤが存在し品種の多さはアナログ IC の比ではない。

| 製品群         | 売上(億ドル) |

|-------------|---------|

| パワー半導体      | 194     |

| センサ・アクチュエータ | 187     |

| イメージセンサ     | 157     |

| LED         | 147     |

| 小信号デバイス     | 26      |

| その他         | 67      |

表 2-5-2. 2018 年ディスクリート製品別売上

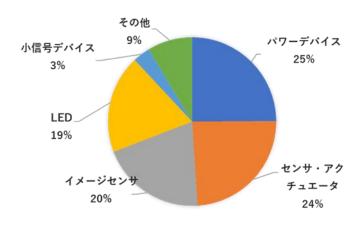

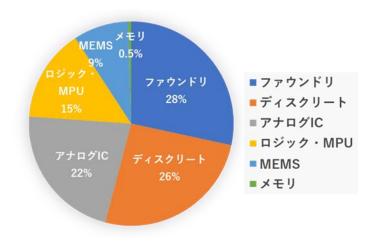

図 2-5-2.に製品群ごとの売上比率を示した。ディスクリート製品群で売上比率が大きい製品群は、パワー半導体 (25%)、センサ・アクチュエータ (24%)、イメージセンサ (20%)、LED (19%)の 4 製品群で約 90%を占める。

図 2-5-2. 2018 年ディスクリート製品別売上比率

# 2-5-2-1. パワー半導体

近年の産業車載応用、IoT 応用で売上の伸びを牽引しているパワー半導体市場シェアを図 2-5-3.に示した[28]。パワー半導体は、2015年に IR(International Rectifier)を買収した Infineon のシェアが 19%で突出している。ON Semi が 9%、STMicro が 5%、日本メーカは Mitsubishi が 5%、Toshiba は 4%である。国内には Mitsubishi、Toshiba の他に Rohm、Renesas、Fuji など親会社グループの重電部門にパワー半導体を供給しているメーカが存在する。これらのメーカは日本のインフラを支える産業構造の一環を担っている。国内メーカを合算すると Infineon に匹敵するがパワー半導体の分野では Infineon の存在が大きくパワー半導体専用の 300mm 量産ラインを二拠点に保有する唯一のメーカとなっている。

図 2-5-3. 2018 年パワー半導体市場シェア

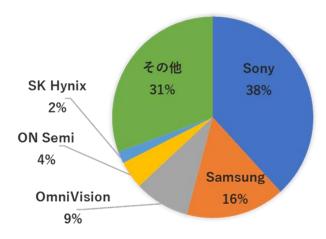

# 2-5-2-2. イメージセンサ

IoT 応用でセンサやイメージセンサの需要が高まっている。イメージセンサの市場シェアを図 2-5-4.に示した[29]。

図 2-5-4. 2018 年イメージセンサ市場シェア

CMOS イメージセンサ分野は Sony が 38%と世界最大のシェアを有している。国内 300mm ラインで生産を行っている。一方 4 位でシェア 4%の ON Semi は車載カメラ分野 に特化している。今後の動向が注目される。

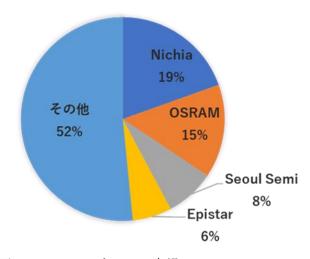

#### 2-5-2-3. LED

液晶テレビや照明分野で伸張してきた LED の市場シェアを図 2-5-5.に示した[30]。

図 2-5-5. 2018 年 LED 市場シェア

白色 LED が登場して以来 LED 製品分野の主要プレーヤであった Nichia (日本)、OSRAM (独)、Epistar (台湾) はシェアランキングに残っているもののシェアは減少している。先行メーカの蛍光体等に関する有力特許の有効期間が切れ始めていることや中国メーカの参入が原因と考えられる。

#### 2-6. まとめ

第1章では、WSTS 統計に従い製品分類を、メモリ、MPU、システム LSI、アナログ IC、ディスクリートの5分類とした。第2章では更にビジネスモデルからアナログ IC・ディスクリート製品を製造する旧 IDM 型、メモリ・MPU を製造する専業 IDM 型、システム LSIを製造するファブレス・ファウンドリ型の3分類を定義した。各モデルの特徴を把握するため、米中貿易摩擦影響のない2018年(近年最高売上)の半導体売上データをもとに売上規模や各製品のメインプレヤーをピックアップした。メモリは、韓国の Samsung と SK Hynix が全体シェアの60%、MPU は米 Intel が90%シェアを持つ専業メーカとなっている。また、システム LSI は台湾ファウンドリと米のファブレスメーカのコラボで半導体製造の新しいエコシステムを構築している。

一方で、アナログ IC とディスクリートは寿命が長く品種が多岐に亘るためという理由で依然としてプレーヤ数が多い。アナログ IC は企業買収による売上拡大の動きとファブレス移行の動きがある。ディスクリートはパワー半導体・小信号半導体・光半導体・センサ等多岐にわたる製品群があり各製品群の売上規模が小さいことと素子単体ごとに性能による差異化を行ってきた経緯から標準化が困難となりファブレスに移行できず、旧 IDM 型の既存ビジネスを延長していると考えられる。

#### 第3章 アナログ IC・ディスクリート/メモリ・MPU/システム LSI 産業比較

#### 3-1. アプリケーション規模とライフサイクルの比較

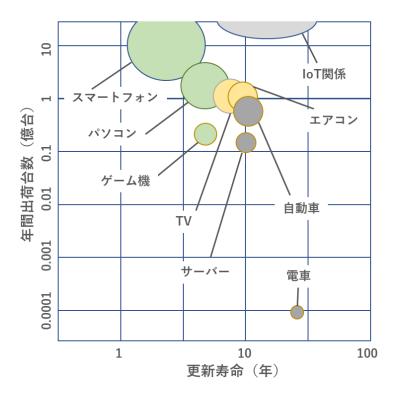

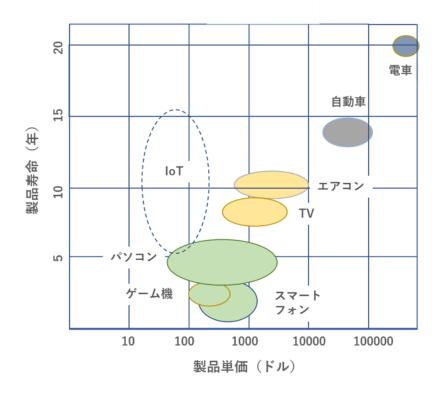

表 3-1-1.に半導体を使用したアプリケーション規模(2019 年度)とライフサイクル示した。メモリ・MPU の専業メーカはスマートフォン、パソコン、ゲーム機等の情報通信分野の民生製品がメインのターゲット顧客である。市場規模は年間 16.6 億台で平均製品寿命は 2~5 年であり短い[4][5][31]。更にモデルチェンジサイクルは 1 年程度と短い。TV やエアコン等の民生家電製品は省エネ指向を背景に年間 2.5 億台で販売され平均寿命は 7~10 年と長い[32][33]。自動車は年間 9200 万台で寿命は 12 年と家電製品より長い[34]。電車は 2 万台で生産台数は極めて少ないが寿命は短いもので 20 年である[35]。それぞれのアプリケーションで主要な半導体製品は異なり情報通信系の民生品にはメモリ・MPU・システム LSI が多く使用されているが、家電・自動車・産業機器にはパワー半導体やアナログ IC が使われている。IoT の定義は広く一般家庭、公共施設、社会インフラ等でセンサ、エッジマイコン、通信 LSI、システム LSI、メモリ、パワー半導体等が広く製品として含まれている。IoT の出荷規模は 274 億台となっているが他アプリケーションと重複している可能性があるため本章では分析対象から除いた。

寿命(年) 出荷 (億台/年) 主な半導体製品 スマートフォン 2 13.7 メモリ、システムLSI ゲーム機 5 0.3 メモリ、システムLSI パソコン 5 2.6 メモリ、MPU TV 7 1.4 システムLSI エアコン 10 パワーデバイス 1.1 システムLSI、パワーデバイス 12 0.92 自動車 0.0002 パワーデバイス 電車 20 センサ、システムLSI、アナログIC 5~15 274 ΙoΤ サーバー 10 0.12 メモリ、MPU、システムLSI

表 3-1-1. アプリケーション規模とライフサイクルの比較

図 3-1-1.に年間出荷台数を縦軸にライフサイクル横軸にアプリケーションをグループに 色分けした。寿命が短く出荷台数が多い緑色はスマートフォン、PC、ゲーム機でありメモリ・MPU・システム LSI が製品の性能を決定する主要部品である。ハードウェアコストの大部分を占める高付加価値な半導体製品である。スマートフォンの寿命はバッテリー寿命の 2 年程度と短い。ユーザーは 2 年毎に買い替えることが一般的となっている。この短いライフサイクルは、セットメーカと半導体メーカが製品や技術のロードマップを共有して作り上げた高収益ビジネスモデルのひとつであるといえる。

家電製品代表の TV やエアコンは橙色で示している。エアコンの年間出荷台数は地球温暖化 影響もあり 2019 年には 1 億台を超えている。省エネ買い替え需要もあり高性能インバータ 搭載が求められパワーデバイス需要が高まっている。寿命が 10 年以上と長い自動車は、機械部品から電子部品への転換が進んでおり、使用される半導体は、インバータ用 IGBT やパワーステアリング・燃料ポンプ用パワーMOSFET などディスクリート半導体が多用されている。

図 3-1-1. アプリケーション規模とライフサイクルによるグルーピング

# 3-2. 半導体コスト構造の比較

表 3-2-1.にメモリ、システム LSI、パワーMOSFET のコスト構造を示した。半導体製品間でコスト構造の比較をする場合、チップ面積が異なると組立コスト差影響が大きくなる。比較に際してメモリやシステム LSI で一般的な 5~7mm□のチップを想定して製品のコスト構造を比較した。ディスクリート製品の代表としてクリーンルームでの生産規模が最も大きいパワーMOSFET を選択しチップサイズ 5mm□の製品を想定した。

製品コストは各メーカ社外秘であるため文献情報など公開情報をもとにコスト費目の比率を示した[36](メモリとシステム LSI のコスト比較[37])。コスト費目はチップコストと組立コストと広義販売管理費(Large Commercial Cost)からなる。チップと組立は材料や直接労働など変動費と管理労務費や設備維持や減価償却などの固定費からなる。

表 3-2-1. 半導体製品コスト構造の比較

| 費用分類     |            | メモリ  | システムLSI | パワーデバイス |

|----------|------------|------|---------|---------|

|          | 直接材料費      | 4    | 3.8     | 12      |

|          | 直接労務費      | 4    | 3.8     | 20      |

| チップコスト   | 変動費(間材+外注) | 7.2  | 6       | 18      |

|          | 減価償却費      | 32   | 28.6    | 7       |

|          | その他固定費     | 9.6  | 9       | 6       |

| パッケージ材料費 |            | 1.6  | 2.3     | 16      |

| 組立コスト    | 労務費+変動費    | 3.2  | 3       | 8       |

|          | 減価償却費+固定費  | 18.4 | 18.8    | 3       |

| 1.00     | 研究開発費      | 12   | 17      | 5       |

| LCC      | 販売管理費      | 8    | 7.5     | 5       |

単位(%)

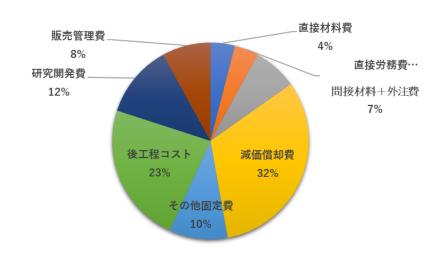

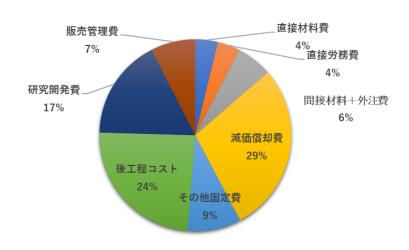

図 3-2-1.にメモリ製品のコスト構造と図 3-2-2.にシステム LSI 製品コスト構造を示した。両者での構造差は少ない。システム LSI はファウンドリを使用しているが設備投資の減価償却費は相応に負担しており同じレベルになっている。両者で差が大きいのは、研究開発費でありシステム LSI の場合 17%となっている。メモリも新製品開発や微細化技術開発で多くの研究費が必要だがシステム LSI の場合は回路設計に関する研究費が大きい。メモリに比べ多品種であることも研究費比率が大きい要因の一つと考えられる。

図 3-2-1. メモリ製品のコスト構造

図 3-2-2. システム LSI 製品のコスト構造

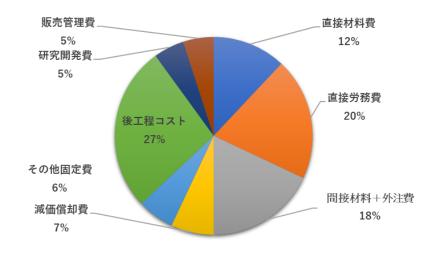

図 3-2-3.に示すパワーMOSFET のコスト構造はメモリやシステム LSI と大きく異なっている。組立コストは一般的にパッケージのピン数やテスト項目に依存するが、パワー MOSFET は放熱のためのフレーム材や樹脂材の直接材料コスト大きい。組立材料費の内訳はメモリやシステム LSI と異なるものの組立コスト比率は3製品で23~27%で大差はない。一方でチップコストの内訳が大きく異なる。パワーMOSFET の減価償却費率は7%でメモリやシステム LSI の 1/4 以下である。直接労務費が20%とメモリやシステム LSI の 5 倍である(製品の工程数を考慮すると 10 倍以上大きいといえる)。また研究開発費は6%でメモリの半分以下となっている。

図 3-2-3. パワー半導体 (パワーMOSFET) のコスト構造

#### 3-2-1. DEP 比較

減価償却費(DEP: Depreciation) は、設備投資に要した費用を設備使用期間で配分したもので製品寿命の短いメモリでは3年程度、寿命の長いアナログICなどでは5年程度が設定される。メモリやシステムLSIは競争力の源である"微細化と生産性"を得るために巨額の設備投資が必要である。表 3-2-2.に 2019年の製品メーカ別投資額をまとめた[38]。

表 3-2-2. 2019 年度 設備投資金額

| メモリ・    | MPU   | システムLSI      | アナログIC・ディスクリート |          |

|---------|-------|--------------|----------------|----------|

| Samsung | Intel | TSMC(ファウンドリ) | Renesas        | Infineon |

| 226     | 155   | 103          | 3              | 18       |

単位:億ドル

メモリトップシェアの Samsung が 226 億ドル、MPU シェア 90%の Intel は 155 億ドル、システム LSI の生産受け皿である TSMC(ファウンドリ)は 103 億ドルである。メモリ・MPU メーカやファウンドリは毎年このレベルでの投資を続けている。アナログ IC 世界 10 位の Renesas は 3 億ドル、パワー半導体トップの Infineon でさえ 18 億ドルでありメモリメーカと比較して桁違いに少ない。パワー半導体の生産ラインの自動化投資を節約することで DEP 発生を抑えることができるものの直接労働費比率が高止まり(20%)の理由にもなっている。

#### 3-2-2. 直材費比較

直材比率は、メモリやシステム LSI では 4%に対しパワー半導体では 12%と大きい。直材費の殆どは材料メーカから購入するウェハ費用と考えてよい。メモリやシステム LSI は 300mm ウェハの極表面領域にデバイスを形成するため、基板濃度など標準化した MCZ (Magneticfield applied Czochralski) ウェハの使用が可能である[39]。一方で、パワー半導体ではデバイスの耐圧系によりエピ層の濃度や厚さが異なり非常に複雑である。パワー半導体で生産規模が大きい低耐圧(100V 以下)のパワーMOSFET の場合、通電方向がウェハ上下であるためヒ素や赤燐等の高濃度不純物基板に耐圧やオン抵抗を最適化したエピタキシャル成長を行ったエピウェハを使用する。耐圧やその他特性にカスタマイズした製品ごとのエピウェハを材料メーカから購入するため 200mm の単純なエピウェハ(単層エピウェハ)でも 300mm のメモリウェハより高額な場合もある。中耐圧 MOSFET で主流になっているエピ層を積み重ねる Super Junction 構造のウェハは、製品ごとのパターニングとイオン注入を 5 回程度繰り返し製造するためセルトランジスタを形成する本工程以上に費用が掛かる場合がある[40]。更に生産規模は極めて少ないがハイパワー (2500V 以上)のウ

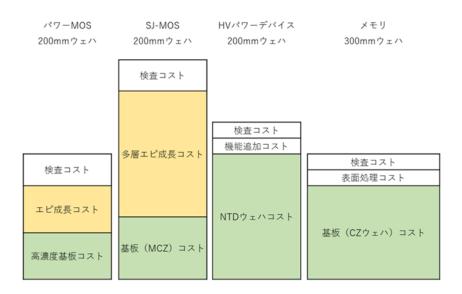

ェハは均一な低濃度のバルクを確保するため中性子線照射(NTD:Neutron Iradiation)により Si を P (リン) に替える技術が使われる[41]。この場合低燐濃度の FZ (Floating Zone) インゴット[42]に原子炉内で中性子線を照射し数か月の冷却期間をおいてウェハ加工するといった手間のかかる作業が必要である。図 3-2-2-1.に 300mm メモリウェハ、200mm 低耐圧パワーMOSFET ウェハ、200mm 高耐圧 SJ-MOSFET 用ウェハ、2500V クラスの HV パワーデバイス用中性子線照射(NTD)ウェハのコスト構造を示した。図 3-2-4.は一枚当たり(面積換算なし)のウェハコスト比較である。

図 3-2-4. 200mm パワー半導体ウェハと 300mm ウェハのコスト比較

パワー半導体向けのウェハは多品種に及ぶためエピ厚やエピ抵抗は抜き取り破壊測定を行う場合もあり検査コスト比率も大きい。また  $300 \, \mathrm{mm}$  標準ウェハの製造リードタイムは、 1 週間程度に対してパワー半導体は耐圧が高くなるほど長くなる。NTD ウェハはインゴットに原子炉中性子を照射し  $\mathrm{Si}$  を  $\mathrm{P}$  に変換することで非常に均一な不純物濃度( $\mathrm{1e12cm}^{-3}$ 程度)を得る秀逸な技術ではあるが放射化するため約 3 カ月の放置冷却期間が必要であり原子炉の能力で生産が制限されることもある。

# 3-2-3. ロットハンドリングコスト比較

パワー半導体コスト構造で直接労務費率が 20% (メモリやシステム LSI の 5 倍) と大き い理由は DEP 比較で説明したが投資を抑えた既存 200mm ラインで生産しているため自動 化が遅れていることが理由である。直労費 (直接労務費) は、既存の 200mm ラインでは凡 そロットハンドリング数に比例する。ウェハ 25 枚をロットケースに収め、人が処理装置に仕掛ける。処理が終了すると終了したロットケースを人が次の処理装置に運ぶといった作

業を行う。大規模な 300mm ラインでは高速な天井搬送 (OHV: Over Head Vehicle)を使用して無人でロットハンドリングが行われている[43]。人運搬に比べ 2 桁以上の生産性を有している。

第1章で示した生産性比較のレーダーチャートを図 3-2-5.に再度示した。300mmBig Fabをフルマークとして品質・生産性・生産管理を比較したものである。コストに大きくかかわる生産性の項目で、搬送・装置・検査工程自動化が 200mm ラインでは大きく遅れている。特に国内半導体メーカの場合、歴史的な背景もあり 200mm 化は 150mm ラインをベースに設備の口径アップだけの切り替えを行ってきた。生産管理システムもそのまま利用してきた経緯がある。200mm 切替当時としては投資圧縮とシームレスな生産を行うメリットがあった。しかし現在では装置オンライン化率が低いとか、天井の高さが低いため天井搬送システムが導入できないとか、細密に設備を配置したため装置のロードアンロードの自動化(装置自動化)ができないなど弊害が起こっている。人を使って搬送やロードアンロードや検査を行うため人海戦術的なラインに留まっている。また国内メーカは人からの発塵を心配するために、SMIF ポッド[44]を使用して装置外ダストを減らす努力をしてきた。2000 年以降に新設された海外 200mm ラインでは、安価なオープンカセットの天井搬送を導入しSMIF ポッドを使用しない生産ラインを構築しているファウンドリもある。ベンチマークに使用した 300mm の Big Fab\*は生産性・品質・デリバリを考慮して設計されておりその生産性は既存 200mmFab の 10~50 倍のスループット(ロット出力)を持っている。

注)\*BigFab 以外の少量生産 300mm ラインの生産性は既存 200mm ラインと同等である。

図 3-2-5. 200mm/300mm ラインの品質・生産性・生産管理能力比較

# 3-3. 半導体製品の信頼性比較

図 3-3-1.に表 3-1-1.の製品寿命と製品平均単価を示した。スマートフォンの平均単価は 300 ドル程度で交換寿命はバッテリー寿命に依存し約 2 年、PC の平均単価は 500 ドル程度で、寿命は内臓 SSD (5 年保証)に依存している。一般ユーザー向けで単価が安い製品の場合、故障時に原因を追究し修理対応することは少なく。短い製品寿命を考慮して新品と交換するケースが一般的になっている。民生半導体に要求される品質レベルは不良率~200ppm程度である[47]。一方で自動車の平均単価は 20000 ドル程度と故障時の新品交換対応は困難であることに加えて人命に関わる事故に繋がる可能性もあり "ゼロデフェクト"を要求される。実際の要求レベルは 1ppm 未満である[45][46]。2019 年トヨタ自動車の販売台数は 971 万台で不良が 1 台出た場合が 0.1ppm に相当する。Tier1 からの実要求レベルは車メーカより更に厳しくパワー半導体で 0.03~0.1ppm が要求されている。パワー半導体は民生半導体に比べ車載や産業用半導体は 2~3 桁高い信頼性を要求されている。

図 3-3-1. 製品寿命と製品単価

#### 3-4. 販売・生産管理比較

表 3-4-1.にメモリ・MPU とアナログ IC・ディスクリート製品メーカの販売・生産管理と 併せて新製品寿命・新製品生産比率\*をまとめた。(\*新製品比率は、全体売上に対する過去 3 年間に開発された製品の売上と定義する)

| 製品             | 流動製品 | 販売予測 | 需給管理 | 生産  | 製品寿命  | 新製品切替 | 新製品比率* | 投資効率 | 在庫 |

|----------------|------|------|------|-----|-------|-------|--------|------|----|

| メモリ・MPU        | 数十種  | 易    | 易    | 変動小 | 2~5年  | 0.5年  | 90%    | 마    | 少  |

| アナログIC・ディスクリート | 数千種  | 難    | 難    | 変動大 | 2~25年 | 2年    | 10%    | 低    | 多  |

表 3-4-1. 販売・生産管理と新製品寿命・新製品生産比率の比較

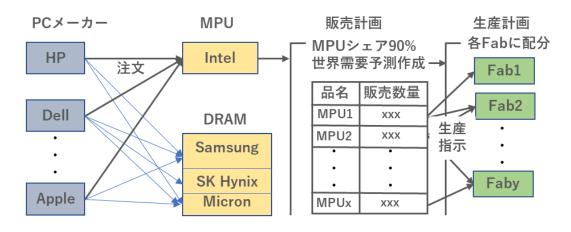

メモリ・MPU メーカは寡占化が進み、PC やスマートフォンメーカーと販売・生産・新製品開発計画ロードマップを共有しているため、生産・販売予測精度が高く計画的な設備投資と投資回収が可能となっている。また新製品切り替えサイクルが短く、製品寿命も短いため、過去の製品は在庫として残ることはない。一方でアナログ IC・ディスクリートメーカは、多品種で競業プレーヤ数が多く、販売・生産予測が困難なうえに、製品寿命が長いため、新製品の入れ替わりスピードは非常に遅い。また車載や産業用の新製品の場合、設備投資しても認定作業により投資回収が開始できるのは 3 年後というケースもある。民生分野の製品では競合が多く存在するため少量多品種で短納期のオーダーに対応しないと販売機会を失うため在庫保有量が多い。図 3-4-1.にメモリ・MPU メーカの販売・生産管理を示した。PCメーカも寡占化が進み HP、Dell、Apple など大手からの販売計画をもとに MPU はシェア 90%の Intel が外すことのない MPU 販売計画を作成しそれを基に全世界の自社工場に生産指示を出す。Intel の工場はコピーイクザクトリーでありどこの工場でも同じ品質で製品を製造することができる。

図 3-4-1. メモリ・MPU メーカの販売・生産管理

DRAM は、Samsung、SK Hynix、Micron でシェアしており MPU に比べ販売予測精度 は劣るものの PC での需要変化に対してはマーケットの異なるスマートフォン向けへの製品に配分することも可能で安定した生産計画を工場に指示することができる。

図 3-4-2.にアナログ IC・ディスクリートメーカの販売・生産管理を示した。メモリ・MPU のような専業半導体メーカとは異なりアプリケーション分野が広く競合する半導体メーカの数も多い。日本も家電メーカが国内で生産を続けていた 2000 年以前は精度の高い販売予測とそれをもとにした生産計画作成が可能であったが円高が進み国内産業の空洞化で生産拠点が中国・東南アジアに移った影響で直接営業から現地販社を介した営業を行うようになった。引取責任を伴わない現地販社には投機的な動きをするものも現れ実需要予測が非常に困難になっている。また、製品寿命が長いため新製品との入れ替えを計画しても顧客の切り替え認定作業が進まず品種数は増加の一途をたどり流動品種数だけでも数千品種を管理する必要に迫られている。生産を合理化するためにライン間で製品移管しラインを集約することが望ましいが客先認定とプロセスチューニングなどを行うリソースが必要である。現状ではそのリソースは不足しているため引取保証のない製品在庫を確保することや採算性を無視して古い生産ラインを維持する国内メーカも多い。

図 3-4-2. アナログ IC・ディスクリートメーカの販売・生産管理

# 3-5. 生産工場の比較

#### 3-5-1. 口径別 Fab

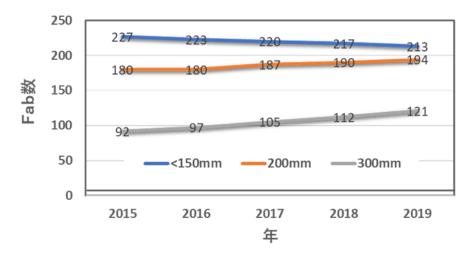

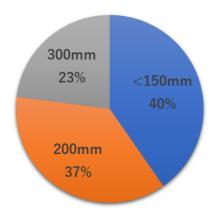

ウェハロ径別 Fab 数の推移を図 3-5-1.に示した[47]。また 2019 年の口径別 Fab 数の比率を図 3-5-2.に示した。世界総 Fab 数 538 に対して、口径 150mm 以下の Fab 数は 243 で2015 年から CAGR マイナス 1.5%で減少しているが、現在でも全体の 40%を占めている。口径 200mm の Fab 数は 194 で 150mm 以下の Fab と同様に減少していると予測されていたが、実際は CAGR+1.9%で増加している。IoT や車載用途のセンサ (MEMS センサ含む)やパワー半導体、エッジマイコンなどの需要増加が背景にある[48]。口径 300mm の Fab 数は 121 で全体では 23%であるが CAGR+7.8%で増加している。Big Fab を有する専業半導体メーカに加え中国が国産メモリ製品生産のため 300mm の Fab を建設していることが背景にある。

図 3-5-1. ウェハロ径別 Fab 数の推移

図 3-5-2. 口径別 Fab 数の比率 (2019年)

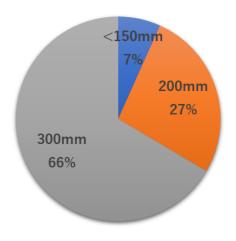

### 3-5-2. 口径別ウェハ使用量

2019年の Si ウェハの口径別面積使用量比率を図 3-5-3.に示した[49]。Fab 数比率 23%の 300mm ラインがウェハの使用量全体の 66%を占めている。単純な面積比率(2.25 倍)の要因 以外に 300mmFab 一棟あたりの生産性が高いことを示している。それぞれの Fab 平均面 積使用量を 200mm ウェハ枚数に換算し Fab 一棟当たりの使用量(K 枚/月・Fab)と、Fab 一棟当りのストレートロット数 (1 ロット=25 枚) でまとめたものを表 3-5-1.に示した。Fab の生産性を表すハンドリングロット数は上記ストレートロット数に製品の工数を掛けたものである。製品の工程数が同じだと仮定した場合でも 300mmFab は 200mm Fab の 4.5 倍、150mmFab の 22 倍の生産性を有していることが判る。面積換算してない出力ロット数で比較した場合 200mm ライン一棟の平均出力は 1000 ロット/月程度に対し 300mm ライン一棟の平均出力は 2000 ロット/月程度と倍になっている。しかしメモリなどの300mmBig Fab は 10000 ロット/月近くの出力を持つところも少なくない。300mmFab 一棟当たりの平均出力が 200mmFab の 2 倍程度である理由として総数 121 棟の 300mmFab には試作レベルの小規模な Fab もカウントされていることが考えられる。

実際の面積出力は 200mmFab と全自動 300mmBigFab を比較すると 1 桁以上の差がある と思われる。

図 3-5-3. 口径別ウェハ使用量(面積換算)

表 3-5-1. 口径別 Fab 平均ウェハ使用量と平均ロット出力

| 口径     | 200mm換算枚数(K枚/Fab・月) | ロット*換算(ロット/Fab・月) |

|--------|---------------------|-------------------|

| <150mm | 5.1                 | 360               |

| 200mm  | 25                  | 1000              |

| 300mm  | 113                 | 2000              |

300mmFab のメーカおよびファウンドリ生産高(製品売上高と異なる)ランキングを、図 3-5-4.に示した[49]。300mm 生産量 1,2,3,5 位はメモリメーカで全体の 65%を占めている。システム LSI の生産を引き受けている TSMC(4位) と GF (7位) で 20%、MPU を独占している Intel は 7%にとどまっている。PC を構成する MPU は基本 1 個、DRAM やフラッシュメモリは複数個使用されていることからも、Si 面積を大量に消費する製品はメモリであることがわかる。

図 3-5-4. 300mmFab のメーカおよびファウンドリ生産高比率

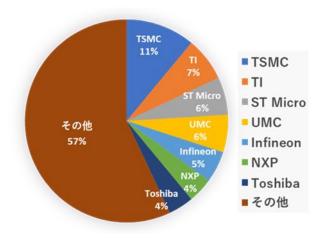

同じく 200mmFab についての生産高ランキングを図 3-5-5.に示した[49]。200mm ラインを使用する製品はアナログ IC とディスクリートである。1 位と 4 位は TSMC と UMC の台湾 200mm ファウンドリ合わせて 17%、その他は TI が 7%、ST Micro が 6%、Infineonが 5%、NXP と Toshiba が 4%で、老舗の半導体メーカが 200mm ラインを維持活用していることがわかる。その他が 57%を占めており各製品ごとのプレーヤが多く存在しそれぞれが 200mm ラインを維持しているものと考えられる。

図 3-5-5. 200mmFab のメーカおよびファウンドリ生産高比率

200mm ウェハの使用用途について分析するために製品別生産高を図 3-5-6.に示した[49]。ファウンドリが 28%を占めている。これはアナログ IC・ディスクリートのファブレスメーカの生産サポートをしていると思われる。次にディスクリートが 26%を占めるが、チップ 面積を消費するパワー半導体が大部分を占めていると考えられる。アナログ IC が 22%、低速度低集積度 MPU、MCU(車載用途等)が 15%、MEMS が 9%、不揮発性小容量メモリが 0.5%の構成となっている。将来的にアナログ IC や MPU 製品は Fab の老朽化で既存製品生産を維持できなくなった場合はファウンドリを使って生産を継続することになると思われる。ディスクリート(パワー半導体)や MEMS(センサ)は、微細化や新規技術の導入により開発要素が高く市場成長が期待できる。特にパワー半導体は 200mm から 300mm へのライン移行の時期にきていると思われる。性能向上効果と製品信頼性と経済性から判断すべきことである。300mm でパワー半導体の生産を始めているのは現時点で Infineon 1 社のみであり、今後も拡大するのか否か、経済性の課題をどう解決するのか注視したい。

図 3-5-6. 200mm ウェハの製品別生産高比率

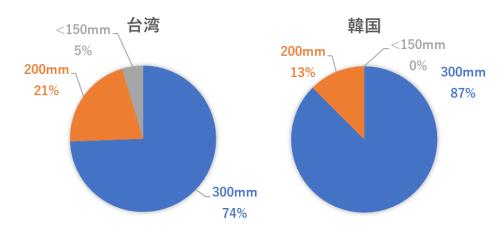

## 3-5-3. 国別ウェハ消費量

表 3-5-2.に 2019 年の国別口径別ウェハ使用量を示した[49]。表の数値は月あたりの200mm 換算ウェハ使用量で単位は百万枚である。国別総ウェハ消費量比率を図 3-5-7.に示した。台湾が22%で1位、韓国が21%で2位、日本が16%で3位となっている。第2章の表 2-2-1.で日本の半導体メーカの売上規模はKioxia(旧東芝メモリ)を除いてTOP10には存在していないことを示した。一方でウェハ(Si面積)の消費量は世界3位である。米国は日本に次いで4位(13%)と少ないが台湾ファウンドリでシステムLSIやアナログICを生産していることを考慮すると実質は世界ウェハ面積の30%以上を消費していると推定される。日本の半導体メーカはウェハ消費シェア(16%)と売上シェア(6%)が結びついていない。理由のひとつとして日本のメーカは低付加価値製品の生産比率が大きいことが考えられる。

表 3-5-2. 国別口径別ウェハ使用量(単位: M 枚/月,200mm 換算)

|     | 300mm | 200mm | <150mm | ウェハ消費量 |

|-----|-------|-------|--------|--------|

| 台湾  | 3.2   | 0.9   | 0.2    | 4.2    |

| 韓国  | 3.5   | 0.5   | 0      | 4.1    |

| 日本  | 1.9   | 0.8   | 0.5    | 3.2    |

| 米国  | 1.6   | 0.7   | 0.2    | 2.5    |

| 中国  | 1.4   | 0.9   | 0.3    | 2.6    |

| 欧州  | 0.3   | 0.7   | 0.1    | 1.2    |

| その他 | 1     | 0.7   | 0.1    | 1.8    |

その他 欧州 9% 6% 中国 13% 日本 16%

図 3-5-7. 国別の Si ウェハ消費比率 (Si 面積比率)

ウェハ消費量は各国 Fab の生産状況や生産ラインの合理化を反映する指標として有益である。図 3-5-8.と図 3-5-9.に台湾と韓国の口径別ウェハ消費量比率を示した。

図 3-5-8. 台湾の口径別消費比率

図 3-5-9. 韓国の口径別消費比率

図 3-5-10.と図 3-5-11.に日本と米国の口径別ウェハ消費量比率を示した。

図 3-5-10. 日本の口径別消費比率

図 3-5-11. 米国の口径別消費比率

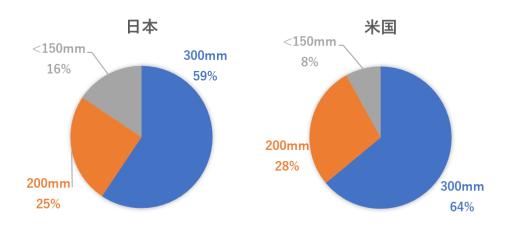

4 か国中で韓国の比率が特徴的である。150mm 以下は生産していない。また 300mm 生産が 87%を占めており半導体最先端国と言える。台湾はファウンドリ生産が比率に影響しており TSMC や UMC は 300mmFab を新設している一方で 200mm 以下の Fab も維持しアナログ IC やディスクリートメーカの生産受皿の役目を担っていることもあり 300mm 比率は 74%である。日本と米国の構成比は類似しているように見えるが米国のシステム LSIメーカは台湾の 300mm ファウンドリを活用しており米国の実質 300mm 比率は 80%以上あると考えられる。日本は 300mm 比率 59%と低く 200mm 比率 25%、150mm 以下 16%と 200mm 以下が非常に多い。日本の半導体メーカの多くは総合電機メーカから派生しており重電部門へのパワー半導体の供給を行ってきた経緯がある。パワー半導体やハイパワー半導体の材料は特殊なものが多くウェハ材料の口径アップは容易ではない。200mm 以下の Fab が残存する理由のひとつとして FZ ウェハなど特殊材料を使用しかつ寿命の長い製品を産業・車載分野に供給している産業界全体の背景が考えられる。

#### 3-6. ウェハロ径と生産性

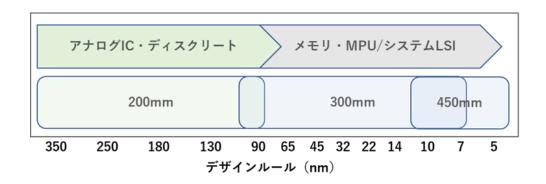

#### 3-6-1. ウェハロ径とデザインルール

半導体産業の発展には微細化によるトランジスタの集積度向上と大口径化による生産性向上が基本となってきた。"5 年で 1 桁の集積度アップ"はムーアの法則としてデジタル IC のすべてのロードマップとなった。ウェハロ径アップと併せて半導体設備メーカは、微細化に対応する新技術を導入し提供するようになった。図 3-6-1.に 200mm 以降のウェハロ径とデザインルールの関係を示した[8]。200mm の露光装置での限界は一般的に 0.13um であり以降は 300mm 液浸露光装置や EUV(Extreme UltraViolet)露光装置で装置開発が継続され

ている。現在はプロセスの工夫と組み合わせて 10nm レベルまでのパターニングが可能となっている。微細化の恩恵がデジタル IC ほど得られないアナログ IC やディスクリートは 200mm 露光装置限界に留まっている。

図 3-6-1. ウェハ口径とデザインルール

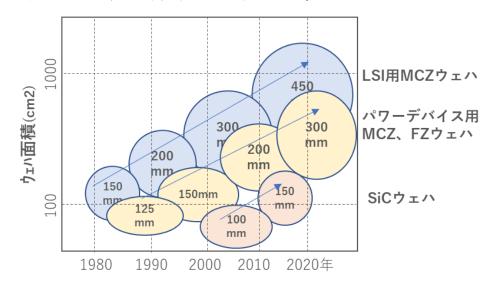

材料開発状況について図 3-6-2.に示した[50]。メモリ・MPU・システム LSI 製品用ウェハが材料メーカの大口径化を牽引している。300mm は 1990 年後半に 450mm は 2010 年に開発が完了している。一方で、パワー半導体用高濃度サブウェハや低濃度の MCZ ウェハや FZ ウェハの 300mm 開発は 2010 年後半からスタートしたばかりで、現在の 300mm パワー半導体ウェハ消費者は Infineon 1 社である。パワー半導体でポスト Si の最有力候補である SiC ウェハは 150mm で生産が行われているが全世界での使用量は極めて少ない。産業として発展するためには暫く時間が掛かると考えられる。

図 3-6-2. 製品別材料ウェハの大口径化

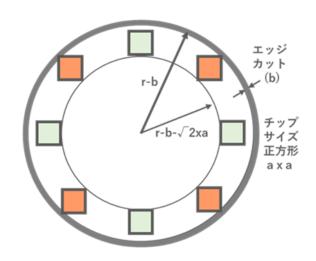

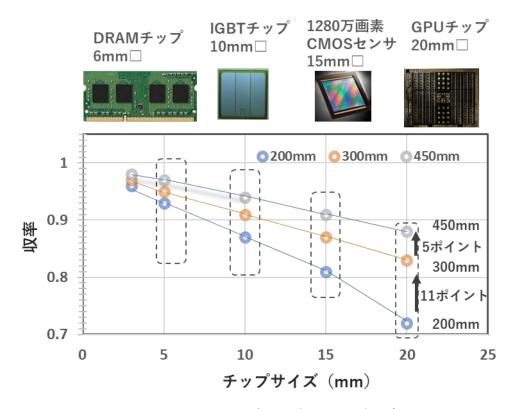

## 3-6-2. ウェハロ径とチップ収率

450mm ウェハが開発されて 10 年が経過している。大口径化には材料メーカのみならず装置メーカとの協業が必要である。半導体メーカとしてはインテルや TSMC (ファウンドリ) は 450mm へ移行を積極的に検討しているが、Si 面積消費量が多いメモリメーカが積極的でないように思われる。

図 3-6-3.にウェハロ径が変わるとウェハ内のチップ取高にどの程度の差がでるのかを計算する簡単なモデルを示した。計算ではチップは正方形で一辺がa(mm)、ウェハ半径をr(mm)、図中の同心円で挟まれた部分のチップ収率を $0.5(\alpha=2)$ 、エッジカット幅b=0とした。ウェハ総面積に対する製品チップ総面積比率Y(チップ収率)は式(1)で表される。

$$Y = 1 - \frac{\left(r - \sqrt{2}a\right)^2 / \alpha}{r^2} \tag{1}$$

図 3-6-3. 正方形チップによる収率計算

計算結果を図 3-6-4.に示した。チップサイズが 5mm の場合は 200mm→300mm で収率は +2 ポイント、300mm→450mm で収率は+1 ポイント変化する。標準的なメモリチップの大きさを 6mm $\square$ とした場合は、450mm 化しても収率改善は+1 ポイント程度に留まる。一方、チップサイズが 20mm と大きい場合は、200→300mm で収率は+11 ポイント、300→450mm では+5 ポイント増加する。 450mm 化で収率恩恵が得られる製品は、チップサイズが大きい MPU、AI チップ、ハイエンド CMOS センサである。 10mm $\square$ の IGBT の場合は、現状 200→300mm で収率+4 ポイント程度アップが望める。 Infineon のパワー半導体の 300mm 化は IGBT などの電力素子を製造する場合に+4 ポイントの収率アップが望める。 これは 300mm ラインで生産するだけで収益率+4 ポイント改善に直結することを意味する。

図 3-6-4. チップサイズによる収率の変化

# 3-7. 半導体製品ロードマップ

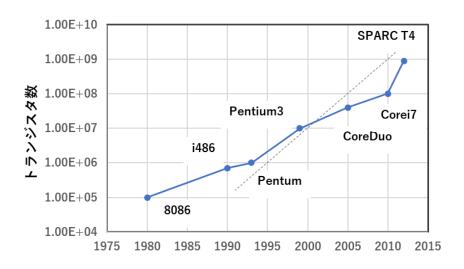

# 3-7-1. MPU とムーアの法則

メモリ・MPU メーカは、PC メーカと MPU 集積度やメモリ容量・スピード等の開発ロードマップを共有し業界全体でコンカレントな開発生産体制を築いてきた。MPU の集積度のロードマップには、ムーアの法則が背景にある[9]。半導体の微細化を示す指標で、"5 年で 1 桁集積度が向上する"というものである。単純なシュリンクに限定しなければ現在に至る四十年間続いている。図 3-7-1.に MPU チップ内トランジスタ数の変化を示した。近年少し停滞はあるが、ムーアラインに近い傾向を示している[51]。

微細化による速度性能向上に加えてコスト削減の効果があり、半導体産業成長の原動力となる法則である。

図 3-7-1. MPU チップ内トランジスタ数の推移

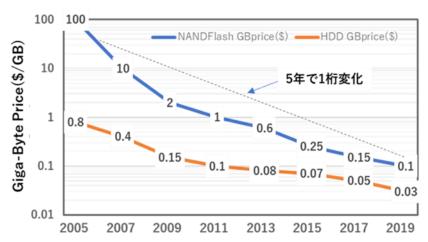

#### 3-7-2. フラッシュメモリと GB 単価

NAND フラッシュメモリの場合のロードマップは、ハードディスク(HDD)と比較して GB(ギガバイト)当たりの単価を如何に下げていくべきかを示したものである。単純な微細 化だけでなく多値化による容量アップが行われてきた。2015 年以降は構造を従来の 2 次元 から 3 次元に変え容量アップを続けている[52]。図 3-7-2.に GB 単価の推移を HDD と比較して示した。2005 年当初は HDD との差は 2 桁以上あったが 2018 年以降の差は 3 倍程度まで下がっている。プライスダウン線は 2005-2019 年の期間で同レート(5 年で 1 桁)で減少している。MPU やメモリ製品は集積度や GB 単価を共通ロードマップとして材料や装置メーカとコラボ体制を構築してきており、今後もコラボ体制を強化し成長を続けるものと思われる。

図 3-7-2. NAND フラッシュメモリと HDD のギガバイト単価の推移

#### 3-8. まとめ

2000年に旧 IDM 型エコシステムが崩壊して 20年経過した現在、アナログ IC・ディスクリートメーカとメモリ・MPU メーカは、投資規模、コスト構造、利益率などの経営指標が大きく異なっている。少量多品種製品を扱うアナログ IC・ディスクリートメーカは販売・生産管理、在庫管理が非常に複雑であり販売計画や生産計画の精度が低い。またアナログ IC・ディスクリート製品は産業や車載分野で多く使用されており寿命が長い。口径変更や合理化のための変更には客先認定が必要であり既存ラインを変更することが困難である。新製品の開発費は少なく微細化のためのライン投資なども困難になっている。半導体産業はアナログ IC・ディスクリートの旧 IDM 型ビジネスモデルとメモリ・MPU の専業 IDM 型ビジネスモデルの隔たりが拡大している。両ビジネス間の隔たりを埋めるものがファブレス/ファウンドリモデルである。国内の半導体メーカは新製品開発に積極的にファウンドリの活用を図るべきである。

微細パワー半導体は 300mm ライン移行への端境期にあるが、微細化投資で先行している Infineon に比べ国内パワー半導体メーカは製造ラインや微細化技術に関する知見に乏しい。微細化による技術課題を早期に予測し設計に反映することが国内パワー半導体メーカの継続成長に必要であると考える。第 4 章では、微細化による特性影響と露光装置や加工装置の工程能力影響を定量化する。第 5 章では、工程欠陥の歩留に及ぼす影響を定量化する。これらの結果は、量産に耐え得る微細パワー半導体設計の一助になるものと考える。

## 第4章 微細パワーMOSFET の Vth モデル

# 4-1. 微細化による Vth の上昇現象

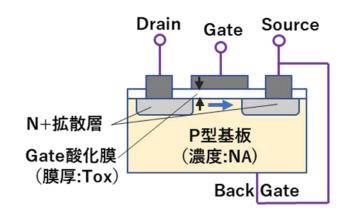

# 4-1-1. Vth の一般モデル

一般的な Nch 横型 MOSFET の断面構造を図 4-1-1.に示す。P 型基板に N+型ソースとドレイン拡散層を形成しゲート酸化膜を介しソース拡散層とドレイン拡散層の間にゲート電極を形成する。ゲートをソース電位基準でプラスにバイアスすることでゲート酸化膜直下が N 型に反転し電流が流れる。横型 MOSFET の Vth を式(2)に示す[53]。

図 4-1-1. Nch 横型 MOSFET の断面構造図

$$V_{th} = V_{FB} + 2\phi_b + \frac{\sqrt{4\varepsilon_{Si}N_A q\phi_b}}{(\frac{\varepsilon ox}{Tox})}$$

(2)

式(2)で電気素量 q、Si と SiO2の比誘電率( $\epsilon$ )については表 3-1-1.に示した。計算では P 型 基板濃度(チャネル濃度)NA を  $1e17(cm^{-3})$ 、ゲート酸化膜厚 Tox=50nm を使用した。 $\phi$ b は P 基板(NA)のフェルミレベルと真性順位の電位差であり、NA の 1 桁変化で 0.05V 変化 することから  $\phi$ b=0.3(V)とした。また VFB はゲート電極仕事関数と Si コンダクションバンドの電位差で N 型ポリシリコン 1e18  $(cm^{-3})$  を想定し VFB は 0.15V である。式(2)から Vth は酸化膜厚(Tox)と P 基板濃度(NA)が主パラメータである。本章では UMOSFET の Vth をモデル化するが、図 4-1-1.の横型 MOSFET と比べてベース濃度(チャネル方向)NA が一定でないこと、ゲート・コンタクト距離(横型ではゲートとバックゲート距離)が短い場合にチャネル垂直方向の影響(NA の濃度変化がなくとも)で Vth 上昇が起こることをモデル化する。

### 4-1-2. UMOSFET の Vth 一般モデル

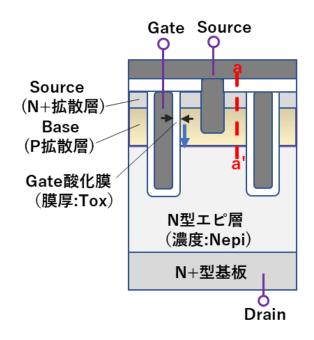

横型 MOSFET と UMOSFET の構造差は、電流を横方向に流すか縦方向に流すかの差である。横型 MOSFET のチャネル濃度は、基板濃度(NA)が一定であるが、UMOSFET はバイポーラトランジスタの製造工程に同じくベース拡散・ソース拡散の二重拡散が用いられる[54]。二重拡散により形成される N 基板のドレインとソース(N+)層に挟まれたベース領域がチャネル領域になる。そのため、チャネル領域の濃度は横型 MOSFET のように一定ではない。図 4-1-2.に UMOSFET の断面構造図を示す。

図 4-1-2. UMOSFET の断面構造図

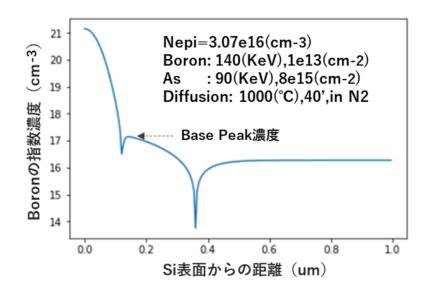

図 4-1-2.の a-a'位置で切り出した UMOSFET のチャネルプロファイルを図 4-1-3.に示す。一次元のチャネルプロファイル計算は、インプラ飛程や不純物拡散定数等から容易に計算できる[55]。図 4-1-3 のプロセス条件は、エピ層濃度(Nepi)3.07e16 (cm<sup>-3</sup>) の基板にベース層を加速電圧 140KeV、ドーズ量 1e13(cm<sup>-2</sup>)で Boron を注入、ソース層を加速電圧 90KeV、ドーズ量 8e15(cm<sup>-2</sup>)で As を注入した後、N2 雰囲気で 1000℃,40 分の拡散を行った場合のプロファイルである。ソース拡散層に近い領域でのベース Peak 濃度は、1.4e17(cm<sup>-3</sup>)である。ゲート酸化膜厚を 50nm として式(2)の NA の替りに Peak 濃度を使って求めた Vth は 2.3V となった。

図 4-1-3. UMOSFET の一次元プロファイル

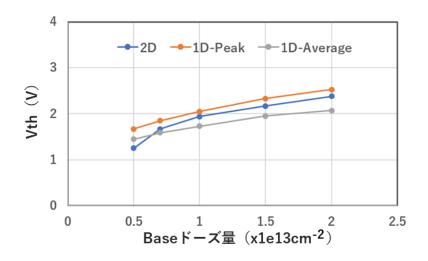

二重拡散による不均一ベース濃度の場合にベース Peak 濃度を用いることで、UMOSFET の Vth が見積れることを検証するために、2 次元プロセス・デバイスシミュレータとの比較を行った。ゲート酸化膜厚が 50nm の場合、ベースの Boron 注入量をパラメータに Vth を求めた結果を図 4-1-4.に示した。1 次元モデルでベース Peak 濃度を使用した場合を赤線(1 D-Peak)とベース平均濃度を使用した場合を緑線(1 D-Average)で表示した。2 次元シミュレータで計算した結果を青線で示した。一次元計算では平均濃度より Peak 濃度を使用することで二次元計算に近い結果が得られることが判った。

図 4-1-4. UMOSFET の Vth 計算 (二次元シミュレータとの比較)

# 4-1-3. 微細化による Vth 上昇の一般論

トレンチョンタクト構造の底部と側壁には、コンタクトのオーミック性を得るために P+ 拡散層を形成する[15]。一般的にはコンタクトオーミック形成には複数回の BF2 イオン注入が行われる。側壁注入のため $\pm$ 7°の斜めインプラと底部注入のための 0°インプラが行われる。活性化で P+拡散層を広げないために RTA (Rapid Thermal Anneal 装置) により 900°C 30 秒程度の活性化アニールが行われる[56]。 UMOSFET のコンタクト部に形成された P+ 拡散層の断面図を図 4-1-5.に示した。

図 4-1-5. UMOSFET のコンタクト P+拡散層

微細化による Vth 上昇はゲート・コンタクト距離 (crl) が短い場合や P+拡散がゲート界面領域まで拡散した場合にベースチャネル領域濃度の上昇に伴って Vth 上昇が起こる現象である。図 4-1-6.微細化によりコンタクト P+拡散層がゲート界面に近づいた場合にチャネル領域の濃度が上昇する様子を示した。

図 4-1-6. 一般的に考えられている微細化による Vth 上昇モデル

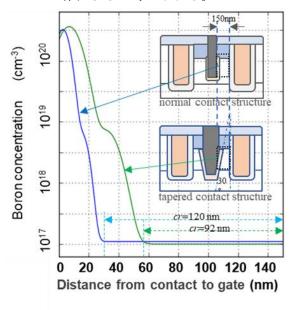

# 4-1-4. トレンチ側壁からの P+拡散長

ゲート・コンタクト距離(crl)が 150nm のトレンチコンタクト構造を持つ一般的な UMOSFET の P+拡散層を 2 次元のプロセスシミュレータにより計算した。結果を図 4-1-7.に示す。P+層はコンタクト底部では深くなっているが側壁方向の拡散層は短くなっている。0°注入と $\pm 7$ °2 回の BF $_2$ インプラを行うが両方の影響を受ける底部で深く、 $\pm 7$ °注入のみの影響を受ける側壁部では浅く形成される。

図 4-1-7. 2 次元プロセスシミュレータによるコンタクト付近の Boron 分布

図 4-1-7.の b-b'方向のゲート界面からコンタクト側壁までの Boron 拡散プロファイルを 図 4-1-8.に示した。ゲート・コンタクト距離 (crl) は 150nm であり、側壁 P+拡散層の厚 さは 30 (nm) 程度である。ゲート界面からは 120nm 離れており P+拡散層によるチャネル 濃度への影響はない。

図 4-1-8. コンタクト側壁からの P+拡散層プロファイル

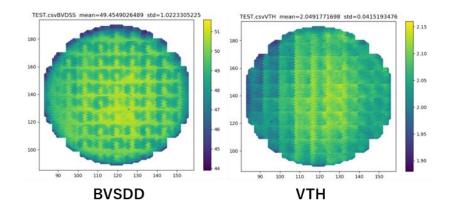

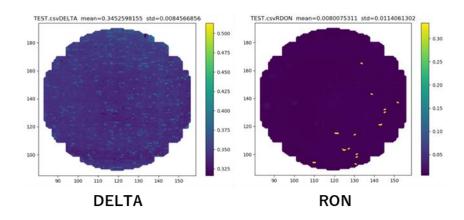

### 4-2. トレンチコンタクト構造 UMOSFET のウェハ面内 Vth バラツキ

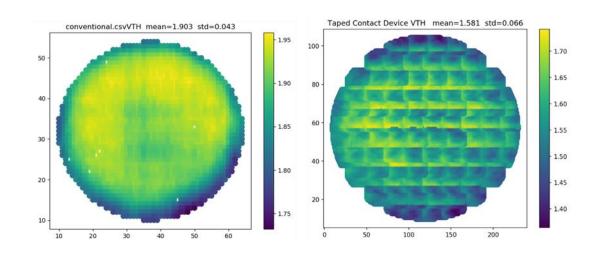

ゲート・コンタクト距離が共通 (crl=150nm)な 2 種類の UMOSFET についてウェハ面 内 Vth 分布に大きな差が見られた (図 4-2-2.)。構造差は一般的な垂直コンタクト構造とソース拡散層より下部で  $30^\circ$ のテーパを持つテーパコンタクト構造の差であり両構造を図 4-2-1.に示した。

図 4-2-1. コンタクト構造の異なる UMOSFET

両構造でセルサイズ、ドレイン領域不純物濃度(Nepi)、ベース Peak 濃度は略同じであるが、ゲート酸化膜厚は垂直コンタクト構造で 60nm、テーパコンタクト構造で 50nm であった。垂直コンタクト製品は車載用でありゲート信頼性を確保するため通常のゲート膜厚 50nm に対して 1.2 倍の 60nm となっている。両構造のウェハ面内 Vth マップを図 4-2-2. に示す。

図 4-2-2. 垂直コンタクト構造とテーパコンタクト構造のウェハ面内 Vth マップ

テーパコンタクト構造では、鱗状の周期パターンが現れている。周期パターンは露光装置のショットマップを反映したもので、露光装置レンズ収差等が原因で発生する露光寸法バラツキの影響によるものと考えられる[57]。次節以降で、テーパコンタクト構造で発生する周期パターンについて露光バラツキを考慮したモデル検証を行う。

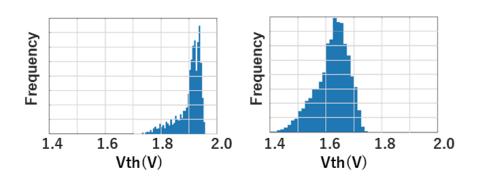

ウェハ内のチップトランジスタの Vth ヒストグラムを図 4-2-3.に示した。垂直コンタクト構造のゲート酸化膜厚は 60nm であり Vth の平均値は 1.90V、標準偏差は 43mV であった。テーパコンタクト構造の Vth 平均値は 1.58V、標準偏差は 66mV であった。平均 Vth はゲート酸化膜厚比 60/50 に対して平均 Vth 比は 1.90/1.58=1.2 であり膜厚比による上昇分である。一方で Vth バラツキには大きな差がみられる。両構造で Vth 低い側のテールはウェハ周辺の低 Vth に引っ張られており共通の事象であるが、それを除いたテーパコンタクト構造の分布バラツキは面内バラツキ以上のショットエリア内のバラツキによるものである。(テーパコンタクト構造 Vth の  $\sigma=66mV$  をショット内と面内に分解すると、ショット内の  $\sigma=46mV$ >面内  $\sigma=42mV$  であり、ショット内のバラツキが大きい。)

図 4-2-3. 垂直コンタクト構造とテーパコンタクト構造のウェハ面内 Vth 分布

両構造での大きな違いはコンタクトテーパの有無である。コンタクトインプラ工程で  $0^\circ$  注入と $\pm 7^\circ$ 注入を行う。垂直コンタクト構造では基本的にコンタクト側壁には $\pm 7^\circ$ 注入分のみであるが、テーパコンタクト構造では $\pm 7^\circ$ と  $0^\circ$ 両方の注入影響を受ける。また  $30^\circ$ テーパによりコンタクト側面からの P+拡散長が大きくなると考えられる。Vth はベース Peak 濃度に依存するため Peak 領域であるソース・ベース接合位置の P+拡散プロファイルを比較することが重要である。シミュレーションにより両構造のベース Peak 位置でのコンタクト側壁からの P+拡散プロファイルを計算し図  $4\cdot 2\cdot 4\cdot$ に示した。プロファイルのこぶは実際のプロセスでコンタクト  $BF_2$  イオン注入を 3 回行なっているためである。図  $4\cdot 2\cdot 4\cdot$ からテーパコンタクト構造ではソース拡散層直下(ベース Peak 濃度付近)の P+拡散長は 58nm となり垂直コンタクトの 30nm に比べ 2 倍近く深くなっている。しかしテーパコンタクト構造でもゲート界面からベース濃度変化が起こってない距離は 92nm ある。これはテーパコンタクト構造がチャネル領域濃度に影響を与えるレベルにはないことを意味している。

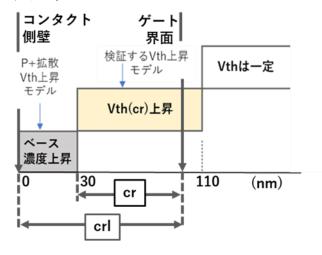

P+拡散層がチャネル領域に影響を与え Vth 上昇が起こる前に P+拡散層を除くゲート・コンタクト距離を実効 cr 長 (cr) として crl と区別する。図 4-2-4.の垂直コンタクト構造の cr=120nm に対しテーパコンタクト構造では cr=92nm である。cr が 80nm を切るあたりで Vth が上昇するメカニズムが存在すると考えられる。

図 4-2-4. 垂直コンタクト構造とテーパコンタクト構造の P+拡散プロファイル

図 4-2-5.にゲート・コンタクト距離(crl)が短くなると起こる Vth 上昇現象について、従来の P+拡散の影響でベース濃度が上がり Vth 上昇するモデルとの違いを明確にするために Crl 長値を併記した。 CP+拡散影響が起こる前の Crl Crl

図 4-2-5. ゲート・コンタクト距離 (crl) と Vth 上昇モデル

# 4-3. ゲート・コンタクト距離が短い場合の Vth モデル

### 4-3-1. ゲート空乏層パンチスルーモデル

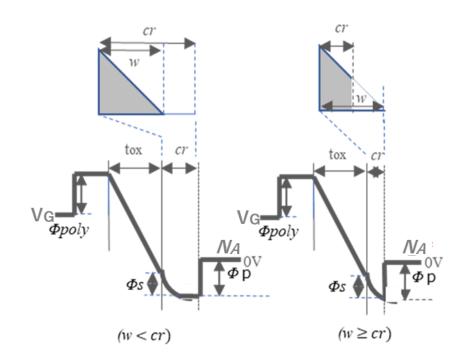

本節の Vth 計算では、crl から P+拡散層を除いた実効的なゲート・コンタクト距離 cr を使用した。cr が十分大きな場合、ゲートバイアスによるゲート空乏層は P+拡散層まで到達せずベース領域内部で終端するためゲート表面電位は cr の影響を受けない。cr が小さくなるとゲート空乏層が通常 Vth より低いゲート電圧で P+拡散層にパンチスルーを起こすことが考えられゲートバイアスによる表面反転層を形成する感度が小さくなり表面を N 型に反転させるためにはより高いゲートバイアスが必要になり Vth が上昇すると考えられる。ゲート空乏層幅を w とし、w<cr (パンチスルーしない場合)と w>cr (パンチスルーする場合)に分けてそれぞれのポテンシャルを図 4-3-1.に示した。

図 4-3-1. ゲート空乏層(w)と cr の大小関係によるポテンシャル図

ゲート空乏層幅 w は、式(3)より求められる。

$$w = E_{si} \cdot e \cdot \varepsilon_{si} q \cdot NA, \tag{3}$$

w<cr の場合は、式(4)により、Si 表面電界  $E_{si}$ に対して、表面電子濃度  $N_{s1}$ とゲート電圧  $V_{g1}$ を求めることができる。

$$\phi_{s1} = w \cdot Esi/2 - \phi p,$$

$$N_{s1} = n_i \exp(q \phi_{s1}/kT),$$

$$V_{g1} = t_{OX} \cdot \mathcal{E}_{ox} - \Phi n - \phi_{s1}.$$

(4)

また同じように w>cr の場合は、式(5)により、Si 表面電界  $E_{si}$ に対して、表面電子濃度  $N_{s2}$  とゲート電圧  $V_{g2}$ を求めることができる。

$$\phi_{s2} = cr \cdot (2Esi - q \cdot NA \cdot cr/\varepsilon_{si}/e)/2 - \phi p,$$

$$N_{s2} = n_i \exp(q\phi_{s2}/kT),$$

$$V_{g2} = t_{OX} \cdot \mathcal{E}_{oX} - \phi n - \phi_{s2}.$$

(5)

使用した物理定数を表 4-3-1.に示す。

表 4-3-1. 物理定数

| q                           | Elementary charge       | 1.6 x 1e19 C            |  |

|-----------------------------|-------------------------|-------------------------|--|

| $\mathcal{E}_{\mathit{S}i}$ | Si dielectric           | 11.7 x8.854x 1e14 F/cm  |  |

| $\mathcal{E}_{OX}$          | SiO2 dielectric         | 3.8 x 8.854 x 1e14 F/cm |  |

| $\boldsymbol{k}$            | Boltzmann constant      | 1.38 x 1e23 J/K         |  |

| ni                          | Intrinsic concentration | $1.18  x1e10  cm^{-3}$  |  |

|                             |                         |                         |  |

また、使用したデバイスパラメータを表 4-3-2.に示す。

表 4-3-2. デバイスパラメータ

| P base concentration $(NA)$ | $1.0 \ x \ 1e17 \ cm^{-3}$ |

|-----------------------------|----------------------------|

| Gate poly-Si concentration  | $1.0 \ x \ 1e18 \ cm^{-3}$ |

| Gate oxide thickness (tox)  | 50 nm                      |

|                             |                            |

\_\_\_\_\_\_

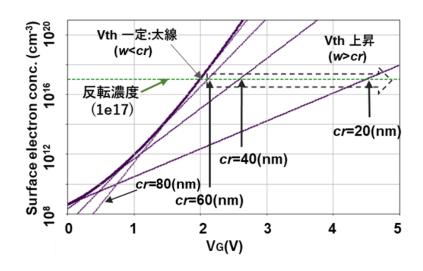

UMOSFET のベース濃度(NA)は、第 4 章 1 節で説明したベース Peak 濃度である。実際の計算は、cr を 20,40,60,80nm として式(5)を使用して計算した。また従来の w<cr の場合は cr 依存性のない式(4)を使用した。Si 表面電界を媒介パラメータとしてゲート電圧と Si 表面の電子濃度を計算したものを図 4-3-2.に示した。

図 4-3-2. ゲートバイアスと Si 表面電子濃度(cr=20,40,60,80nm)

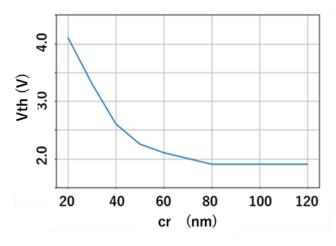

図 4-3-2.の太線は w<cr の場合で cr 依存性はない。w>cr の場合(ゲート空乏層パンチスルーモデル)表面電子濃度カーブは cr に依存する。太線と各 cr 値のカーブは接しており、その接点電圧が各 cr でのパンチスルー電圧である。cr=60nm のパンチスルー電圧は 1.2V であり 1.2V 以下では電子濃度は太線カーブに従い 1.2V 以上では cr=60nm のカーブに従う。cr=60nm での反転 Vth は約 2.1V とわずかに上昇する。cr=40nm の場合のパンチスルー電圧は 0.5V で反転 Vth は約 2.5V となる。cr=20nm の場合の反転 Vth は約 4.5V となり急激に上昇する。図 4-3-3.に cr と Vth の関係を示した。cr<80nm で Vth の上昇が起こり始める。cr<25nm で Vth は 2 倍の 4V を超え、拡散やゲート酸化等のプロセスより加工寸法依存性が大きくなる。垂直コンタクト構造の P+拡散層 30nm に cr に加えるとゲート・コンタクト距離(crl)が 55nm になると vth が 4V まで上昇することになる。テーパコンタクト構造では P+拡散層長が垂直コンタクト構造(30nm)の約倍の 58nm と大きいため寸法バラツキの影響に敏感になることが予測される。

図 4-3-3. Vth の実効 cr 長依存性

### 4-3-2. 製造工程バラツキ

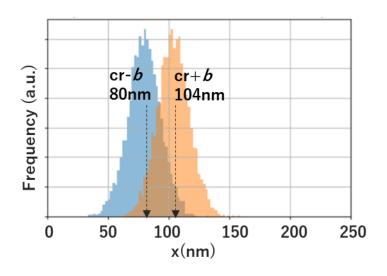

ゲート・コンタクト距離 (crl) が短くなると急峻な Vth 上昇が起こることを示した。crl をばらつかせる製造要因はゲート・コンタクトの加工バラツキ、露光装置のバラツキとパターンの合わせずれの3要因が考えられる。加工バラツキに関しては、露光装置のバラツキを排除して加工バラツキを調べるために図 4-3-4.に示したウェハ面内のショットエリアの右上のチップ断面から crl をウェハ全領域で測定した。結果平均 crl は 150(nm)、標準偏差は13.3nm であった。

図 4-3-4. ウェハ面内の crl 長測定筒所

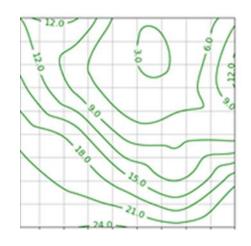

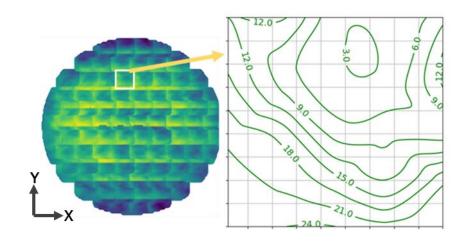

露光装置バラツキに関しては、ショットエリアのレンズ収差による露光寸法バラツキが考えられショットエリア内のチップ断面からトレンチパターンの開口寸法と設計値との差(広がり:a)を測定した。aと crl の関係を図 4-3-5.に示した。ゲート加工後にゲート酸化を行うため図 4-3-5.では crl にゲート酸化膜厚を加えた crt で表現している。ゲートとコンタクトは同じ露光装置を使用するため crt,crl,cr ともに-aの影響を受ける。図 4-3-6.に設計値に対するゲート開口パターン広がり値の等高線マップを示した。ショット領域左下で最大で 24(nm)の広がりが発生している。

図 4-3-5. 広がりパラメータ a の crl への影響

図 4-3-6. ショット内トレンチパターンの開口広がり(a)分布

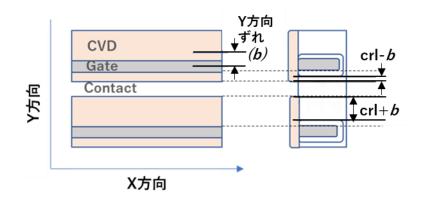

パターンの合わせずれに関しては、ゲートパターンとコンタクトパターンの合わせずれが crl に影響する。一般的にゲートパターンを基準にしてコンタクトパターンが形成される。一般的な UMOSFET はゲートとコンタクトパターンの配置を図 4-3-7.に示した。ゲートとコンタクトは平行に配置され crl に対して X 方向の合わせずれの影響はないが Y 方向シフト量(b)の影響が大きく crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl-crl

図 4-3-7. ゲート・コンタクトパターン合わせずれ(b)による crl 変化

# 4-3-3. 製造工程バラツキを考慮したチップ Vth の計算

一般的なトレンチコンタクト構造 UMOSFET のチップサイズは 4(mm²)、セルサイズは 1.5um、チップ内の有効セル領域面積はチップサイズの 80%である。この場合チップ全体 の総チャネル幅は 4m になる。チップ全体は多くのセルトランジスタから構成されている。

製造工程のバラツキはショットレベル、チップレベルのみならずセルトランジスタレベル に影響している。測定されるチップトランジスタ閾値 (Vth) はチップ単位の値で、チップ 内に含まれるセルトランジスタの閾値(vth)の平均値とみなすことができる。

微細化パラメータの cr が大きくセルトランジスタ vth が cr 依存性を持たない場合は従来どおり Vth=vth であるが、cr が短くセルトランジスタ vth が cr 依存性を持つ場合は、セルトランジスタの vth 分布を考慮する必要がある。図 4-3-8.にテーパコンタクト構造 UMOSFET の加工バラツキを考慮した場合にセルトランジスタ vth に与える影響を示した。

図 4-3-8. 加工バラツキを考慮したセルトランジスタ vth への影響

テーパコンタクト構造 UMOSFET のゲート・コンタクト距離(crl)は実測値から平均 150nm で標準偏差が 13.3nm であった。図 4-3-7.の薄緑色で示した右側ガウシアン分布が その分布である。テーパ構造の P+拡散層は 58nm を除いた実効 cr 長(cr)は平均 92nm で標準偏差は実測値と同じ 13.3nm とした cr が緑色で示した左側ガウシアン分布となる。セルトランジスタの vth(cr)カーブは実効 cr 長(cr)を基準に表示されており cr が 80nm 以下で vth 上昇が起こる。cr 分布の左側の分布裾野部分は vth 上昇の影響を受ける。一方で crl が 150nm の垂直コンタクト構造では、cr は平均 120nm 標準偏差 13.3nm で図 4-3-7.の二つの分布の中間に位置しセルトランジスタ vth の上昇影響は受けないレベルである。チップトランジスタの Vth はセルトランジスタの cr 分布と vth(cr)曲線のコンボリューション計算から求めることができる。なおテーパコンタクト構造の Vth 実測値にはゲート界面電荷影響 (約 0.5V) が加わっていると考えられ crl>100nm の Vth (vth0) は測定平均最小値を計算に採用した。

加工バラツキの他の要因である露光装置の開口寸法広がり(パラメータ:a)とゲート・コンタクトパターンの Y 方向合わせずれ(パラメータ:b)を含めたモデルに拡張する。

図 4-3-9.に開口寸法広がり(a)を考慮した cr 分布を示す。P+拡散長を含めた幾何的 crl に対して、P+拡散長を除いた電気的な cr を基準に広がり(a)だけ平均値を左にシフトした分布である。横軸の x が小さくなると vth 上昇の変調を受けて、セルトランジスタ vth 分布は高い方にすそ野を引く非ガウシアン分布となる。

図 4-3-9. 開口寸法広がりパラメータ(a)を考慮した cr 分布

a=0nm から a=24nm に広がった場合に起こる分布変化をテーパコンタクト構造 UMOSFET (cr=92nm) の場合について a=0nm と a=24nm の二つの分布を正規乱数 (5000 個のセルトランジスタ) で発生させたものを図 4·3·10.に示した。5000 個分のセルトランジスタの実効 cr 長分布と vth 分布変化をそれぞれ図 4·3·10.と図 4·3·11.に示した。図 4·3·10. では二つの正規分布が 24nm 離れていることが確認できる。 青色の分布は cr 長 150nm から P+拡散長 58nm を除いた実効 cr 長 92nm を平均とする分布でありオレンジ色の分布は広がりパラメータ a=24nm を加えた分布である。両分布の標準偏差には実測した加工バラツキ 13.3nm を使用している。

図 4-3-11.に示した青色の分布は a=0nm のセルトランジスタ vth 分布でオレンジ色の分布は a=24nm である。 a=24nm の分布は対称性の崩れと高 vth へのすそ引きが a=0 の分布と比較して顕著になっている。セルトランジスタ vth 分布の平均は、a=0 から 24nm に変化することで 1.48V から 1.64V に上昇している。バラツキも増加していることが判る。

図 4-3-10. パラメータ a によるセルトランジスタ cr 分布の変化

図 4-3-11. パラメータ a によるセルトランジスタ vth 分布の変化

パターン開口広がりパラメータ (a) を含むチップトランジスタ Vth は、セルトランジスタ Vth の平均値であることから式(6)(7)(8)から求められる。g(x)は標準偏差 13.3nm のガウス 関数、 $x_0$ は cr に P+拡散層長を加えたもの(crl)である。 $v_{th\,0}$ はゲート空乏層パンチスルーが起こらない場合(cr が大きい場合)のセルトランジスタ vth である。

$$d(cr) = \int_0^\infty v \, th(x) \cdot g(x - cr) \, dx \tag{6}$$

$$d(cr, a) = \int_0^\infty v \operatorname{th}(x) \cdot g(x - cr + a) dx \tag{7}$$

$$Vth(cr,a) = d(cr,a)/d(x_0) \cdot v_{th 0}$$

(8)

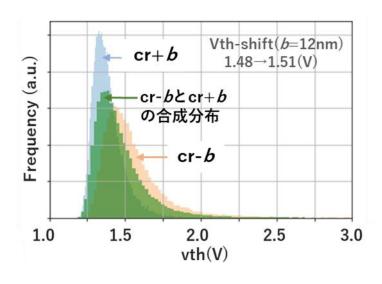

次に、ゲートパターンとコンタクトパターンの Y 方向合わせずれパラメータ(b)を考慮したチップトランジスタ Vth の計算を行う。合わせずれパラメータ(b)を考慮した場合にコンタクトの左右で cr が異なる様子を図 4-3-12.に示す。青色破線の分布が合わせずれがない場合の分布、二つの赤色実践の分布が合わせずれにより生じる二つの分布である。 cr の平均値が cr+b の分布と cr-b の分布ができる。特に cr-b の分布はセルトランジスタ vth の上昇影響を受けやすい。テーパコンタクト構造 UMOSFET について、広がりパラメータ a=0nm として、合わせずれパラメータ (b) を実測定での最大値 12nm とした場合の二つの分布を図 4-3-13.に示す。

図 4-3-12. 合わせずれパラメータ(b)を考慮した cr 分布

図 4-3-13. パラメータ bによるセルトランジスタ cr 分布の分離

図 4-3-14.は分離したセルトランジスタ vth の分布を示した。青色の分布は cr-b を平均と するセルトランジスタの vth 分布、オレンジ色の分布は cr+b を平均とするセルトランジスタ vth の分布である。緑色の分布は cr-b と cr+b の両分布を合成し規格化した分布である。合成した分布の平均値がチップトランジスタの Vth となる。テーパコンタクト構造 UMOSFET の場合の最大パターン合わせずれ b=12nm を入れた場合 1.48V から 1.51V に上昇する結果となった。上昇量は 0.03V 程度であり予想以上に小さい結果となった。

図 4-3-14. パラメータ bによるセルトランジスタ vth 分布の分離

合わせずれパラメータ b を含めたチップトランジスタ Vth は、式(9)(10)(11)より求めることができる。

$$d1(cr,b) = \int_0^\infty v \operatorname{th}(x) \cdot g(x - cr + b) dx \tag{9}$$

$$d2(cr,b) = \int_0^\infty v \operatorname{th}(x) \cdot g(x - cr - b) dx$$

(10)

$$Vth(cr, b) = (d1(cr) + d2(cr))/2 d(x_0) \cdot v_{th 0}$$

(11)

#### 4-3-4. 製造パラメータ感度解析

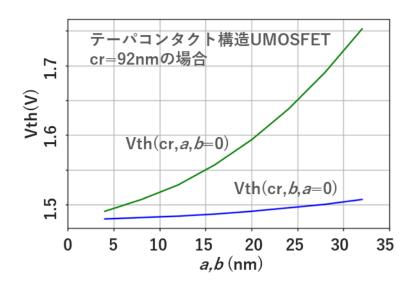

テーパコンタクト構造 UMOSFET (cr=92nm) において、開口寸法広がりパラメータ a とゲート・コンタクト合わせずれパラメータ b に対するチップトランジスタ Vth の感度解析を行った結果を図 4-3-15.に示した。a,b の実測最大値は、それぞれ 24nm,12nm であった。この範囲内では開口寸法広がりの影響が大きく、合わせずれによるチップトランジスタの Vth 影響は殆どない結果となった。合わせずれは Vth よりオン抵抗に大きな影響が出るものと考えられる。

図 4-3-15. チップトランジスタ Vth に対するパラメータ a,b の感度

### 4-3-5. モデル検証

前節では、トレンチコンタクト側壁からの P+拡散層を除くゲート・コンタクト距離 (cr) が 80nm より小さくなるとゲート空乏層が閾値電圧より低い電圧で P+拡散層にパンチスルーを起こすため Vth 上昇が起こることを示した。また加工バラツキや露光装置の開口寸法広がり、ゲート・コンタクトパターンの合わせずれを考慮したチップトランジスタの Vth 計算方法を提案した。このモデルの検証に図 4-2-1.に示したテーパコンタクト構造 UMOSFET を使用する。テーパコンタクト構造 UMOSFET は露光装置のショットパターンと同じ周期性を持った Vth 分布を示し、Vth バラツキについてはパターン設計では同じゲート・コンタクト距離 (crl=150nm) を持つ垂直コンタクト構造 UMOSFET に比べ標準偏差で 1.5 倍大きなバラツキを持っている。モデル検証にあたりトレンチコンタクト構造 UMOSFET のショット内チップトランジスタの Vth 分布を検証することにした。図 4-3-16.にウェハ面内で検証に採用したショット領域とその領域で実測した開口寸法広がりの等高線 MAPを示した。

露光装置の開口広がりは複数枚のレンズ収差によって起こる。黄緑色の領域で Vth が大きく青色領域では Vth が小さい。ショット面積は 20mmx20mm で、X,Y 方向に 23 個 x10 個合計 230 個のチップトランジスタが含まれている。ショット内チップトランジスタ Vth を開口寸法パラメータ(a)を考慮して計算したものと実測したチップトランジスタ Vth を比較する。

図 4-3-16. 検証に用いたショットエリアと開口寸法広がりの等高線図

まず、ショット内で実際に測定した 230 個のチップトラジスタ Vth の平均値と標準偏差は、1.61V、51mV であったのに対して、上記計算で求めた Vth 平均値と標準偏差は、1.54V、46mV であった。計算の平均値は実測値に対し略同じ分布が得られた。実測と計算によるシ

ョット内分布をカラー濃淡図で図 4-3-17.に示した。

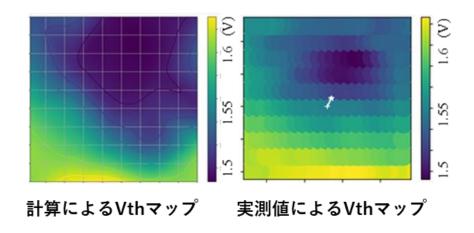

図 4-3-17. ショット内 Vth 計算値と実測値の分布マップ

ショットの左下部でVth が高く中央部やや右上でVth が低い領域が再現されている。実測値マップに白線で加えたベクトルはゲート・コンタクトパターンのX,Y 方向の合わせずれを示しておりY方向シフト量(b) はAnm であった。合わせずれのVth 影響は無視できるレベルであったことも付け加えておく。

#### 4-4. 微細化による Vth 制御性の課題

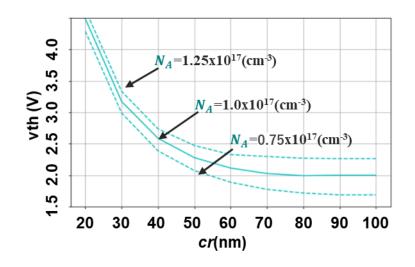

cr>80nm の場合 Vth は式(2)で表されベース濃度 NA とゲート酸化膜厚(Tox)が主要パラメータである。ゲート酸化膜厚はゲート耐圧を確保するため製造工程で膜厚を都度変えて Vth をコントロールすることはない。通常はベース濃度 NA をベースイオン注入のドーズ量を使ってコントロールすることが一般に行われる。しかし cr が小さくなりゲート空乏層がコンタクト P+拡散層にパンチスルーする (cr<80nm) 場合、図 4-3-3.に示したように Vthは cr に大きく依存する。工程バラツキを入れないシンプルなモデル(バラツキがないモデル)で、ベース濃度 NA と cr をパラメータとした vth の計算結果を図 4-4-1.に示した。

図 4-4-1. vth のベース濃度(NA)と cr 依存性

図 4-4-1.で  $\operatorname{cr}$  が  $\operatorname{80nm}$  以上では、 $\operatorname{vth}$  の  $\operatorname{cr}$  依存性はなくベース濃度(NA)だけでコントロールできる。 $\operatorname{cr}$  が  $\operatorname{80nm}$  より小さくなると  $\operatorname{cr}$  依存性が大きくなる。更に小さくなるとベース濃度 (NA) による  $\operatorname{vth}$  コントロールが効かなくなる。

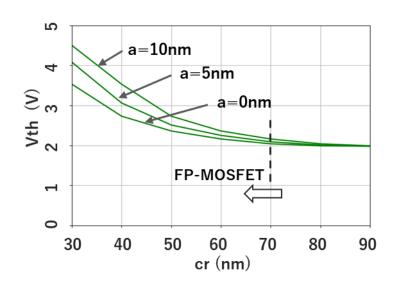

最近の Field Plate 構造の UMOSFET は、セルサイズが 1.0um 以下でゲート・コンタクト距離 (crl) が 100nm 程度となっている。垂直コンタクト形状でコンタクト側壁からの P+拡散層 30nm として cr は 70nm である。図 4-4-2.に FP-MOSFET セルの断面構造を示す。 FP-MOSFET のチップ Vth 計算前提として、加工バラツキは従来と同じく標準偏差 13.3nm として露光装置による寸法変化差は実験で使用した装置より改善されるとして開口寸法広がりパラメータ(a)を、0,5,10nm として Vth 計算した結果を図 4-4-3.に示した。ベース濃度 (NA) は 1e17(cm-3)、ゲート酸化膜厚は 50nm で一定としている。

図 4-4-2. FP-MOSFET のセル断面構造

図 4-4-3. FP-MOSFET チップ Vth の開口寸法広がり (a) 依存性

セル構造の微細化により P+拡散層を除いたゲート・コンタクト距離(cr)が 70nm 以下となる場合は露光装置のパターン変換差を厳しくコントロールしなければならない。また、ドライエッチャ等の加工寸法バラツキの改善も必要である。パワー半導体の生産ラインは200mm ラインが主流ではある。寸法変換差や合わせずれ精度は最小寸法の 1/10 が一般的である。精度は10~20nm 程度であり、最小露光寸法130nm が微細パワー半導体を律速する要因というよりも寸法変換差や合わせずれ精度が量産設計での限界になると考えられる。

#### 4-5. まとめ

セルサイズの微細化が進む UMOSFET をモチーフに複数の加工装置のバラツキ影響を受けるゲート・コンタクト距離 (crl) に着目して微細 UMOSFET の Vth 上昇現象を解明した。一般的には crl による Vth 上昇は crl<30nm でコンタクト P+拡散層によるチャネル濃度上昇が原因と考えられていたが、実際には crl<150nm で Vth の上昇が観察された。この現象はゲート空乏層が P+拡散層にパンチスルーを起こすモデルで説明することができた。実際の工程バラツキである crl 寸法の加工バラツキ (o=13.3nm) と露光装置の寸法広がり(a)、ゲートとコンタクトのパターンずれ(b)を考慮した Vth モデルを作成した。この拡張モデルで露光装置のショット内で顕著な Vth バラツキを再現検証することができた。このモデルを更に微細な UMOSFET に適用すると、従来の Vth の制御パラメータであるベースインプラドーズ量による制御が効かなくなり crl の影響が大きくなりことを示した。crl が Vth の主要パラメータになるため製造装置バラツキを大幅に改善する必要があることを示した。

露光装置の線幅均一性(広がり:a)はデザインルールの 1/10 が目安である[59]。例えば UMOSFET のコンタクト幅 0.2um パターンに対しては最大で 20nm 程度となる。またパターンの合わせずれ(b)はデザインルール 0.13um では最大で 13nm 程度である[58]。今回 の実測最大値は a=24nm、b=12nm であり 200mm 製造ラインとしては標準的である。将来 の微細 UMOSFET は a,b ともに nm オーダーの制御が必要だと思われる。300mm ラインの装置はデザインルール的には現状ではオーバースペックであるが nm オーダーのバラツキ制御の観点からは必要になると思われる。

## 第5章 微細化による工程欠陥の影響

# 5-1. 工程欠陥と不良モード

# 5-1-1. パワー半導体の不良モード

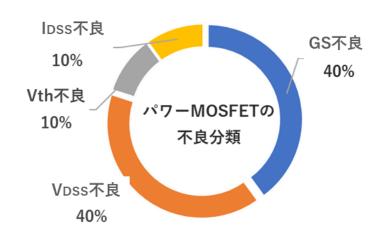

一般的なパワーMOSFET のウェハテストでの不良項目とその比率を図 5·1·1.に示す。GS 不良はゲートとソースのショートモード不良で工程欠陥が主要因である。VDSS 不良は接合耐圧が定格耐圧に満たない不良である。接合終端部構造やセル部構造の寸法バラツキによるものと Si バルク結晶欠陥に起因するものが含まれる。Vth 不良は製品の Vth 規格を外れる不良で製造バラツキの影響を受ける。IDSS 不良は欠陥による接合リークやセルトランジスタのチャネルリークに起因することが知られている[60][61]。

図 5-1-1. パワーMOSFET のウェハテスト不良項目

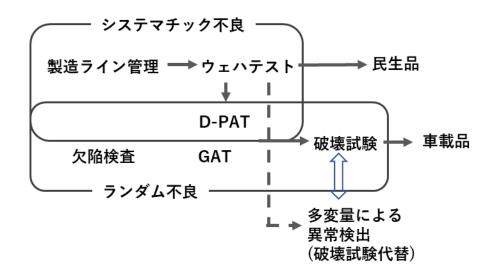

不良モードは、特性値が外れるシステマチック不良と欠陥の影響によるランダム不良に大別される。パワーMOSFET の場合は Vth 不良と VDSS 不良はシステマチック不良で寸法・膜厚、拡散長等のプロセスパラメータに依存する。GS 不良と IDSS 不良 (VDSS 不良が含まれる場合もある) はランダム不良であり工程欠陥 (工程ダスト) や結晶欠陥に依存する [62][63]。Vth に代表されるシステマチック不良は、第4章で説明したように工程感度を分析し影響の大きいパラメータのバラツキを抑えることで低減が可能である。一方、GS 不良のようなランダム不良の管理には欠陥検査装置が使用される。欠陥の多いウェハはウェハテストで電気的不良と判断される前にウェハ単位で欠陥数を測定し管理規格より多ければ工程途中で破棄される。更に車載製品の場合はウェハ単位の欠陥数が管理規格内であって

も周辺チップが不良の場合や特性値が規格値内であってもウェハ内で分布外れのチップは 不良として取り除かれる[64][65]。また自動車市場で不良が発生した場合には関連するロット、ウェハ、チップの製造工程履歴が必要で欠陥位置とサイズだけではなく欠陥画像を保存 する場合もある。車載製品については欠陥検査工程負荷が民生品に比べ非常に大きい。従っ て不良モードに対して管理すべき欠陥検査工程を絞り込むことは非常に重要である。

パワーMOSFET の場合は過去の不良解析から致命的な欠陥を発生させる加工工程は凡そ推定されている。GS 不良はゲートポリシリコン加工後の欠陥に強い相関があることが知られている[66]。 車載製品ではパワー半導体の実使用環境を模した L 負荷スイッチング試験がウェハテスト項目に追加される(図 5-1-1.の不良分類に L 負荷不良は含まれていないが)。この場合はコンタクト P+インプラのインプラ遮蔽欠陥がアバランシェ耐量不足やチップ破壊に結び付くことが知られている[67]。

#### 5-1-2. 欠陥の種類と不良モード

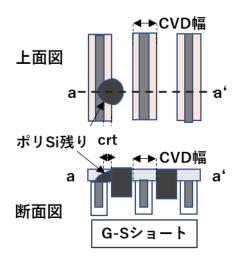

GS 不良モードを起こす典型的な欠陥を図 5-1-2.に示す。一般的にトレンチゲートは、トレンチ形成  $\to$  ゲート酸化  $\to$  ポリシリコンデポジション  $\to$  ゲートポリエッチチングで形成される。GS 不良はポリ Si 残りやポリ Si ダストがゲートとコンタクトをショートさせることにより発生する場合が多い。GS 不良と相関の強い欠陥検査はゲートポリシリコン加工後に行われる。

ポリシリコン欠陥のサイズが、ゲート・コンタクト距離(crl)にゲート酸化膜厚(Tox)を加えた距離(crt)より大きい場合は GS ショートを起こす要因となる。ゲート上の絶縁膜(CVD 膜)幅より大きい欠陥サイズになるとポリシリコンとソースコンタクトはショートするため GS 不良率 100%となる。微細化によりゲート・コンタクト距離(crl)や CVD 幅が減少すると GS 不良率は増加する。GS 不良の模式図を図 5-1-3.に示す。

ポリSi残り ポリSiダスト

図 5-1-2. GS 不良の原因となるポリシリコン欠陥

図 5-1-3. ポリシリコン欠陥による GS 不良の模式図

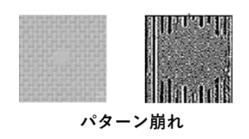

次に L 負荷スイッチング試験破壊耐量不良と関連性が強いパターン崩れ欠陥を図 5-1-4. に示す。パターン崩れはパターン形成や加工を妨げる遮蔽欠陥により発生する。

図 5-1-4. パターン崩れ

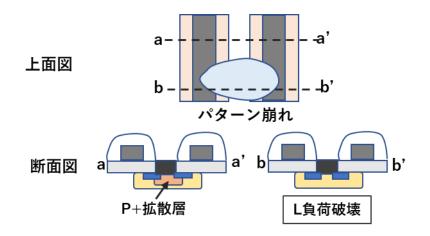

L 負荷スイッチング試験で破壊するチップには部分的にベース抵抗が高いセルトランジスタが存在しそのセルトランジスタに電流が集中し破壊すると考えられる。実際に L 負荷試験後の微小な破壊痕はアクティブ領域にランダムに発生している[68]。セルトランジスタベース抵抗上昇はコンタクト領域への追加 P+インプラを遮蔽する欠陥がある場合に起こる。図 5-1-5.に P+遮蔽欠陥による L 負荷耐量不良の模式図を示した。上面図の a-a'断面は正常な P+コンタクトが得られているが、遮蔽部 b-b'の断面ではベースと接触する P+拡散層が形成されていない。

図 5-1-5. P+遮蔽欠陥による L 負荷破壊耐量不良の模式図

次節では、これらの欠陥が歩留や特性にどのように影響するのかをモデルにより解析する。

## 5-2. ゲート不良のモデル化

2000 年にシステム LSI の歩留を設計パターン修正により改善するビジネスが出現した。 その手法は多層配線の配線パターンからランダム欠陥に敏感な領域(クリティカルエリア) を検出しパターン幅や形状を修正する手法であった。現在では外部リソースに頼らず光学 シミュレータによりクリティカルなホットスポット検出やパターンの光学補正 (OPC:Optical Pattern Collection)は設計初期段階で行われる[59]。本章では構造が単純でセルトランジスタパターンが周期的に配置されているパワー半導体にクリティカルエリアの概念を適用しセル微細化による欠陥影響のモデル化を行った。

UMOSFET や IGBT のセルパターンは基本的にゲートパターンとコンタクトパターンは ライン&スペース構造でゲートラインとコンタクトラインは平行に配置されている。

第4章では、UMOSFET のセル微細化に伴うゲート・コンタクト距離(crl)縮小は Vth 上昇を招き Vt hバラツキを増加させることを説明した。本章では第4章と同じパラメータであるゲート・コンタクト距離(crl)縮小により起こる GS 不良の増加と L 負荷耐量不良をクリティカルエリアモデルを使って予測した。

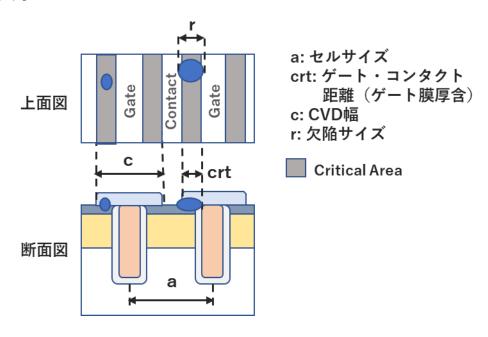

#### 5-2-1. ゲート不良のクリティカルエリアモデル

ゲートトレンチとコンタクトが平行な一般的な UMOSFET セル部の上面図と断面図を図 5-2-1.に示す。セルサイズと CVD 幅をそれぞれ a と c、欠陥サイズ(直径)をr とする。 欠陥はゲート材料であるポリシリコンの通電性を仮定している。上面図で灰色に着色した部分がクリティカルエリアでありこの領域の絶縁性が絶たれると GS 不良が起こる。ソース

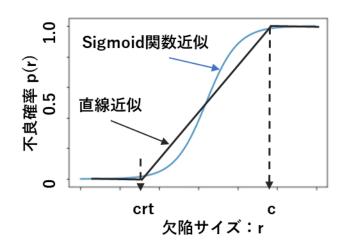

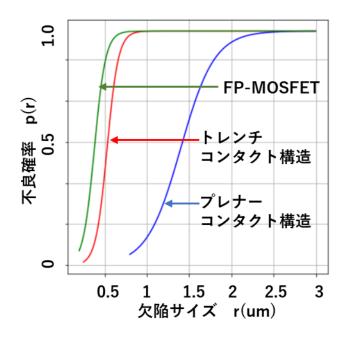

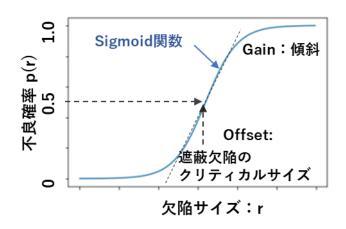

パターンとゲートパターンの絶縁距離(crl)にゲート膜厚を加えた距離 (crt) より小さい欠陥は不良を起こさないが crt をこえると( $\mathbf{r}$ >crt)不良が発生する更に欠陥が CVD 幅 c を超えると( $\mathbf{r}$ >c)ゲート・ソースが必ずショートする。欠陥サイズ( $\mathbf{r}$ )による不良確率( $\mathbf{p}$ ( $\mathbf{r}$ ))を図 5-2-2.に示す。

図 5-2-1. UMOSFET のクリティカルエリア

図 5-2-2. 欠陥サイズと不良確率

歩留計算は確率関数を使って計算するが、場合分けが必要な直線近似を使用せず連続関数である Sigmoid 関数を使用した。図 5-2-2.に直線近似と Sigmoid 近似を示した。欠陥サイズ $\mathbf{r}$ と不良確率  $\mathbf{p}(\mathbf{r})$ は、式(12)の Sigmoid 関数で表現する。

$$p(r) = \frac{1}{1 + \exp(-\alpha r + \beta)} \tag{12}$$

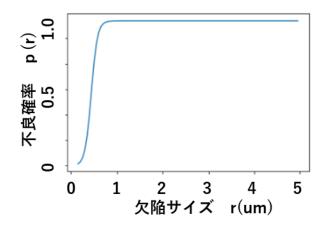

式(12)で、 $\alpha$  はゲインで傾斜を表す、 $\beta$  で X 軸のオフセットを調整するパラメータである。 図 5-2-3.に crt=0.25um のトレンチコンタクト構造 UMOSFET を想定にした確率カーブ  $p(\mathbf{r})$ を示した。計算には  $\alpha$ =15、 $\beta$ =0.44 を使用した。

図 5-2-3. 不良確率関数 p(r)

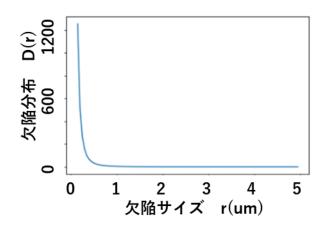

$A_0$  はチップ全体のクリティカルエリア面積でありチップ面積にセル領域のクリティカルエリア比率とチップのアクティブ領域 (FET) 領域比率(80%を仮定)を掛けて求める。計算でのチップサイズは2mm とした。欠陥サイズ $\mathbf{r}$  に依存したクリティカルエリアを $\mathbf{A}(\mathbf{r})$ = $\mathbf{A}_0$ ・ $\mathbf{p}(\mathbf{r})$ とした。欠陥分布  $\mathbf{D}(\mathbf{r})$ については、欠陥数が欠陥サイズ  $\mathbf{r}$  に対してガンマ関数( $\mathbf{B}$ = $\mathbf{0}$ )や逆 3 乗に比例することが経験的に知られていることから逆 3 乗を採用して式( $\mathbf{13}$ )のように仮定した[ $\mathbf{71}$ ]。図  $\mathbf{5}$ - $\mathbf{2}$ - $\mathbf{4}$ -に欠陥サイズと欠陥分布を示す。

$$D(r) = d_0/r^3 \tag{13}$$

図 5-2-4. 欠陥分布 D(r)

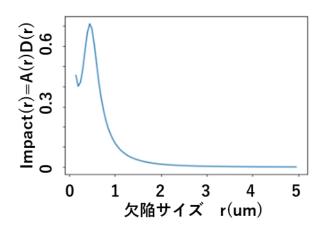

do は欠陥サイズ 1um の欠陥密度である。計算では欠陥検査装置で検出される。計算では 1um 以上の欠陥数がウェハ全面に 300 個ある場合(約 1 個/cm²)を想定している。 歩留に影響ある欠陥サイズ分布を表す Yield Impact を式(14)で計算する。

また歩留は式(15)に示すように Yield Impact を積分することで求められる。図 5-2-5.に欠陥サイズ  $\mathbf{r}$  と Yield Impact を示した。 $\mathbf{r}$ =0.6 $\mathbf{u}$ m 付近の欠陥が歩留への影響が大きいことが判った。

$$\operatorname{Im} pact(r) = A(r) \cdot D(r) \tag{14}$$

$$Yield = Y_0 \cdot \exp\left\{-\int_{r_0}^{\infty} \operatorname{Im} pact(r) \, dr\right\}$$

(15)

図 5-2-5. 欠陥サイズと歩留影響

チップ面積を 4mm² として式(15)により求めた歩留は 81.3%となる。ここでは UMOSFET のクリティカルエリアモデルから歩留を計算する手順を示した。次に実際のセル構造と製造ラインの欠陥密度を用いて歩留計算を行う。

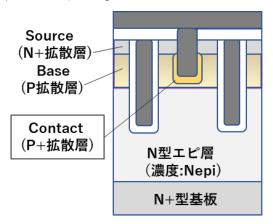

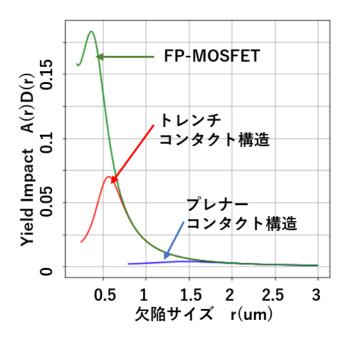

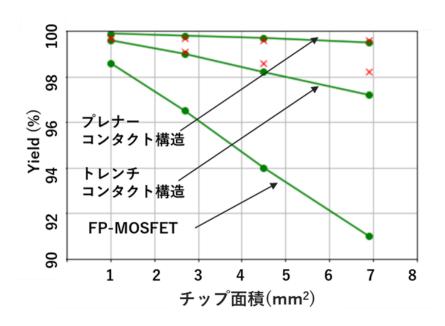

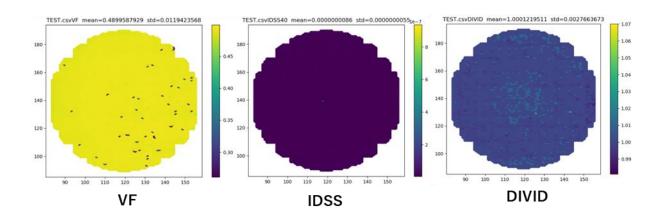

# 5-2-2. セル微細化とゲート歩留

微細化と GS 歩留の関係を把握するために第 4 章の Vth 計算し使用したプレナーコンタクト構造 UMOSFET とトレンチコンタクト構造 UMOSFET についてチップサイズ依存性を実データと比較した。また更に微細な FP-MOSFET 構造についてもチップサイズ依存性の歩留予測を実施した。比較した 3 構造のセル上面図を図 5-2-6.に示した。

図 5-2-6. 微細化とクリティカルエリアの変化

図 5-2-7.に上記 3 構造についての欠陥サイズと不良確率を示した。プレナーコンタクト構造に比ベトレンチコンタクト構造は小さい欠陥に敏感になっている。図 5-2-8.に Yield Impact を示したが、プレナーコンタクト構造が 1.5um 付近の欠陥影響を最も受けるのに対し、トレンチコンタクト構造で 0.6um、FP-MOSFET で 0.4um と微細欠陥の影響を受け易くなっていることが判った。

図 5-2-7. 3 構造の欠陥サイズと不良確率

図 5-2-8. 3 構造の Yield Impact

ポリシリコンエッチング後のウェハ欠陥検査では、欠陥サイズ 1.0um 以上の個数が 50 個/Wafer (Wafer 面積=176cm²:欠陥密度 D=0.28/cm²) を設定、チップサイズが  $1\sim7$ mm²の 各構造での歩留を計算した結果と欠陥レベルが同程度のラインで製造されたプレナーコンタクト構造とトレンチコンタクト構造の実歩留を図 5-2-9.に示した。

図 5-2-9. 3 構造の予測 Yield と実測値の比較

図 5-2-9.で赤色の×印が実測値である。旧式ラインと設備で製造するプレナーコンタクト構造 UMOSFET とトレンチコンタクト構造 UMOSFET は予測値と良い一致を示した。更に微細な構造を持つ FP-MOSFET では欠陥の影響を予測するとチップ面積依存性が大きく歩留低下も大きい。 FP-MOSFET 生産には旧式ラインではなく欠陥数がより小さい製造ラインが必要であることが判った。また、チップ面積が大きくなると実測不良率と計算不良率に乖離が発生する場合がある。原因のひとつにウェハ面内の欠陥の偏在が考えられる。次節で説明する。

# 5-2-3. 偏在欠陥による歩留のチップ面積依存性

ランダム欠陥による歩留 $Y_{random}$ はセル構造が同じ場合は欠陥密度 Dとチップ面積 A を使って式(16)で表される。

$$Y_{random} = \exp\left(-D \cdot A\right) \tag{16}$$

しかし式(16)が成り立つのは、欠陥がランダムに分布していることが前提である。面積依存性が式(16)に示すポアソン分布に従わない場合がある。欠陥がウェハ面内で偏在している場合は注意が必要である。特にチップサイズが大きくなると歩留予測モデルから外れる可能性が大きくなる。

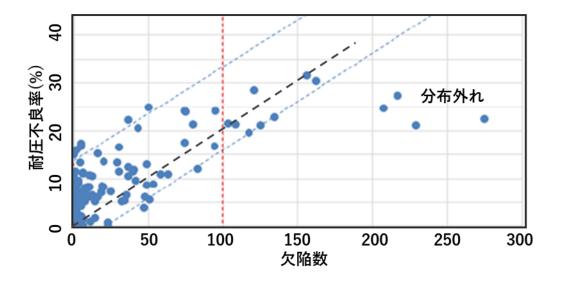

工程投入前の材料結晶欠陥と工程終了後のデバイス耐圧不良の関係を図 5-2-9.に示した。欠陥数と不良については式(16)から不良率 F を近似でして式(17)のようになる。欠陥数と耐圧不良は欠陥密度 D を傾斜とする原点を通る直線になるが、実際には分布外れが存在する。欠陥密度 D はウェハの総欠陥数をウェハ面積で割り単位面積当たりの欠陥数に変換したものでありウェハ面内で均一に欠陥が存在することを前提にしている。図 5-2-10.の分布外れは欠陥分布の偏在により生じたと考えられる。

$$F(D) = 1 - Y_{random} = 1 - (1 - DA) = D \cdot A \tag{17}$$

図 5-2-10. 結晶欠陥数と素子耐圧不良率

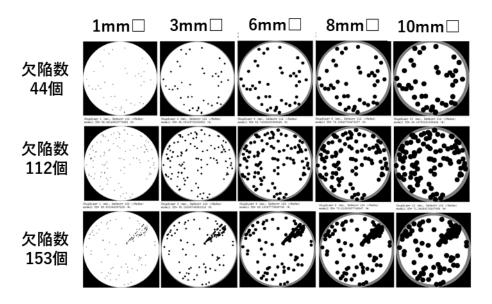

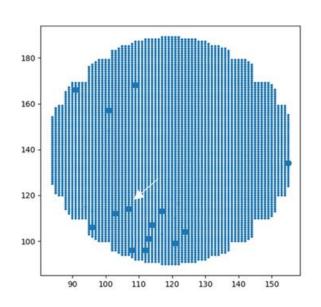

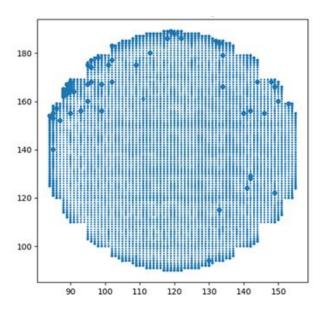

ウェハ面内の欠陥位置から欠陥が偏在している場合にも有効な不良率計算方法を提示する。計算方法はシンプルで欠陥位置座標を中心にチップサイズを反映した円を着色し重なりあう部分が多い場所は欠陥が集中(偏在)するが逆に集中してない領域は良品が多いためウェハ全体では不良率が低下することを着色部面積比率で表せる。これはオーバーラップした着色面積を求めることで計算することができる。Pythonの画像処理ライブラリ(PIL)を使用して不良領域チップ面積を反映した黒丸で重ね書きものを図 5-2-11.に示した。また、図 5-2-11.の灰色で示した同心円周辺(エッジ部)のは無効領域として面積から除外した。検証に使用した3枚のウェハの欠陥数は、44,112,158個である。欠陥がウェハ内でランダムに分布する場合この順番で不良率が増加することになるが、本計算ではチップサイズが大きくなると44,158,112個の順番と逆転する結果となった。欠陥数 158 個のウェハが逆転したのは欠陥偏在によると考えられる。

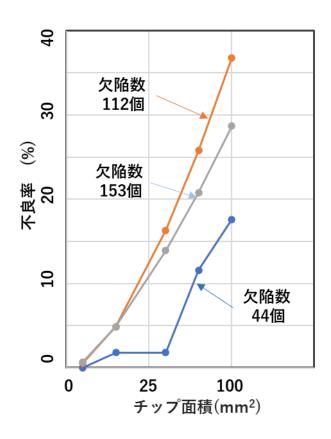

図 5-2-11.に上記 3 枚のウェハの欠陥位置情報を基にチップサイズ 1,3,6,8,10mm□を想定した場合の不良領域(黒色着色部:矩形を円に変換)比率を計算した。また図 5-2-12.にチップ面積と不良率を 3 枚のウェハについて示した。チップサイズが 6mm□以上では欠陥数 112個と欠陥数 153個では欠陥が偏在する欠陥数 153個の方の不良率が少ない結果となった。また欠陥数 44個のウェハの不良数増加は連続的ではなく 8mm□を超えると 10%近く不良が増加することが判った。欠陥が偏在しチップサイズが大きい場合は式(17)に従わなくなることに注意が必要である。欠陥検査装置からのウェハ欠陥数のみでの管理は歩留と結びつかない場合があることを示した。

図 5-2-11. 結晶欠陥分布とチップ面積による不良率計算

図 5-2-12. チップ面積による不良率の変化

# 5-3. L負荷破壊と欠陥サイズ

# 5-3-1. P+インプラ遮蔽欠陥によるベース抵抗上昇モデル

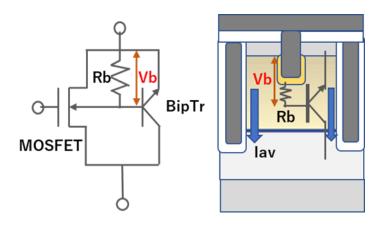

セルトランジスタの等価回路を図 5-3-1.に示す。セルトランジスタは MOSFET に寄生バイポーラトランジスタが並列に接続されている。またソース電極とベース (バックゲート) はベース抵抗 Rb を介して接続されている。L 負荷スイッチ試験等でドレインに大電流が流れるとベース抵抗 Rb に電位差が生じエミッタとベースのビルトインポテンシャル(約 0.6V) を超えると寄生バイポーラトランジスタが動作しセルトランジスタに電流が集中する[71]。

図 5-3-1. セルトランジスタの等価回路

L 負荷試験耐量の指標としてアバランシェ電流 Iav が使われる。粗い近似では Iav と Rb は定数を介して逆比例すると考えられる[73]。

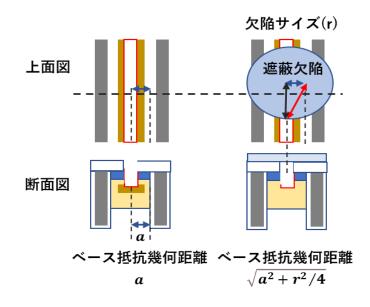

ベース抵抗 Rb はコンタクト P+の追加インプラを遮蔽する欠陥サイズ r の欠陥影響により P+から遮蔽されたベース領域までの幾何距離が増加し部分的にベース電位が上昇を起こす と考えられる。図 5-3-2.に P+インプラ遮蔽欠陥有無の上面図と断面図を示した。また上記 ベース抵抗幾何距離を図示した。欠陥がない正常な場合は、コンタクト底部に P+インプラ が注入されコンタクト底部中央からチャネル界面までの距離 (a) がベース抵抗の幾何距離 となる。一方で欠陥サイズ(r)の遮蔽欠陥コンタクト領域を遮蔽されたセルトランジスタの ベース抵抗は遮蔽されてない P+領域からチャネル界面までの距離 $\sqrt{a^2+r^2/4}$  で表現される。

図 5-3-2. P+インプラ遮蔽欠陥とベース抵抗幾何距離

# 5-3-2. 欠陥サイズとセルトランジスタの耐量低下率

チップ破壊耐量の指標であるアバランシェ電流 Iav は、概近似ではセルトランジスタのベース抵抗に逆比例すると考えられる。セルトランジスタのベース抵抗については、ベースドーズ Qd、ホール易動度  $\mu p$ 、チャネル幅 w とベース幾何距離を使って表され欠陥がない場合のベース抵抗  $R_0$  は式(18)のように表される。

$$R_0 = \frac{a}{qQ_d \mu_p w} \tag{18}$$

また、サイズ r の P+インプラ遮蔽欠陥がある場合のセルトランジスタのベース抵抗 R(r)は欠陥がない場合との幾何距離比を使って式(19)で表される。

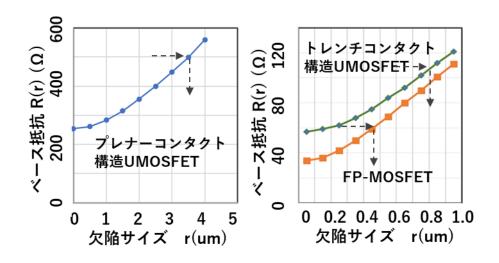

$$R(r) = R_0 \left\{ 1 + \left(\frac{r}{2a}\right)^2 \right\} \tag{19}$$

Qd=1e13(cm<sup>-2</sup>)、 $\mu$ p=200(cm<sup>2</sup>/Vs)、w=0.6(um)として、図 5-2-5.に示した微細化レベルの異なる 3 構造(プレナーコンタクト構造、トレンチコンタクト構造、FP-MOSFET)について欠陥影響を考慮したベース抵抗  $R(\mathbf{r})$ を計算した。結果を図 5-3-3.に示した。欠陥がない状態のベース抵抗  $R_0$  は欠陥サイズ  $\mathbf{r}$ =0 の値であり、プレナーコンタクト構造、トレンチコンタクト構造、FP-MOSFET 構造でそれぞれ 254,57,34( $\Omega$ )となった。 Iav と Rb が逆比例すると考えると微細化によりアバランシェ耐量 Iav は上昇することになる。微細化により破壊耐量(Iav)の絶対値は上がるが、チップトランジスタ破壊はチップ内の部分的なセルトランジスタの電流集中で起こることを考えると微細化により L 負荷不良率は欠陥の影響で増加すると考えられる。上杉によると 1.4 倍のベース抵抗差でベース抵抗の大きいMOSFET への電流集中が再現されたと報告されている[72]。

図 5-3-3. P+遮蔽欠陥サイズとベース抵抗(計算)

ここでは欠陥によりセルトランジスタのベース抵抗が 2 倍になる欠陥サイズをクリティカルサイズと仮定し図 5-3-3.から抽出した。上記 3 構造でそれぞれ 3.45,0.82,0.48(um)が得られた。欠陥のクリティカルサイズを不良確率=0.5 (Sigmoid 関数のセンター値)として、Sigmoid 関数の立上りをトレンチコンタクト構造の GS 不良モデルで使用した値 (Gain=15)を使用し遮蔽欠陥のクリティカルモデルに応用した。(図 5-3-4.)

図 5-3-4. P+遮蔽欠陥サイズと破壊不良確率のモデル

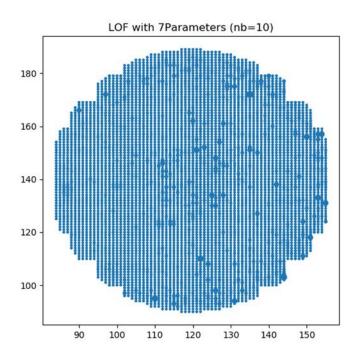

## 5-3-3. ゲート不良/L 負荷不良の欠陥密度とチップサイズ依存性

ランダム不良は発生源側では欠陥個数とサイズ、設計側では設計ルールとチップサイズに依存する。パワーMOSFETの代表的なランダム不良として、ゲートポリシリコン欠陥による GS 不良(5・2・2.)と材料結晶欠陥による耐圧不良(5・2・3.)それと P+遮蔽欠陥による L 負荷破壊不良(5・3・2.)を説明した。製造ラインでは主要プロセスに欠陥検査を導入し欠陥個数による管理が行われている。実際は歩留ロスを管理する基準にするのではなく加工装置の異常管理が主目的であるためデザインルールやチップサイズには無関係な管理値が設定される場合が多い。しかし、微細新製品をそのラインで流した場合に発生するランダム不良率を予測できないと低歩留で採算性のない製品を生み出すことになりかねない。特に微細化が進むパワー半導体ではラインや装置の実力を把握し歩留を予測・設計することが重要である。ランダム欠陥密度(場)とチップサイズ(設計)から不良率を予測するモデルをコスト設計に役立てるため結果を可視化した。

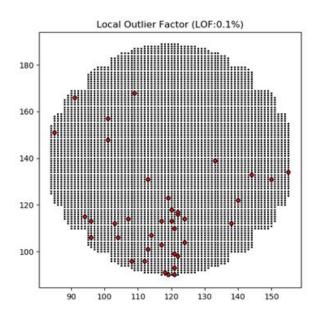

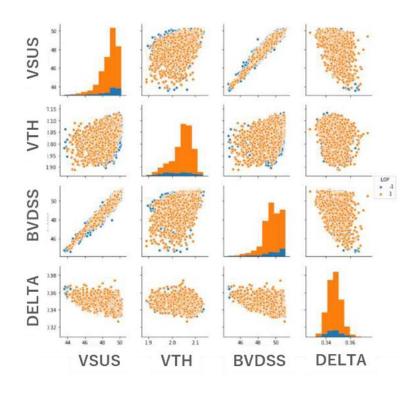

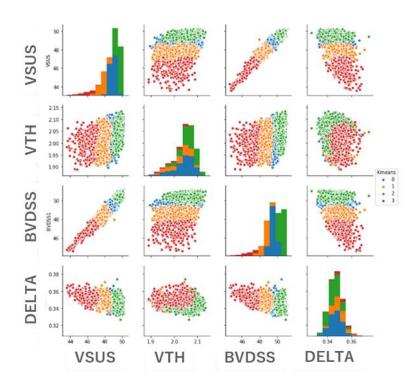

入力を欠陥密度(D)とチップ面積 (A)、出力を 3 構造の GS 不良率と L 負荷耐量不良率を同一の平行線で表示した[73]。図 5-3-5.に欠陥密度 D を  $0\sim0.32$  個/cm² (1um 以上)、チップ面積を  $0\sim0.1$ cm² に変化させた場合に、セル微細度の異なる 3 構造についてゲート・ソース不良率 (GS 不良) と L 負荷耐量不良率 (LS 不良) を示した。

図 5-3-5. 欠陥密度とチップ面積による不良予測モデルの可視化

プレナーコンタクト構造では欠陥密度  $0.32(lcm^2)$ 、チップ面積 0.1(cm2)の範囲では、GS 不良、LS 不良ともに 1%以下であるが、トレンチコンタクト構造では 5%のレベルに、FP-MOSFET では 10%を超えることが予測された。平行線図は Python の plotly ライブラリを使用しておりインタラクティブな操作が可能である[74][75]。出力パラメータの範囲を操作

することで入力パラメータの範囲を表示させることが可能である。この機能を使ってトレンチコンタクト構造の GS 不良と LS 不良を 1%以下に抑えるための欠陥密度とチップサイズを求めたものを図 5-3-6.に示す。

図 5-3-6. トレンチコンタクト構造の欠陥密度とチップサイズ制限

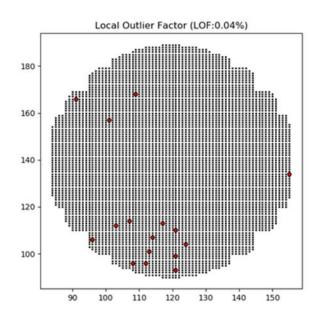

トレンチコンタクト構造で GS 不良と LS 不良を 1%以下に抑えるためには、チップ面積は  $0.06cm2(2.4mm\Box)$ 以下のサイズに制限される。その場合、欠陥密度を 0.03 個/cm² 以下に管理された製造ラインが必要である。同じように FP-MOSFET の場合を図 5-3-7.に示す。

図 5-3-7. FP-MOSFET 構造の欠陥密度とチップサイズ制限

FP-MOSFET 構造で GS 不良と LS 不良を 1%以下に抑えるためには更に制限がかかり標準的な  $2\sim3$ mm $\Box$  チップサイズ  $(0.04\sim0.09$ cm $^{-2})$  では図 5-3-7.の範囲に解が見つからない。

# 5-4. 微細化パラメータによるユニバーサルモデル生成

図 5-4-1.に示すコンタクト側壁 P+拡散層を除くゲート・コンタクト距離 cr と露光装置の 寸法変換差/合わせずれ dcr (delta-cr) を微細化パラメータとした。側壁 P+拡散 30nm と ゲート酸化膜厚 50nm は定数とした。また、ランダム欠陥による不良率計算の前提として UMOSFET 標準サイズのチップ面積 0.1(cm²)を採用した。またサイズが 1um 以上の欠陥 密度 DD (Defect Density) を場のパラメータとした。

図 5-4-1. 微細化パラメータ

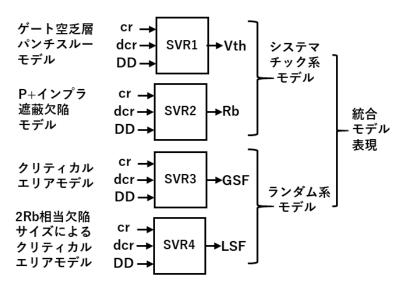

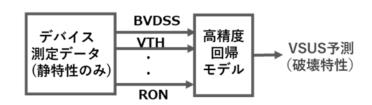

図 5-4-2.に 3 つの微細化パラメータ(cr,dcr,DD)を説明変数とし、4 つの目的関数 (Vth,Rb,GSF,LSF)を求めるベースモデルと更に共通説明変数で各モデルを数値的に結合 するための回帰モデルを示した。回帰に使用したモデルは非線形に対応する SVR (Support Vector Regression)を使用した[77]。最終的に動的平行線図に 3 説明変数と 4 目的関数の 7 項目を結合し表示した。

図 5-4-2. 微細化パラメータと結合モデル

回帰を行うための各ベースモデルから抽出した計算結果を表 5-4-1.に示した。微細化パラメータの設定は cr<100nm とし dcr<16nm と次世代構造を予測できるレベルに設定した。また欠陥密度はチップ面積=0.1  $(cm^2)$  としていることから DD<0.007  $(/cm^2)$  とした。

| 表 5-4-1. | 回帰用デー | タ構造 |

|----------|-------|-----|

|----------|-------|-----|

| 欠陥 (x1e-3/cm2) | cr (nm) | Δcr(nm) | Vth(V) | Rb(Ω) | GS不良(%) | LS不良(%) |

|----------------|---------|---------|--------|-------|---------|---------|

| 1              | 30      | 0       | 3.53   | 15    | 1.74    | 1.49    |

| 1              | 30      | 5       | 4.11   | 17.5  | 1.77    | 1.47    |

| 1              | 30      | 10      | 4.52   | 20    | 1.79    | 1.44    |

| 1              | 50      | 0       | 2.34   | 25    | 1.62    | 1.39    |

| 1              | 50      | 5       | 2.53   | 27.5  | 1.65    | 1.37    |

| 1              | 50      | 10      | 2.74   | 30    | 1.67    | 1.34    |

| 1              | 70      | 0       | 2.05   | 35    | 1.45    | 1.28    |

| 1              | 70      | 5       | 2.1    | 37.5  | 1.49    | 1.24    |

| 1              | 70      | 10      | 2.18   | 40    | 1.54    | 1.2     |

| 2.5            | 30      | 0       | 3.53   | 15    | 4.38    | 3.74    |

| 2.5            | 30      | 5       | 4.11   | 17.5  | 4.44    | 3.69    |

| 4              | 70      | 10      | 2.18   | 40    | 6.01    | 4.71    |

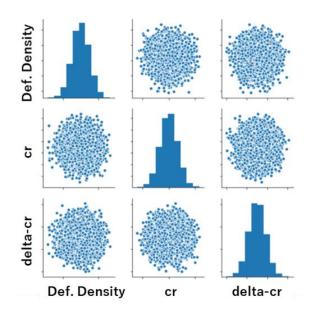

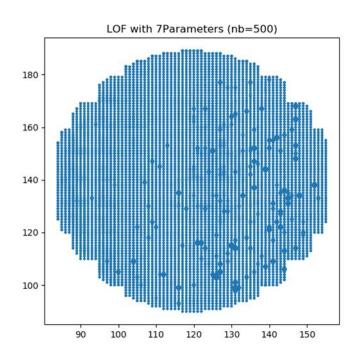

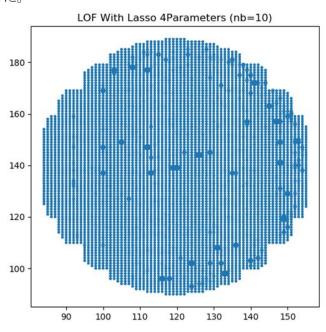

SVR による回帰結果はデータ数が少ないことと系がスムーズ(特異点がない)なため精度指標である Rsquare は 0.996 以上が得られた。最終的に平行線図上で結合するためにデータ数を増やす必要がある。説明変数を正規乱数を使用して 10000 個発生させた。説明変数の PairPlot を図 5-4-3.に示した。この 10000 組の説明変数に回帰精度 0.996 の SVR で 10000 個の回帰を 4 項目ごとに行いユニバーサルモデルを生成した[78]。

図 5-4-3. 正規乱数による 10000 組の説明変数生成

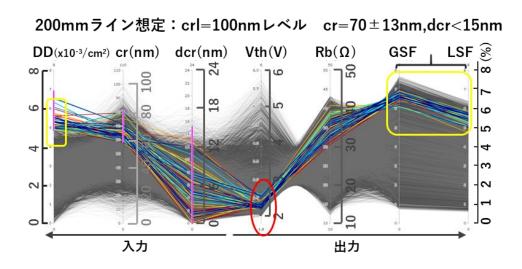

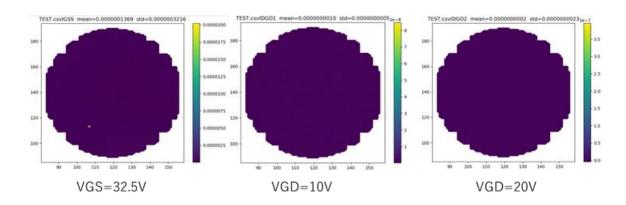

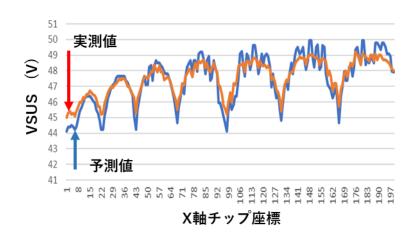

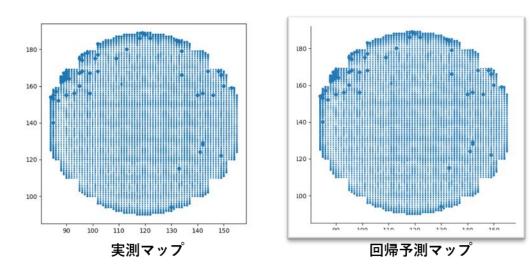

図 5-4-4.に 200mm ラインを想定して、欠陥レベルを 4.5</br>

DD<6.5x10<sup>-3</sup>(/cm²)、crl の加工バラツキを±13nm (実測値)、露光装置寸法変換差と合わせずれ dcr<15nm とした crl=100nm の FP-MOSFET (現レベル) について、Vth、Rb、GS 不良率、LS 不良率の平行線図を示した。Vth の分布上昇は 2.5V までで GS や LS 不良は  $6\sim7\%$ と予想された。

図 5-4-4. 200mm ライン想定 FP-MOSFET(crl=100nm)の特性・不良率

次世代の FP-MOSFET(crl=80nm)を 200mm 想定ラインで生産した場合の結果を図 5-4-5.に示した。Vth の分布上昇は 3.5V まで広がった。Vth の cr 依存性が大きくなっており 露光装置や加工装置の寸法制御性が限界にあることを示している。一方で、Rb は低くなり L 負荷耐量の絶対値は向上していることが判るが、電流アンバランスによっておこる LS 不良は 6%であり crl=100nm と比較して差はない。

図 5-4-5. 200mm ライン想定 FP-MOSFET(crl=80nm)の特性・不良率

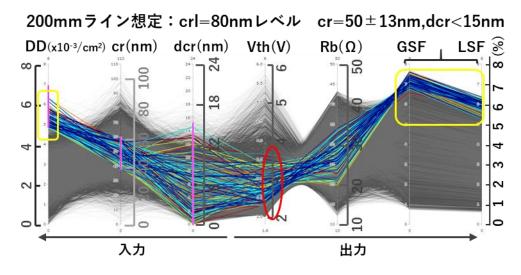

次に、300mm ラインを想定して、欠陥レベルを DD<1.0x10- $3(/cm^2)$ 、crl の加工バラツキを $\pm 5$ nm、露光装置寸法変換差と合わせずれ dcr<5nm とした crl=100nm の FP-MOSFET (現レベル) について、Vth、Rb、GS 不良率、LS 不良率の平行線図を図 5-4-6.に示した。Vth の分布上昇は最大で 2.2V までで軽微なレベルである。また GS や LS 不良は $\sim$ 1%であり量産適用可能なラインであることが予想された。

図 5-4-6. 300mm ライン想定 FP-MOSFET(crl=100nm)の特性・不良率

次世代の FP-MOSFET(crl=80nm)を 300mm 想定ラインで生産した場合の結果を図 5-4-7.に示した。Vth 分布はオフセット上昇が約 0.3V ありレンジで  $2.3\sim2.7V$ (センター値  $2.5V\pm0.2V$ )であった。Vth の cr 依存性が大きくなっており露光装置や加工装置の寸法制 御性が限界にあることを示している。GS 不良率や LS 不良率は<1.5%で crl=100nm と比較して大幅な増加ではない。crl=80nm は量産可能レベルと思われる。

図 5-4-7 300mm ライン想定 FP-MOSFET(crl=80nm)の特性・不良率

### 5-5. まとめ